# LabVIEW实时与FPGA助您快速构建 工业高确定性应用

### 议程

- 工业高确定性应用的解决方案

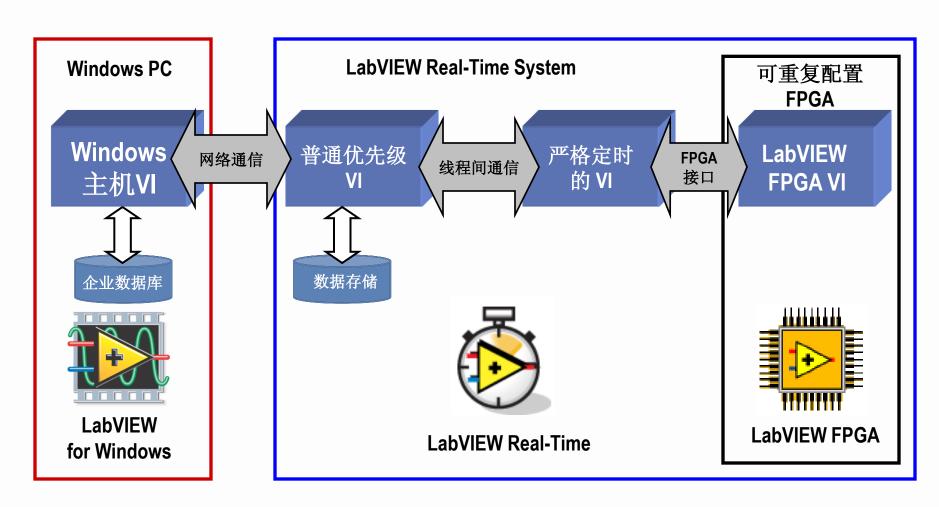

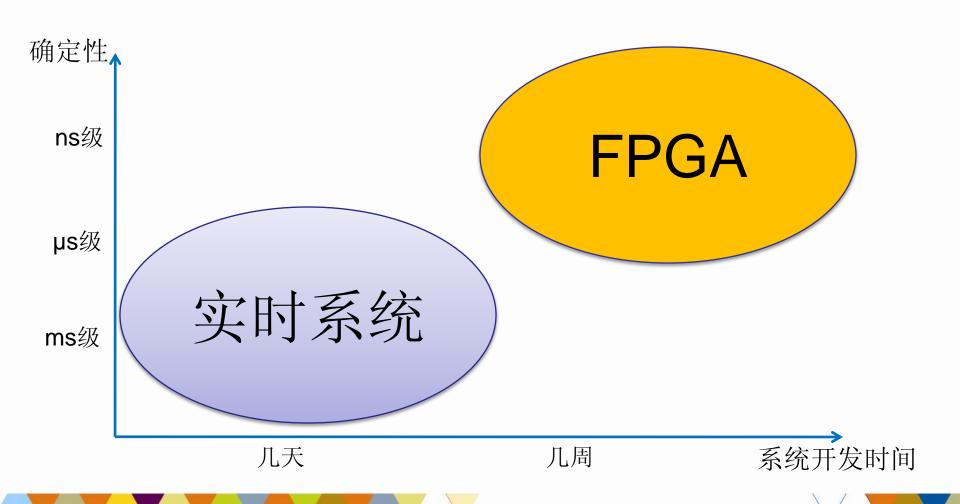

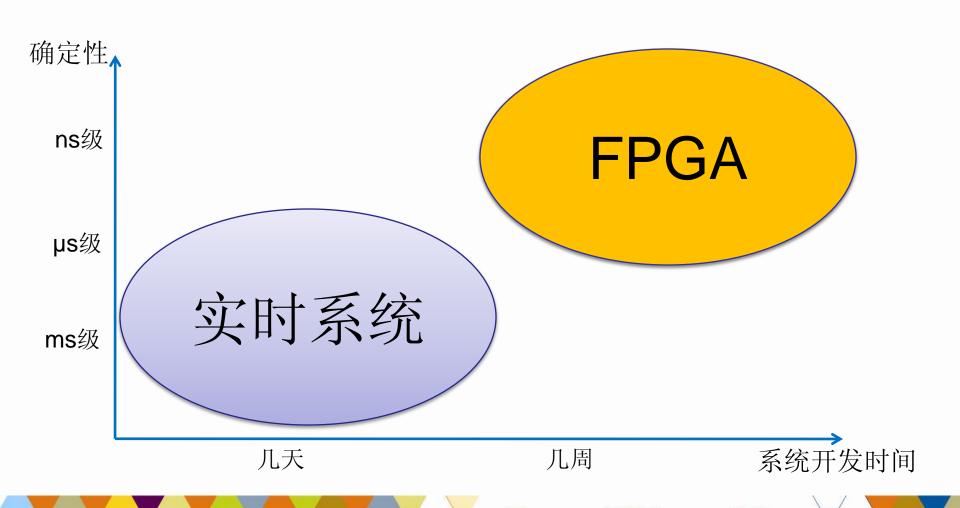

- 实时系统与FPGA

- NI提供全面的解决方案

- 快速开发实时应用

- 利用FPGA进一步提高确定性

- 小结

### 工业的高确定性应用

### 实时应用

- 实时:

- 在系统中有时间的约束,以防止事故的发生

- 确定性:

- 系统在确定的时间间隔内完成任务的时间

- · 普通操作系统循环速率: 100 Hz

- 实时操作系统循环速率: 50 kHz

#### 更高的实时性能——FPGA

- 高可靠性

- 在硬件上运行

- 高确定性

- 40 MHz的循环速率

- 完全并行的运行方式

- 可重配置

- 软件定义硬件程序

# FPGA技术原理 可编程的互连 逻辑块 Xilinx I/O块 FPGA芯片

### 高确定性的NI工业硬件平台

#### ——CompactRIO

#### 坚固可靠

- •-40~70° C温度范围

- 抗50g冲击, 5g振动

#### 低功耗

•9~35V DC供电, 7-10 W典型值

- •I/O 模块内置信号调理功能,可以直接连接传感器/激励

- ●可重新配置FPGA用于高速、自定义的I/O定时,触发和控制

- •实时处理器用于确定性的单机操作,数据记录和分析

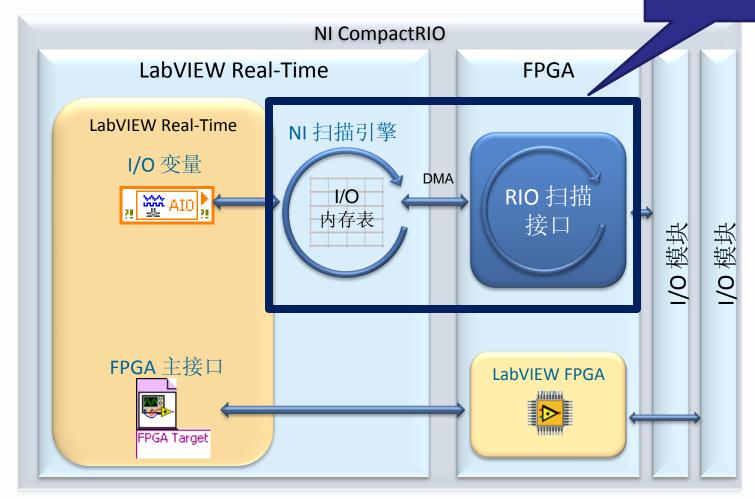

# LabVIEW下的CompactRIO软件开发框架

# NI CompactRIO为您提供全面的开发方案

NIDavs<sub>08</sub>

### 议程

- 工业高确定性应用的解决方案

- 实时系统与FPGA

- NI提供全面的解决方案

- 快速开发实时应用

- 利用FPGA进一步提高确定性

- 小结

#### 进一步简化的实时开发方式

- 实时系统开发的新工具

- 基于IEC-61131-3的工业控制函数

- 全新扫描模式与分布式系统管理器

#### IEC-61131-3函数功能块

- 遵循IEC-61131-3标准

- 专为实时控制应用而设计

- 能在Windows操作系统下运行

#### **Accumulate & Collect**

Σ Accumulate

Collect Boolean Array

Collect Numeric Array

| fdx | Totalize

#### Bistable/Flip-Flop

R<sub>₹</sub>D≻R S+D>

**RS** Bistable

R-25-5

SR Bistable

#### **Timing**

<sup>⊥</sup>→0 Count Down

O\$I Count Up

Count Up Down

Pulse Timer

Elapsed Time

Retentive Timer On

፲₄፲ Timer On Delay

Timer Off Delay

#### **Edge Detection**

Edge Detect

One Shot Rising

One Shot Falling

#### **Control**

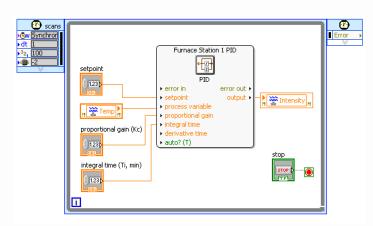

### 全新的扫描模式

- 无需编程直接显示I/O值

- 简单的模拟I/O

- 数字I/O: PWM波形, 高速计数器等

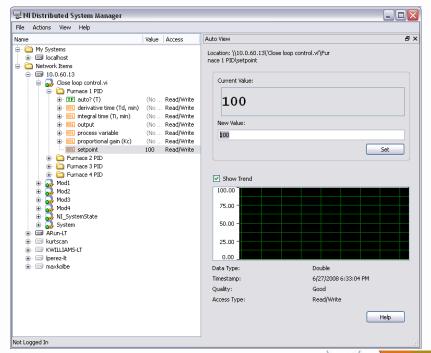

- 分布式系统管理器

- 测试面板功能

- I/O值强制输出

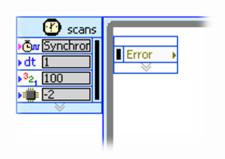

### 扫描模式工作原理

预先定义 无需编程

### 扫描模式下的I/O管理

- 扫描引擎的同步

- 定时循环

- While循环

• 调试程序时可强制改变I/O输出值

### 演示1: 扫描模式下的Ⅳ0管理

- 利用扫描模式创建和管理I/O

- 采集一个温度值

- 分布式系统管理器

- 强制改变I/O值

### 议程

- 工业高确定性应用的解决方案

- 实时系统与FPGA

- NI提供全面的解决方案

- 快速开发实时应用

- 利用FPGA进一步提高确定性

- 小结

# NI CompactRIO为您提供全面的开发方案

NIDavs<sub>08</sub>

### 采用FPGA进一步提高系统的确定性

- 难点:编写代码

- 解决方案: 采用现成的代码

- LabVIEW FPGA提供了频谱分析等工具

- CLIP Node助您集成第三方FPGA代码

- 难点:编译时间长

- 解决方案: 减少编译次数

- 利用软件仿真测试代码

- 在不同硬件上的代码复用加速系统开发流程

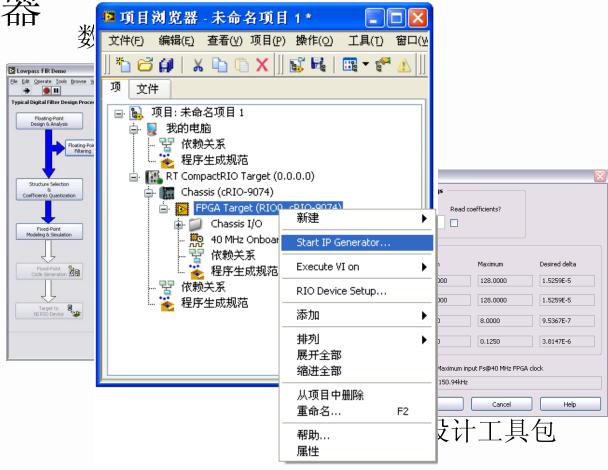

#### 1.采用现有IP降低代码开发的复杂性

- FPGA中的代码称为核(core)或知识产权(IP)

- 在LabVIEW中可以使用现成的IP减少开发时间

LabVIEW FPGA自带的分析工具

外部FPGA代码

#### LabVIEW FPGA中自带的IP

快速傅立叶变换(FFT)

重采样

窗函数

• IP生成器

- FPGA IPNET(<u>ni.com/ipnet</u>)

- NI FPGA IP的一站式资源中心

- 浏览、学习、下载IP资源

- 超过150个共享IP,资源不断更新

Math

Signal Processing

Data Manipulation and Transfer

RF and Communications

Digital Protocols

Data Acquisition

Signal Generation

Control

Sensor Simulation

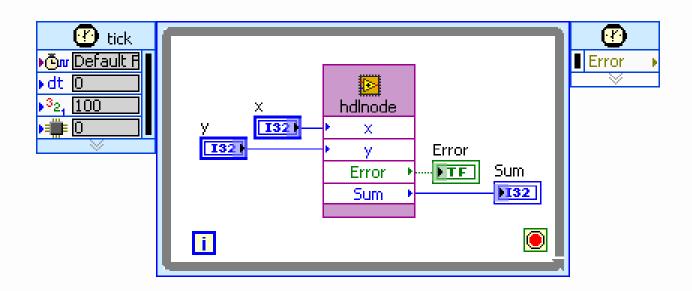

- HDL 节点

- 在您的程序中快速插入VHDL代码

- 需尊循LabVIEW FPGA编写逻辑,有时要修改代码

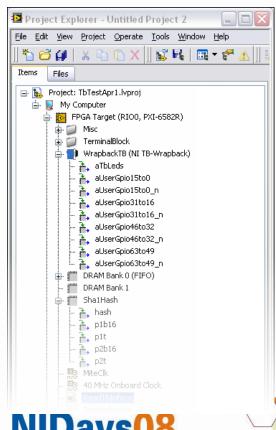

- CLIP(Component Level IP)节点

- 实现对于VHDL代码的完全支持,无需修改

- 并行执行

- 可以直接与硬件I/O通信

- 支持多时钟

#### 演示2: 在LabVIEW中使用CLIP节点

- 将现有的IP生成CLIP项

- 在LabVIEW中调用CLIP节点

```

Tablety ment the control of the cont

```

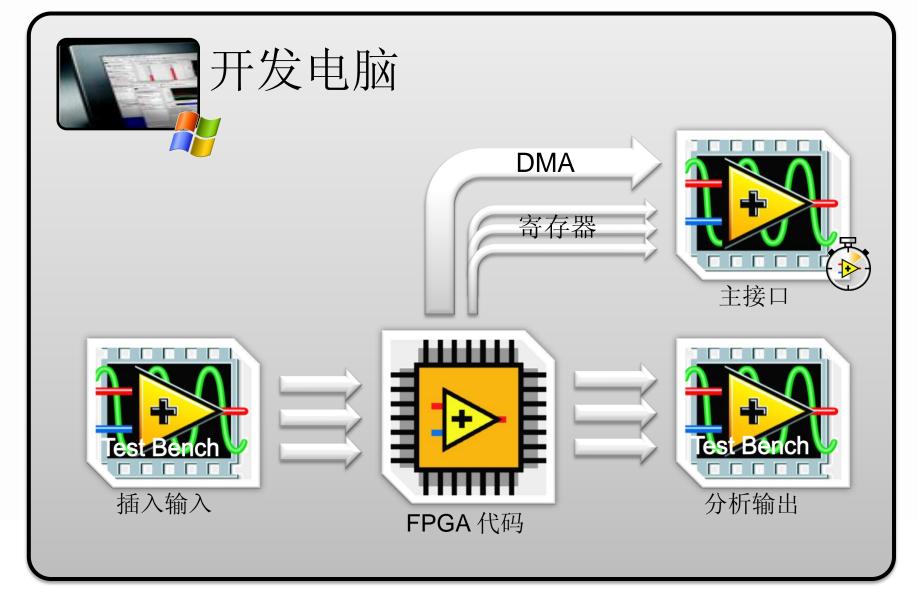

#### 2.在软件中仿真FPGA代码

#### 演示3: 在软件中仿真FPGA代码

- 采用软件仿真的方法减少编译次数

- 自定义仿真输入

- 实现仿真FPGA代码与主VI的通讯

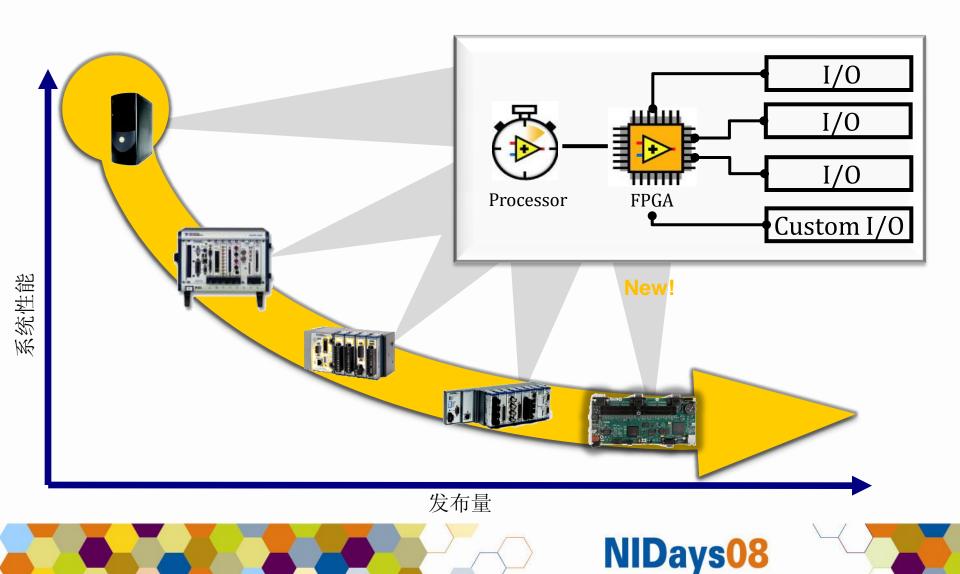

# 在不同的硬件上重用您的设计

#### 总结

· 在工业控制应用中使用实时系统和FPGA以获得更高的确定性

- NI CompactRIO为您提供全面的开发方案

- 扫描模式助您快速开发系统

- FPGA提供硬件级的确定性