# 高速数字电路设计教材

| yyyy-mm-dd | 日期: | <br>拟制: |

|------------|-----|---------|

| yyyy-mm-dd | 日期: | 审核:     |

| yyyy-mm-dd | 日期: | 审核:     |

| yyyy-mm-dd | 日期: | 批准:     |

# 华为技术有限公司

版权所有 侵权必究

# 目 录

| 第6章    | 专输线匹配           |

|--------|-----------------|

| 6.1 终站 | <b>耑匹配</b>      |

| 6.1.1  | 终端匹配的上升时间3      |

| 6.1.2  | 终端匹配的直流偏置5      |

| 6.1.3  | 其它拓扑形式的终端匹配8    |

|        | 终端匹配电路的功耗10     |

|        | <b>耑匹配</b>      |

|        | 始端匹配的阻值11       |

| 6.2.2  | 始端匹配的上升时间11     |

| 6.2.3  | 始端匹配较平坦的阶跃响应11  |

| 6.2.4  | 始端匹配的输出驱动电流11   |

|        | 始端匹配的其它拓扑形式12   |

|        | 始端匹配的功率消耗12     |

|        | <b>可匹配</b>      |

| 6.4.1  | 容性负载匹配的直流不平衡性14 |

| 6.4.2  | 差分线的终端匹配        |

| 6.5 电图 | 且阻值的选择15        |

|        | 匹配电阻的精确性        |

|        | 匹配电阻的功率消耗15     |

| 6.5.3  | 匹配电阻的电感         |

| 6.6 匹置 | 記电路的串扰          |

| 6.6.1  | 相邻轴向电阻间的串扰20    |

| 6.6.2  | 相邻贴片电阻间的串扰21    |

| 6.6.3  | 排阻间的串扰          |

# 第6章 传输线匹配

## 摘要:

系统何时需要匹配电阻?按照第四章的内容来看有两种情况:长线传输造成信号反射的情况 和短线传输造成信号振荡的情况。

传输线过长意味着线缆的长度已经超过了六分之一的信号波长,这时信号线必须匹配。如果不采取匹配,长线任一端的反射都能使信号无法传输。第四章第三节阐述了如何精确的确定信号反射的影响。4.3.5节提供了一种简单的数学方法,可以用来确定在一根没有匹配的电线上反射持续的时间。

传输线较短时,如果负载是容性的话仍然需要匹配。4.1节分析了负载是容性的高感应电路,让我们看到高O振荡的后果。短线上的振荡现象和长线上的反射现象具有相同的影响效果。

匹配可以解决振荡或反射的问题。

本章有三个主题:

- 终端匹配和始端匹配的比较;

- 选择合适的匹配电阻;

- 匹配器件间的串扰;

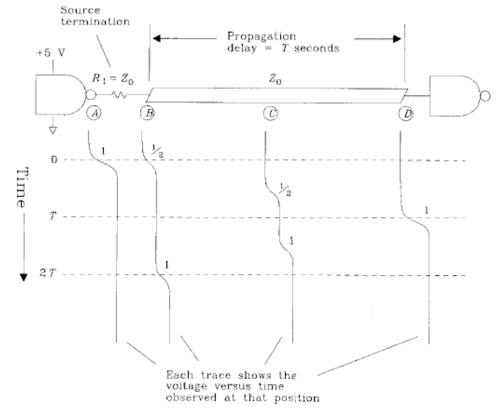

## 6.1 终端匹配

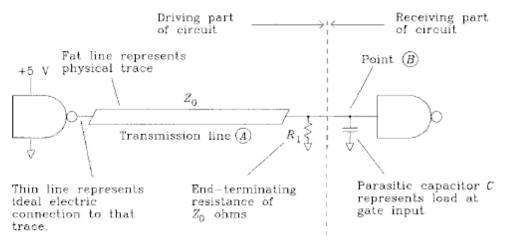

当使用终端匹配时,每一个驱动门直接和它的传输线相连,匹配电阻并在接收端(见图6.1)。 终端匹配传输线有以下这些特征:

- (1) 波形在整条线上都是以满强度传输的;

- (2) 所有的反射都被匹配电阻抑制了;

- (3) 接收端电压等于发射端电压。

#### 6.1.1 终端匹配的上升时间

我们可以通过直觉或更为详细的数学方法来推断终端匹配电路的上升时间。一般我们先用直觉的方法来推断然后用详细的数学方法来检验。

图6.1直接来看可以分为两部分。左边的部分即驱动部分由驱动门、传输线和匹配电阻组成。 我们可以把这一部分的驱动阻抗看作传输线的阻抗和匹配电阻的并联。从网络效果来看,在短时 间内相当于Z0/2的驱动阻抗。

Figure 6.1 Calculating the rise time of an end terminator.

右边的部分即接收部分只有一个接收门,在图6.1中其输入等效为一个电容。这种电容模型对于大多数CMOS、TTL、ECL的环境都是适用的。注意到这个电路就是简单的RC滤波电路,我们知道RC电路的时间常数:

$$RC$$

time constant =  $\frac{Z_0}{2}C$  [6.1]

利用3.1节的计算RC滤波器上升时间(10%--90%)的公式:

$$T_{\text{term}} = 2.2 \frac{Z_0}{2} C = 1.1 Z_0 C$$

[6.2]

假设有一输入信号上升沿时间为T1,我们结合匹配电路的Tterm来得出B点实际的上升时间为:

$$T_{\mathcal{B}} = \left(T_{\text{term}}^2 + T_1^2\right)^{\frac{1}{2}}$$

[6.3]

当传输线比上升沿要长时,它的输出阻抗实际上就是Z0。如果我们缩短传输线长度让它短到可以和上升沿相比时,传输线的阻抗从B点来看下降了。当传输线非常短时,B点的驱动阻抗与输出端的输出阻抗相等,在B点的上升沿将更快。

下边让我们用一种精确的数学方法来估算上升时间。回忆一下根据第四章里的模型推导出来的传输线全响应等式4.61:

$$S_{os}(w) = \frac{H_X(w)A(w)[R_2(w)+1]}{1 - R_2(w)R_1(w)H_X^2(w)}$$

[6.4]

如果传输线的长度超过了信号的波长,我们可以忽略任何来自终端的反射。这是合理的,因为在完成接收信号之前终端的反射信号没有时间反射回驱动端然后再返回接收端。或许会有延时的反射但不会影响初始的上升沿波形。从数学公式来看,如果想要得到零反射必需使反射因子 $R_1(W)$ 等于零。这样公式6.4就可以简化如下:

$$S_{\infty}(w) \approx H_X(w)A(w)[R_2(w)+1]$$

[6.5]

2001-08-16 版权所有,侵权必究 第4页, 共22页

为了进一步简化我们可以假设驱动阻抗与传输线的特征阻抗相比非常低,因而A(W)近似等于1。进一步还可以假设传输线的长度不足以分散信号,因而 $H_x(w)$ 的大小可以视为1。把这些简化一起考虑,上式可以简化为:

$$S_{oo}(w) \approx R_2(w) + 1 \tag{6.6}$$

把4.53式代入上式得:

$$S_{\infty}(w) \approx \frac{2Z_L(w)}{Z_L(w) + Z_0(w)} \approx \frac{2}{1 + \frac{Z_0(w)}{Z_L(w)}}$$

[6.7]

下边,把特征阻抗 $Z_0(W)$  视为常量 $Z_0$ ,同时注意到 $Z_L(W)$  是由匹配电阻(也等于 $Z_0$ )和一个电容并联而来,即:

$$\frac{1}{Z_L(w)} = \frac{1}{Z_0} + jwC$$

[6.8]

把此式代入6.7中得:

$$S_{\infty}(w) \approx \frac{2}{1 + Z_0 \left[ \left( \frac{1}{Z_0} \right) + jwC \right]}$$

[6.9]

$$=\frac{1}{1+jw\left[\left(\frac{Z_0}{2}\right)C\right]}$$

[6.10]

等式6.10是RC滤波器的响应,里面有时间常数因子Z0\*C/2。这证实了我们最初的模型。 终端匹配电路如果接容性负载的话上升时间是接同样负载的始端匹配电路的一半(请参见 6.2.2)。

# 6.1.2 终端匹配的直流偏置

图6.1中的电路很少应用于实际的TTL或CMOS电路中,这是因为当输出高电平时需要较大的驱动电流。当图6.1中的驱动门输出VCC时,它必须给终端电阻提供VCC/R1的电流;驱动门输出为低电平时,没有输出电流。假设我们使用一根特征阻抗为65欧的传输线,那么5伏驱动信号需要5/65=76毫安的电流,很少有驱动门可以输出如此大的电流。

就驱动能力而言,TTL输出低电平时需要的驱动电流要远大于输出高电平时的驱动电流; CMOS 则两种情况基本相同。

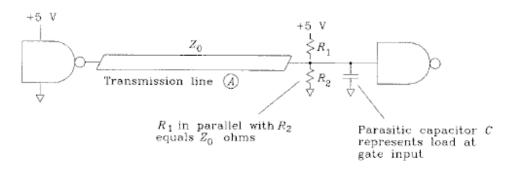

图6.2 是一种实际经常采用的匹配方法叫作SPLIT终端匹配。在这个电路中,R1并上R2的阻值等于Z0(传输线的特征阻抗)。R1和R2的比值控制着高低电平驱动电流的相对比例。图2.10提供了用于转变这种匹配为单电阻匹配形式的等式和等效电压源。

2001-08-16 版权所有,侵权必究 第5页,共22页

高速数字电路设计 内部公开

Figure 6.2 Split termination.

如果R1等于R2,高低电平驱动需要的电流是相等的。这种情况适用于HCMOS数字逻辑系列。如果R2大于R1,低电平驱动需要的电流大于高电平驱动需要的电流,这种情况适用于TTL和HCT系列。

R1和R2的大小选择最好采用图示的方法,选择时有三个约束条件:

- (1) R1和R2并联起来的阻值应等于Z0;

- (2) 输出电流不能大于IIOHMAX(高电平最大输出电流);

- (3) 输出电流不能大于 $I_{OLMAX}$ (低电平最大输出电流);

在下面的例子中我们对输出电流做如下的约定:流入驱动器的电流为正,流出驱动器的电流为负。TTL或CMOS输出低电平时为灌电流(为正)输出高电平时为拉电流(为负);ECL无论处于什么状态都是拉电流(为负)。

第(1)个约束条件很容易用允许范围来表示,用变量Y1、Y2分别表示满足条件的电阻R1和R2:

$$Y_1 = \frac{1}{R_1} \qquad Y_2 = \frac{1}{R_2} \tag{6.11}$$

我们先找出满足条件的Y1和Y2,然后再用Y1和Y2求出R1和R2,这样做的好处是可以把第(1)个约束条件表示为一个线性的等式:

$$Y_1 + Y_2 = \frac{1}{Z_0} \tag{6.12}$$

第(1)个约束条件可以用图6.3表示如下:

2001-08-16 版权所有,侵权必究 第6页,共22页

Figure 6.3 End-termination constraints.

在图上看这是一条斜线,所有满足约束条件的Y1和Y2的组合都在这条线上。

注意到流入驱动器的电流等于流过R2的电流减去流过R1的电流,由此可以得到第(2)个约束条件的一个等式。这两个电流的大小由VCC、VEE以及驱动器输出决定。一般的,我们用VCC代替较高的电压,用VEE代表较低的电压,这两个电压里常常有一个电压等于0。

约束条件(2)可以利用输出高电平时的驱动电压来计算:

$$(V_{CC} - V_{OH})Y_1 - (V_{OH} - V_{EE})Y_2 > I_{OH \text{ max}}$$

[6.13]

不等式的符号似乎应该是相反的方向,但并非如此。因为等式两边都是负数(因为驱动器常常输出电流)。不等式6.13需要实际的驱动电流要大于 $I_{OHMAX}$ 。不等式中 $I_{OHMAX}$ 的值应该是一个负值。

约束条件(3)可以利用输出低电平时的输出电压来计算:

$$(V_{CC} - V_{OL})Y_1 - (V_{OL} - V_{EE})Y_2 < I_{OL \text{ max}}.$$

[6.14]

$I_{OLMAX}$  的值对于TTL或CMOS来说是正值,对于ECL电路是0,因为ECL电路不吸收任何电流。

3种约束条件都表示在图6.3中,用74HC11000与非门来计算。输出电压和电流的限制都是假设在5.5伏电压供电的情况下来计算的,这通常是最坏的一种情况。条件(1)出现了两次,一次用来计算特征阻抗是65欧的情况,另一次是100欧。100欧对应的直线可以经过同时满足两种电流约束条件的区域,在(Y1=0.05,Y2=0.05)这个点上,对应的阻值是: R1=200欧; R2=200欧。

65欧电阻对应的直线没有经过任何同时满足两种电流约束条件的区域,因此不存在实际工作的SPLIT匹配电阻的组合,74HC11000不能驱动终端匹配电阻为65欧的传输线。

2001-08-16 版权所有,侵权必究 第7页,共22页

有时侯仅用一个电阻来进行终端匹配,这时候需要为匹配电路单独提供一个固定的电压。上面的过程对于找寻一个合适的匹配电压也是有效的。

首先设计一个SPLIT匹配网络,然后把此网络转换为等效电压源。等效电压源的阻抗是Z₀,输出电压是:

$$V_{\text{terminate}} = \frac{R_1 V_{EE} + R_2 V_{CC}}{R_1 + R_2}$$

[6.15]

可以把这个值作为匹配电压。

#### 6.1.3 其它拓扑形式的终端匹配

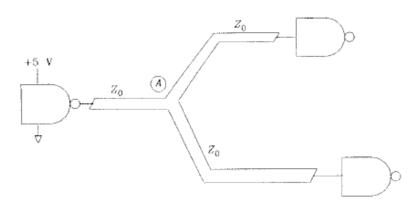

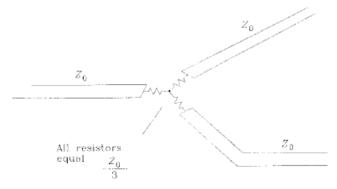

图6.4中的两根分支线很难正确匹配。无论我们在哪里放置匹配电阻,驱动器输出的信号都要反射回节点A,引起振铃。

Figure 6.4 Bifurcated line.

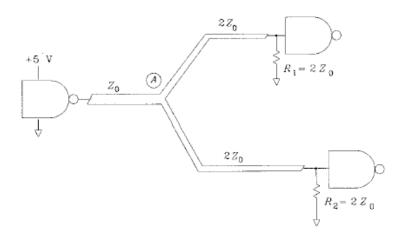

图6.5中的两根分支线可以正确匹配。在图6.5中每个分支线的特征阻抗都等于2Z<sub>0</sub>。只要使分支线比主线细就可以实现这个电路。在每一个分支线的终端都有一个阻值为2Z0的电阻。从A点来看每一条分支线的输入阻抗都是2Z<sub>0</sub>,这样特征阻抗为Z<sub>0</sub>的主线就可以和两条并联的分支线匹配。但是几乎没有系统采用这种技术,因为在电路板上分支线的阻抗是变化很大的。

采用终端匹配后,以前沿着传输线传输的反射信号停止了,没有任何反射发生。

Figure 6.5 Bifurcated line with matching trace impedances.

2001-08-16 版权所有,侵权必究 第8页,共22页

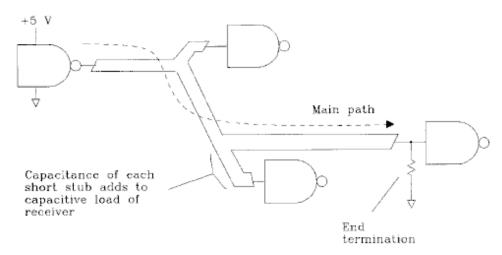

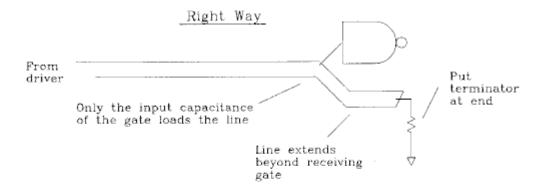

对于终端匹配的传输线因为输入信号的延时再现在线上任一点都会出现,因此我们可以把接收器放在线上的任一点。这种配置被称为菊花链。图6.6中的每一个接收器都可以收到延时后的输入。

Figure 6.6 Daisy-chain configuration with end termination.

保持STUB线足够短(相比上升时间)有助于减少分支点的反射。短的STUB线(以及与之相连的接收器的等效输入电容)就象一个4.4.2节里描述的简单的电容负载一样,可以减少信号的上升时间。如果STUB线均匀分布,4.4.3节的近似值也还是成立的。

理想的终端匹配形式是把匹配电阻放在最后一个接收器之后,没有任何分支和STUB。(参见图6.7)

Figure 6.7 Detail of an ideal end-terminator placement.

2001-08-16 版权所有,侵权必究 第9页,共22页

高速数字电路设计 内部公开

#### 6.1.4 终端匹配电路的功耗

终端匹配电路的功耗是高电平和低电平电压以及电源供电电压和负载阻抗的函数。负载功耗与匹配电阻的大小成 反比,因而传输线阻抗越高,终端匹配的功耗越小。

关于驱动电路中功率消耗的等式可以参见第2.2.6节。图6.3中负载电阻总的功耗可以用式6.16计算(假设输出高电平和输出低电平的时间相等):

$$P_{\text{load}} = \frac{\left(V_{\text{HI}} - V_{EE}\right)^2 + \left(V_{\text{LO}} - V_{EE}\right)^2}{2R_2} + \frac{\left(V_{CC} - V_{\text{HI}}\right)^2 + \left(V_{CC} - V_{\text{LO}}\right)^2}{2R_1}$$

[6.16]

# 本节要点:

- 驱动同样的容性负载,终端匹配电路的上升时间只有始端匹配电路的一半;

- 大部分的CMOS和TTL电路没有足够的驱动电流驱动终端匹配电路;

- 终端匹配电路的接收器可以以菊花链的形式连接。

#### 6.2 始端匹配

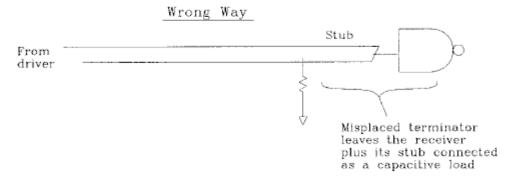

始端匹配电路中的驱动器通过串联的电阻和传输线相连。这个电阻的阻值加上驱动器的输出阻抗应该等于传输线的特征阻抗Z<sub>0</sub>。这样源端的反射系数就等于零。参见图6.8。

Figure 6.8 Source-terminated line.

始端匹配电路有以下特征:

- 1. 输出波形在经过串联电阻后的强度只有原来的一半;

- 2.传到传输线终端的信号强度只有原始信号的一半;

3.在传输线的终端(开路的情况下)信号的反射系数是+1。反射信号的强度也是原始信号的一半。一半的反射信号和原始输出的一半信号相加形成传输线终端的信号电平。

- 4.反射信号(原始信号强度的一半)沿着传输线往源端回传,到达匹配电阻后被抑制。

- 5.终端反射回来的信号到达源端后,输出电流降到零直到下次传送开始。在一些高速系统中, 在反射回到源端之前下一次传输就已经开始了。

#### 6.2.1 始端匹配的阻值

一个理想的驱动器的输出阻抗是0。实际的驱动器的输出电阻也都很小。ECL电路的高电平和低电平的输出阻抗都是10欧左右。当设计一个始端匹配的电路时,必须考虑驱动器的输出阻抗使驱动器输出阻抗加上匹配电阻的阻值与线路的阻值相匹配。因此源端匹配电路的匹配电阻的阻值小于线路的特征阻抗。

TTL和CMOS电路在输出高电平和低电平时的输出阻抗不同(参见例2.1)。因而对于TTL和CMOS电路没有完全合适的阻值来进行始端的匹配,只能取一个折衷的值。

#### 6.2.2 始端匹配的上升时间

始端匹配电路中传输线上任一点往源端看的话,驱动器的输出阻抗都是Z0。当驱动一个容性负载的话,我们可以得到一个类似简单RC低通滤波电路的响应,RC时间常数是:

$$RC$$

time constant =  $Z_0C$  [6.17]

利用3.1节中的公式可以计算出RC滤波器的(10%-90%)上升时间:

$$T_{10-90} = 2.2Z_0C ag{6.18}$$

这个时间是同样传输线阻抗和同样负载情况下终端匹配电路上升时间的两倍。

#### 6.2.3 始端匹配较平坦的阶跃响应

在一个典型的数字电路中在传输线的起始端减小反射要比在终端减小反射容易。起始端有输出阻抗(还有感应系数)。另一方面,终端的接收器常常有寄生电容。在终端匹配电路中这种由于电容负载而引起的不匹配效应的情况比在始端匹配电路中由于驱动感应系数而不匹配的情况要糟得多,尤其在驱动多个负载的时候。始端匹配的反射系数比终端匹配电路的反射系数要更接近于0,因而它具有更为平坦的全频率响应。

估算出哪种电路形式更适合于你的逻辑器件是很有意义的。

#### 6.2.4 始端匹配的输出驱动电流

始端匹配传输线的复合输入阻抗既包括传输线的特征阻抗 $Z_0$ 又包括匹配电阻的阻值。它们的和接近于特征阻抗的二倍。最坏情况下的输出电流是 $\Delta V/2Z0$ 。这种状态持续的时间只有信号在电缆上传输一个来回的时间,此后输出电流变为0。对于始端匹配由于信号倒换很少,因而平均的驱动输出电流是很小的,虽然峰值电流是 $\Delta V/2Z0$ 。

与通常的认识相反,终端匹配的传输线不比始端匹配的传输线更难驱动。如果把终端匹配的偏置设为逻辑电平的中间点,终端匹配电路的最大输出电流与始端匹配电路一样。终端匹配传输线的输入阻抗只有始端匹配电路的一半,即 $\mathbf{Z}_0$ 。但输出和偏置之间的电压峰值只有输出电压的一半,因而最大输出电流也是 $\Delta V/2\mathbf{Z}0$ 。

2001-08-16 版权所有,侵权必究 第11页,共22页

高速数字电路设计 内部公开

但是请注意如果使终端匹配的偏置点偏离中间点,一个方向上电流增大;一个方向电流减小。而对于始端匹配电路则没有这个问题。

虽然两种电路所需要的最大电流相同,但在信号慢速变化的情况下,始端匹配的平均驱动电流要小一些。在快速电路的情况下,在信号反射回来之前下一个信号已经到来,此时的驱动电流峰值时间要长一些。

#### 6.2.5 始端匹配的其它拓扑形式

菊花链的拓扑形式在始端匹配电路里是不能使用的。所有的负载必须全部接在传输线的终端。一个连在线路中间的负载其上的波形如图6.8的C点。

#### 6.2.6 始端匹配的功率消耗

第2.2.6节中的方法对于估算此情况下的驱动电路的功耗效果不好,这是因为输入负载的电流 在信号传输一个来回延迟2T后变为0,我们必须找出更好的模型。

在驱动器输出一个信号到信号反射回起始端的这段时间里,匹配电阻上的电压为 $\Delta V/2$ 。在这端时间里电阻上总的功耗为:

$$E = 2T \left(\frac{\Delta V}{2}\right)^2 \frac{1}{R} \tag{6.19}$$

$\Delta V$  = 高低电平间的压差,单位V;

T = 信号沿传输线的单向传输时间,单位s;

2T = 信号在传输线上一个来回的时间,单位s;

R = 始端匹配电阻,单位欧。

把每一个脉冲期间所消耗的功耗加起来可以粗略的估计电路的功率。这种方法只在脉冲持续时间比信号在传输线上走一个来回的时间长时才有效,如果脉冲持续时间很短,只能假设电路始终工作在最坏的情况下即 $\Delta V/2$ 一直通过电阻R:

Power

$$\approx \frac{\text{(Pulse frequency)}T \Delta V^2}{2R}$$

[6.20]

$\Delta V$ = 高低电平间的压差,单位V;

T = 信号沿传输线的单向传输时间,单位s:

R = 始端匹配电阻,单位欧。

在同样的条件下, 始端匹配的功耗要比终端匹配的小。

#### 本节要点:

- 始端匹配的上升沿较缓,其残留的反射比终端匹配电路小。

- 不能用菊花链的形式来连接始端匹配电路。

- 从理想的始端匹配阻值减去驱动器的输出阻抗才是正确的匹配电阻值。

- 信号频率较低时消耗的功率较小。

- 始端匹配的电路和终端匹配电路的峰值电流相等。

#### 6.3 中间匹配

2001-08-16 版权所有,侵权必究 第12页,共22页

有时候工程师把很多电路连到一起但并不考虑匹配,而信号可能已经具备了匹配的条件。这 在三态驱动器的情况下更为严重,因为不能准确定义源端和终端。

直觉告诉我们每一次传输在稳定下来之前都要在传输线上震荡一段时间。4.3.5节提供了一种快速的方法来估算一段直线上的这段时间。在器件间连线比较复杂的情况下,这段时间至少是最长的那根分支连线上的稳定时间。

如果这个网络中的一个器件需要陡峭的上升沿的话,就比较麻烦。通常情况下没有办法来解决这个问题,因为缺少使上升沿变陡的方法(另外也无法对接收信号加有效的滤波)。

如果输入电路能够及时采样的话,我们可以把采样的时间安排在网络上每一次传输稳定以 后。这时,我们只需减少传输稳定的建立时间,不过是没法完全消除的。

至少有四种方法可以解决这个问题:

- (1) 为每一个驱动器都加上始端的匹配。

- (2) 为每一个接收器都加上终端的匹配。

- (3) 在网络的中间加一个SHUNT匹配。

- (4) 在所有的支路节点之间串入电阻。

- 第(1)种方法有明确的定义,消耗的功率也比较小,可以提供一点衰减。同时可以减少信号建立的时间。

- 第(2)种方法需要较大的驱动功率但是只适合于星型的电路。星型的电路中有很多布线,它们的一端各自连接一个电路,另一端连在一起。反射被局限于中间节点和发送端之间。

把以上两种方法结合起来,虽然功耗稍大但对于星型的网络是一个不错的解决方法。但是所有的信号经过中间节点后强度被削弱了。虽然没有了反射但接收到的信号电平非常小。

我们不知道人们为什么使用方法(3)。它只能使网络的中心阻抗变的更低而这个阻抗本身就已经非常低了。

方法(4)在每一个节点都对信号有衰减。利用图6.9中的电路可以看出信号经过一个节点就会被衰减一半。这样的电路使反射的衰减非常快(反射信号一个来回后就只有原来的1/4),但当信号经过很多节点以后的衰减也非常严重。因而这样的电路中串联的节点数不能超过3个,只有这样才能保证接收器的接收灵敏度可以容忍信号的衰减。

Figure 6.9 Attenuating juncture for hair ball networks.

# 本节要点:

中间匹配是以信号的衰减为代价提高系统的阶跃响应性能。

#### 6.4 终端匹配的交流偏置

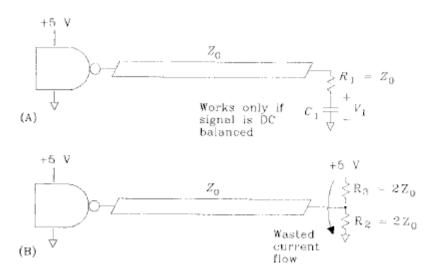

我们有时候在终端匹配电路里用电容来减小电源的静态功耗。考虑图6.10中的两个电路。与信号时钟周期相比所选的时间常数 $R_1$ C是非常大的。

如果我们能够保证驱动电路处于高电平的时间等于低电平的时间(我们称这样的电路为直流补偿电路),那么电容C1上的平均电压将为高电平电压和低电平电压的中间值。电阻R1上的平均电压大小为 $\Delta V/2$ 。R1消耗的功率为:

$$P_{R_1} = \frac{(\Delta V/2)^2}{Z_0} = \frac{(\Delta V)^2}{4Z_0}$$

[6.21]

$\Delta V$  = 高低电平之间的压差,单位V;

Z<sub>0</sub> = 匹配电阻值,单位欧。

作为对比,在SPLIT匹配的电路中两个电阻上的平均电压均为 $\Delta V$ ,但每一个电阻的阻值是2Z0,因而电阻上消耗的功率是:

$$P_{R2+R3} = \frac{(\Delta V)^2}{2Z_0} \tag{6.22}$$

等式6.22 中的值是6.21中的两倍。多出的那部分功耗是R2和R3的直流功耗。

从驱动电路的角度来看以上两种匹配电路是一样的,因为驱动电路的输出功率是相同的,只 有电阻消耗的功率不同。

#### 6.4.1 容性负载匹配的直流不平衡性

如果图6.10A中电路输出停留在高电平的时间过长,电容两端的电压将被充电到高电平电压值,当输出变为低电平时,全部的 $\Delta V$ 电压将被加在电阻R1的两端。此时的输出电流是直流补偿状态下输出电流的两倍。

如果驱动器不能输出如此大的电流的话,我们必须保证信号是直流平衡的以保证容性匹配电路可以正常工作。

有时候设计者采用折衷的方法,让C1的容量减小以保证时间常数R1C1足够短。他们期望C1要足够大来保证衰减反射同时又足够小来减轻驱动器的双倍电流输出。

#### 6.4.2 差分线的终端匹配

2001-08-16 版权所有,侵权必究 第14页, 共22页

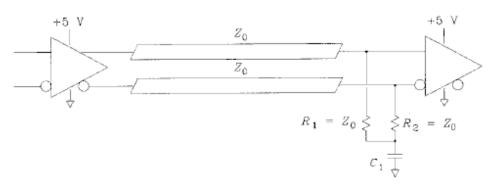

如果两个信号是差分信号,我们可以把它们的匹配电阻接在一个电容上。这样的终端匹配电路既能节省功耗又能保证C1上电压的准确性。参见图6.11。

Figure 6.11 Termination of a differential pair.

# 本节要点:

• RC电路可以匹配直流补偿的情况下的传输线,并且没有静态功耗。

#### 6.5 电阻阻值的选择

#### 6.5.1 匹配电阻的精确性

终端匹配的电阻应该能减小或消除不希望的反射。这必须满足匹配电阻与传输线的特征阻抗 相等才能实现。

在考虑不匹配的最坏情况时必须同时考虑阻值的不确定性和传输线特征阻抗的不确定性。总的结果除以2来找出期望的反射百分比(式4.5.3的结果)。传输线特征阻抗往往比电阻的阻值更加不确定。例如我们都知道传输线的阻值范围在±10%之内而电阻的阻值都在±1%之内。

如果信号的保真度是最重要的话,可以考虑同时使用终端和源端的匹配。这种情况下接收到的信号电平减半但是显著的减小了反射。任何反射信号都必须在始端和终端之间传输同时使有效 反射系数保持一致。无论对终端匹配还是始端匹配的要求都放宽了。这种方法在微波电路中应用 比较广泛,主要用于在宽的频带内实现增益的平坦。在数字电路中这种双匹配技术仅仅当线路接收器可以区别接收削弱的信号的情况下才使用。

#### 6.5.2 匹配电阻的功率消耗

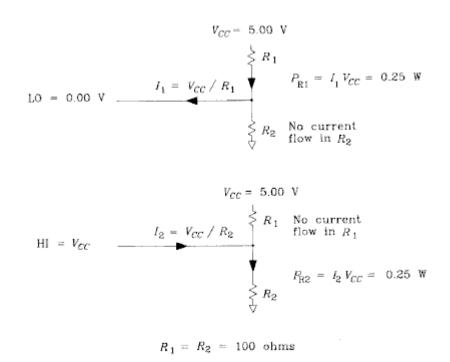

不考虑工作速度的话,通常对所有的匹配电阻分别计算来估算出最坏情况下各个电阻的功耗。在计算这个功耗时不要假设你的电路工作在50%的占空比。

例如,图6.12中的匹配电阻在最坏情况下所消耗的功率为:

$$P_{\text{worst}} = \frac{(5 \text{ V})^2}{100 \Omega} = 0.25 \text{ W}$$

[6.23]

在这种应用中标准的1/8瓦的电阻在室温下会过热,1/4瓦的电阻在环境温度稍高的情况下也会过热。可以向制造商确认电阻在功率为1/4瓦的情况下且可能的最高环境温度下能否安全的工作。 很多电阻的功率控制能力在过高的环境温度下会下降。

请按照制造商提供的安装和散热指导来设计。电阻体存在一个热阻,导致每瓦特会有几个摄 氏度的温度升高。相比集成电路,电阻能容忍更高的工作环境,尤其是陶瓷电阻。

2001-08-16 版权所有,侵权必究 第15页,共22页

Figure 6.12 Power calculation for split termination with the worst-case LO or HI signal.

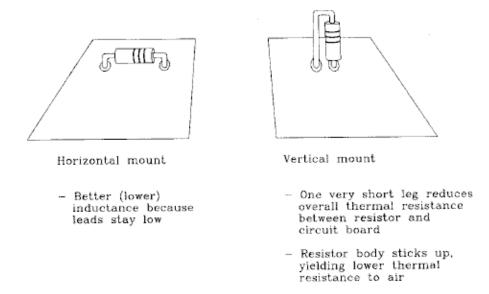

与集成电路不同,电阻有两种贴装方式。图6.13中垂直安装的电阻在没有空气流通的情况下散 热要好于水平安装的电阻。

电阻过热的直接后果是引起阻值的漂移,从而引起反射。在极端的情况下电阻已经破裂,你 精心设计的匹配电路根本就不存在了。

Figure 6.13 Two ways to mount axial resistors.

#### 6.5.3 匹配电阻的电感

2001-08-16 版权所有,侵权必究 第16页,共22页

假设你已经选好了电阻值、承受能力、额定功率,下一步最重要的一个因素是寄生电感。所有的电阻都有寄生电感。其大小依赖于电阻的内部结构、外部导线类型以及安装方式。印刷电路板上与匹配电阻串联的导线的电感必须作为电阻电感的一部分。

电感所造成的影响与工作的频率有关。对于数字信号,我们在工作频率是KNEE频率的情况下分析电感的影响(见式1.1)。利用等式1.1可以把上升时间和频率联系起来,我们可以直接利用上升时间来计算感抗的大小。

$$\left|X(T_r)\right| = \frac{\pi L}{T_r} \tag{6.24}$$

Tr = 信号上升时间,单位s;

|X(Tr)| =上升沿Tr所对应的感抗的大小,单位s;

L = 电感,单位H。

寄生电感引起的不匹配如同匹配电阻阻值不准引起的失配一样。把感应电阻的阻值表示为匹配电阻阻值的百分比形式,每1%的感应阻值对应1/2%的反射。当X(Tr)的绝对值等于10%的匹配电阻值时对应的反射是5%。

表6.1列出了三种不同电阻的实验室测量结果。前两种是2.2欧轴向碳膜电阻。最后的一个是表面帖0欧电阻,0.12英寸长0.06英寸宽。较大的1/4瓦轴向电阻的电感比1/8瓦的要大。

这些测量受导线长度的影响比较大。对于表6.1,所有的轴向电阻都是水平贴装而且引线都是 尽可能靠近电阻的接线端并连接牢固。

TABLE 6.1 TYPICAL SERIES INDUCTANCE OF RESISTORS

| Series inductance (nH) |

|------------------------|

| 2.5                    |

| 1.0                    |

| 0.9                    |

|                        |

#### 例6.1: 匹配电阻的电感影响

让我们用1/8瓦的轴向电阻来匹配数字信号信号,此信号的上升时间或下降时间是1ns。

信号的上升时间或下降时间

1ns

传输线特殊阻抗

50欧

电阻的感抗

1nH

我们采用100欧电阻来进行SPLIT匹配。在这种配置中,感抗和阻抗的比值对两个电阻来说是一样的。对于一般的SPLIT匹配,只需用感抗大小和两个电阻中较小的一个电阻的比值来计算出感抗的大小:

$$|X(T_r)| = \frac{\pi(1 \text{ nH})}{1 \text{ ns}} = 3.14$$

[6.25]

找出感抗和阻值之间的比例:

$$\frac{|X(T_r)|}{100 \ \Omega} = 3.14\% \tag{6.26}$$

2001-08-16 版权所有,侵权必究 第17页,共22页

这里电感的反射为1.5%。

在例6.1中的SPLIT匹配把原来的反射减小一半,与单50欧电阻匹配相比有着相同的电感。把电阻并联通常是一种减小电感的好方法。

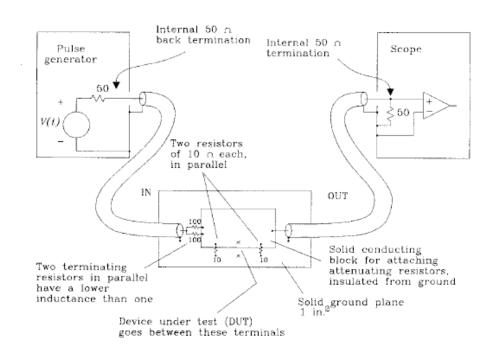

表6.1中的电感测量的具体方法如图6.14。这个JIG的输出阻抗为4.3欧,源波形是步进的波形。 当测试一个纯电感时,我们期望从这个JIG测出感应的峰值信号,它的总面积等于:

Spike area =

$$\frac{L}{R_s} \Delta V$$

[6.27]

$\Delta V$  = 电压步进值,单位V;

L = 测试时的电感,单位H;

Rs = 测试JIG的输出阻抗,单位欧。

当测试纯电阻时,我们期望测量一个步进输出,其最终值为:

Final value =

$$\frac{R_1 \Delta V}{R_1 + R_S}$$

[6.28]

R1 = 测试时的阻抗,单位欧

Rs = 测试JIG的输出阻抗,单位欧。

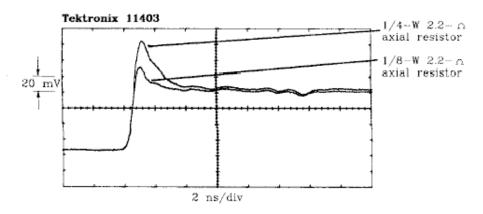

当测试一个未知的电阻和电感的混合体(比如一个实际的电阻),我们期望看到输出是电阻引起的步进波形和电感引起的尖峰波形的叠加。步进和尖峰波形都画在图6.15中。

当分析输出时,首先找出已知的测试JIG的输出阻抗和输出的终值。然后用直流电阻计测出其电阻。知道了被测电阻的阻值,我们可以画出测试电路在纯电阻情况下的输出波形。然后在实际的波形中减去这个理想的波形剩下的就是纯电感部分的尖峰波形。

然后我们可以用式6.29来算出纯电感的值,式6.29与式6.27很相似,只是多了一个测试电阻的自身电阻值。

2001-08-16 版权所有,侵权必究 第18页,共22页

- All resistors are 1/8 W.

- Run coax probes in from opposite sides to reduce direct feed-through.

- Ground DUT test point to check for feed-through.

- This test jig has a source impedance of 4.34 n, and an attenuation factor of 23:1.

Figure 6.14 A 4.3- $\Omega$  lab setup for measuring the inductance of resistor packages.

Figure 6.15 Output of a 4.3- $\Omega$  test setup for 1/4- and 1/8-W resistor bodies.

$$L = (\text{spike area}) \frac{R_1 + R_S}{\Delta V}$$

[6.29]

L = 测试时的电感,单位H;

R1 = 测试时的阻抗,单位欧;

Rs = 测试JIG的输出阻抗,单位欧。

从实际的测试波形去掉那部分理论上的波形时利用测试JIG的开路输出波形而不是规则的步进 波形,这一点很重要。因为测量设备的带宽有限,理想的波形占有的面积和实际测出波形之间的 差异会引入误差。

你可以把输出的波形存储起来,设好比例,然后从实际的波形中减去它,使用诸如Tektronix 14000系列的数字示波器就可以很容易的测出结果。

在这个实验中用尽可能小的电阻。对于一个固定的电感,测出的SPIKE面积与电阻成反比。这使得SPIKE在阻值很大时很难观测。

必须知道一些金属膜电阻是通过在金属膜上蜿蜒蚀刻而获得高的电阻值的。与低值电阻相比,高值电阻有时候明显具有更高的电感。电阻值在10-100欧之间的电阻往往都有相同的物理结构。

# 本节要点:

- 选用匹配电阻时要注意阻值的准确和额定功率。

- 电阻的寄生电感可以引起不想要的反射。

#### 6.6 匹配电路的串扰

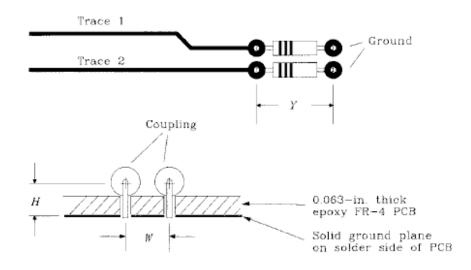

图6.16中的两个相邻的匹配电路的信号通过传输线交叉耦合。这种互扰比相邻传输线的串扰更为严重。

2001-08-16 版权所有,侵权必究 第19页,共22页

这一节中提供了一些匹配电路交叉耦合的测量结果和一些启发性的东西用来预见匹配电路中的串扰。

End View of Layout

Figure 6.16 Configuration of terminating resistors.

匹配电路中的串扰来自互感和耦合电容。互感的作用更大一些。我们只需找出一个总的系数 来反映串扰而不关心是互感还是电容耦合的作用更大。

Noise voltage =

$$\frac{K}{R} \frac{\Delta V}{T_{10-90}}$$

[6.30]

Noise voltage = 在走线2上的干扰锋值;

K = 交叉耦合系数,单位欧-秒;

R = 阻抗, 单位欧;

$\Delta V$  = 驱动电压步进值,单位V;

$T_{10-90} = 驱动信号上升时间,单位s。$

### 6.6.1 相邻轴向电阻间的串扰

在相邻过孔的匹配电阻之间的互感串扰通常遵循式6.30中的规则。我们可以利用它来大致估计交叉耦合系数:

$$K = (5.08 \times 10^{-9})Y \frac{1}{1 + (W/H)^2}$$

[6.31]

当我们将步进信号加在布线1上时在布线2上的耦合噪声电压为脉冲信号。

Y = 过孔之间的电阻的长度,单位in.;

H = 地层之上的中心线的高度,单位in.;

W=电阻中心线之间的距离,单位in.;

K = 交叉耦合系数。

2001-08-16 版权所有,侵权必究 第20页,共22页

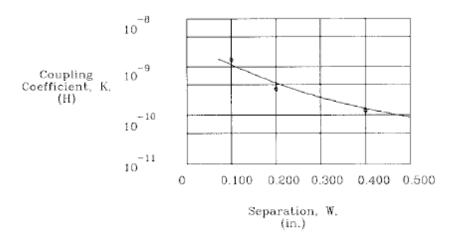

图6.17中绘出了K的几个测量值和计算值。测量值(图中的点)是通过测量几个样品的实际串 扰然后用6.30推出来的K值。计算值(图中的实线)是用式6.31在长度为0.400宽为0.108(与实际被 测样品相同)条件下计算出来的。它们之间是不同的。

Same layout as in Figure 6.16 1/4-W resistor bodies Body length, 0.400 in.

Centerline height above surface of board

Distance, surface of board to ground

Total centerline height

0.045 in.

0.063 in.

Figure 6.17 Measured and calculated values for the coupling coefficient between two terminating resistors.

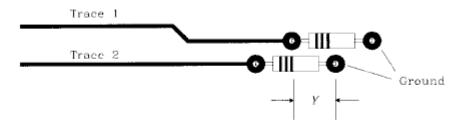

如果象图6.18中那样把电阻错开,然后用新的重叠长度代入6.31计算一下。

Figure 6.18 Staggered terminating resistors showing overlap length (parameter Y.)

#### 6.6.2 相邻贴片电阻间的串扰

表面贴的电阻由于能够更加靠近印制板,因而它表现出比轴向器件低得多的串扰系数。为了把它的这个特性发挥到极至,可以在此电阻的下面接近于电路板外层的地方铺设接地层。这减小了6.31中的H参数,降低了串扰。

#### 6.6.3 排阻间的串扰

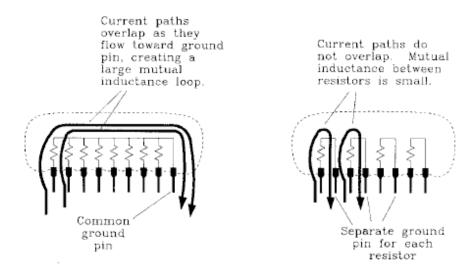

这些器件可以工作的很好或者很坏,这取决于它的内部走线。图6.19中画出了单端接地设计时 匹配电阻间的公共电流回路,这个公共回路引入了很强的互感。

Figure 6.19 Two styles of SIP terminating resistors.

表6.2列出了0.1英寸SIP封装的排阻的典型串扰系数。SIP-A封装的器件内部有7个电阻和8个管脚,7个电阻共用一个接地端。SIP-B有四个电阻和8个管脚,每个电阻都有独立的接地端。所有的电阻都是50欧。B封装要比A封装的器件的串扰情况好100倍。

TABLE 6.2 COUPLING COEFFICIENTS IN SIP TERMINATING NETWORKS

| Package | From | То | Coupling coefficient |

|---------|------|----|----------------------|

| SIP-A   | 7    | 6  | 8250.0 ps-Ω (worst)  |

| SIP-A   | 7    | 1  | 2050.0 ps-Ω (best)   |

| SIP-B   | 4    | 3  | 95.0 ps-Ω (worst)    |

| SIP-B   | 4    | 1  | 8.0 ps-Ω (best)      |

利用等式6.30可以把这些系数转换为实际的串扰电压。

#### 本节要点:

• 匹配电阻的物理布局影响信号回路间的串扰。

2001-08-16 版权所有,侵权必究 第22页,共22页