# Freescale Technology Forum

**Design Innovation.**

November 2008

# Hands-on Workshop: An Introduction to Freescale Segment LCD Solutions

PZ114

System Engineer

# Freescale Technology Forum

**Design Innovation.**

**Basis on Liquid Crystal Display Technologies**

## **Segment LCD Products Everywhere**

**Disk**

**Thermal Stat**

**Appliances**

**Clock**

Remote Controller

Portable One Time Token

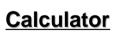

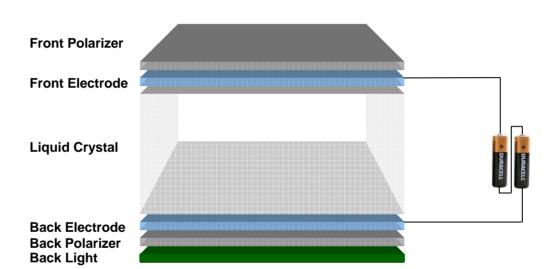

### **Basics of LCD Operation**

- ► The twisted nematic (TN) The most common LCD

- Sandwich Construction

- Front Polarizer

- Front Electrode

- Liquid Crystal

- Back Electrode

- Back Polarizer

- Back Light

#### Reflective twisted nematic LCD

### **Display Segments**

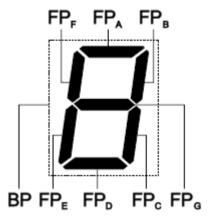

### ► Static Display

- One backplane electrode for all segments

- One front plane electrode for each segment

#### ▶ Dynamic Display

- Matrix organization

- Multi back plane time-division shared by all front plane

- Multi front plane time-division shared by all back plane

### ► Dynamic VS Static

- Dynamic display needs less driving terminals

- Static has better optical properties

A typical 7-segment static display

A typical 3 front plane and 3 back plane dynamic display

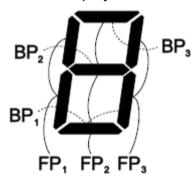

### **Dynamic Segment Display**

- ► Duty Time Component

- the number of phases of the refresh cycle

- Mostly, duty cycle equal to back plane number

- Most used duty cycle 4x mode

- ▶ Bias Voltage Component

- The voltage across the LCD cell during the inactive phases

- Most used bias 1/3 mode

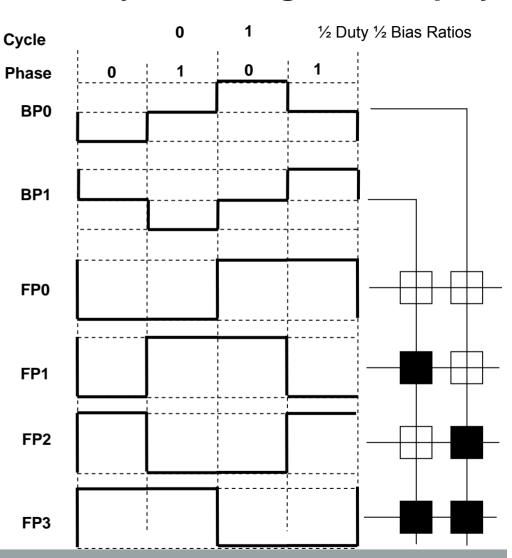

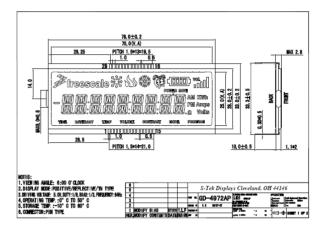

#### **Order LCD Glass**

- **▶** Dimension

- ► Segment Definition

- · Front plane mapping

- · Back plane mapping

- ▶ Parameters

- Viewing Angle:

- 12:00, 3:00, 6:00, 9:00 O'Clock

- · Display Mode

- TN, STN, ...

- POSITIVE/NEGATIVE

- REFELECT/TRANSMISSIVE/

- Operating Voltage

- 3V, 5V, ...

- Duty cycle and Bias

- Operating Frequency

- ▶ Others

- Operating/Storage Temperature

- Connector

# **Freescale Segment LCD MCU Family**

## Freescale Segment LCD MCU Family

- MC9S08LL16 Low-voltage ultralow-power LCD Microcontroller

- Operating Voltage 1.8V 3.6V

- Enabled by Flexis Technologies

- Up to 8×24 or 4×28 LCD segments

- ► MC9RS08LA8 Cost-effective Low-power LCD Microcontroller

- Operating Voltage 2.7V 5.5V

- Enabled by RS08 CPU core

- Up to 8×21 or 4×25 LCD segments

- MC9RS08LE4 Lowest-end Lowpower LCD Microcontroller

- Operating Voltage 2.7V 5.5V

- Enabled by RS08 CPU core

- Up to 8×14 or 4×18 LCD segments

- Packaged in 28-pin SOIC

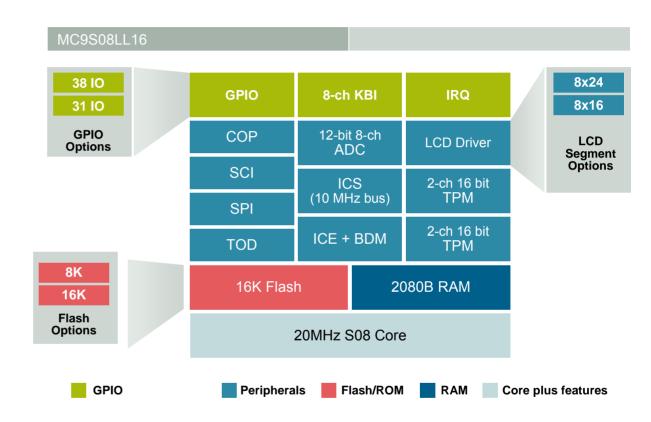

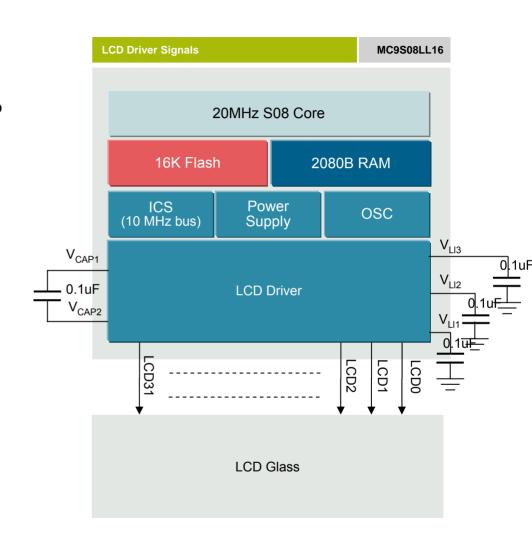

#### MC9S08LL16 Features

- ▶ Voltage Range

- 1.8V ~ 3.6V

- ► Core & BUS

- 20MHz S08 Core

- 10MHz BUS

- ► LCD Driver

- 8x24 in 64-pin

- 8x14 in 48-pin

- ▶ Peripherals

- 2x 2-ch 16-bit TPM

- 1x TOD

- 1x 12-bit 8-ch ADC

- Communications

- SCI

- SPI

- IIC

- Package

- 64-pin LQFP

- 48-pin QFN & LQFP

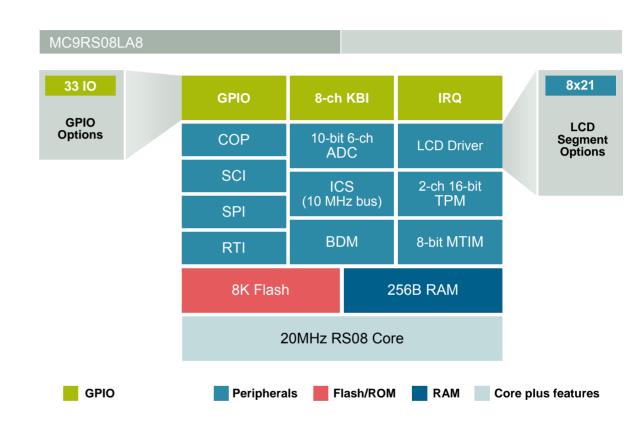

#### MC9RS08LA8 Features

- ▶ Voltage Range

- 2.7V ~ 5.5V

- ► Core & BUS

- 20MHz RS08 Core

- 10MHz BUS

- ► LCD Driver

- 8 x 21

- ▶ Peripherals

- 1 x 2-ch 16-bit TPM

- 1 x 8-bit MTIM

- 1 x RTI

- 1 x 10-bit 6-ch ADC

- Communications

- SCI

- SPI

- IIC

- Package

- 48-pin QFN & LQFP

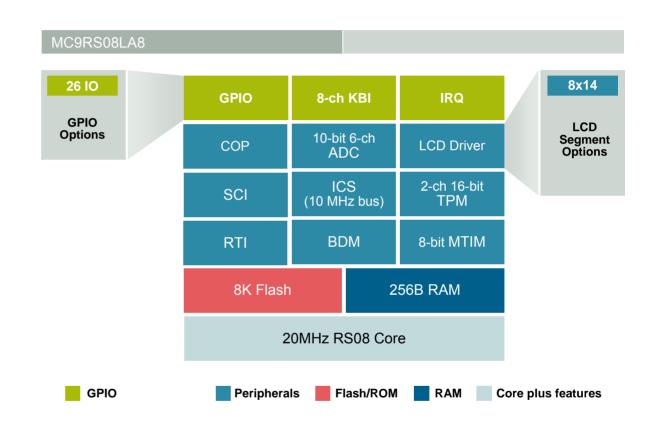

#### MC9RS08LE4 Features

- ▶ Voltage Range

- 2.7V ~ 5.5V

- ► Core & BUS

- 20MHz RS08 Core

- 10MHz BUS

- ► LCD Driver

- 8 x 14

- ▶ Peripherals

- 2 x 2-ch 16-bit TPM

- 1 x RTI

- 1 x 10-bit 8-ch ADC

- Communications

- SCI

- ▶ Package

- 28-pin SOIC

# **Freescale LCD MCU Family**

|                   |                              | MC9S08LL16                                 | MC9RS08LA8                                     | MC9RS08LE4                                |

|-------------------|------------------------------|--------------------------------------------|------------------------------------------------|-------------------------------------------|

| Operating Voltage |                              | 1.8V – 3.6V                                | 2.7V – 5.5V                                    | 2.7V – 5.5V                               |

| CPU               |                              | S08@20MHz                                  | RS08@20MHz                                     | RS08@20MHz                                |

| BUS               |                              | 10MHz                                      | 10MHz                                          | 10MHz                                     |

| Memory on-chip    | FLASH                        | 16KB                                       | 8KB                                            | 4KB                                       |

| Welliory On-Chip  | RAM                          | 2080B                                      | 256B                                           | 256B                                      |

| Timers            |                              | 2 	imes 2-ch 16-bit TPM                    | 1 $	imes$ 2-ch 16-bit TPM 1 $	imes$ 8-bit MTIM | 2 	imes 2-ch 16-bit TPM                   |

| Real-Time Clock   |                              | TOD                                        | RTI                                            | RTI                                       |

|                   | SCI                          | YES                                        | YES                                            | YES                                       |

| Comms.            | SPI                          | YES                                        | N/A                                            | N/A                                       |

|                   | IIC                          | YES                                        | N/A                                            | N/A                                       |

| ADC               |                              | 8-ch 12-bit                                | 6-ch 10-bit                                    | 8-ch 10-bit                               |

| ACMP              |                              | YES                                        | YES                                            | N/A                                       |

|                   | Segments                     | $8 \times 24 = 192$<br>$4 \times 28 = 112$ | $8 \times 21 = 168$<br>$4 \times 25 = 100$     | $8 \times 14 = 112$<br>$4 \times 18 = 72$ |

|                   | Charge Pump                  | YES                                        | YES                                            | NO                                        |

| LCD Driver        | Resister Network             | YES                                        | YES                                            | YES                                       |

|                   | VLCD pin                     | YES                                        | NO                                             | NO                                        |

|                   | VCAP1 VCAP2<br>VII1 VLL2VII3 | YES                                        | YES                                            | NO                                        |

| GPI0              |                              | 38                                         | 33                                             | 26                                        |

| Packages          |                              | 64-pin 48-pin                              | 48-pin                                         | 28-pin                                    |

#### Introduction to Freescale LCD Driver

### **LCD Driver Signals**

#### ► LCD FP/BP Pins

- LCD driver pins

- All pins can operate as FP or BP

- Up to 8 Back plane driver pins

- ►V<sub>LCD</sub> Pins

- LCD supply voltage

- Available on LL16 only

- ► LCD Bias Pins

- V<sub>113</sub> = Full LCD driving voltage

- V<sub>112</sub> = 2/3 LCD driving voltage

- V<sub>111</sub> = 1/3 LCD driving voltage

- Available on LL16 and LA8 only

- ► LCD Charge Pump Pins

- V<sub>CAP1</sub> and V<sub>CAP2</sub>

- Available on LL16 and LA8 only

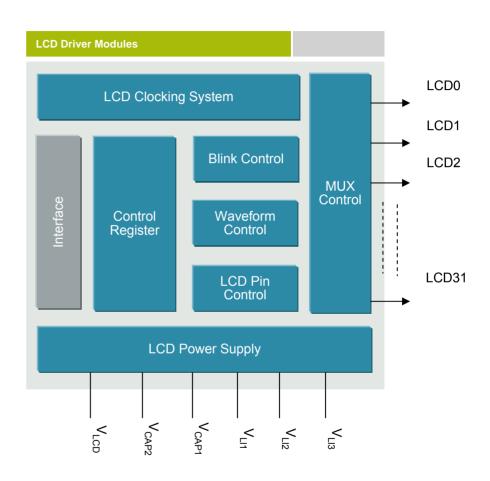

#### **LCD Driver Architecture**

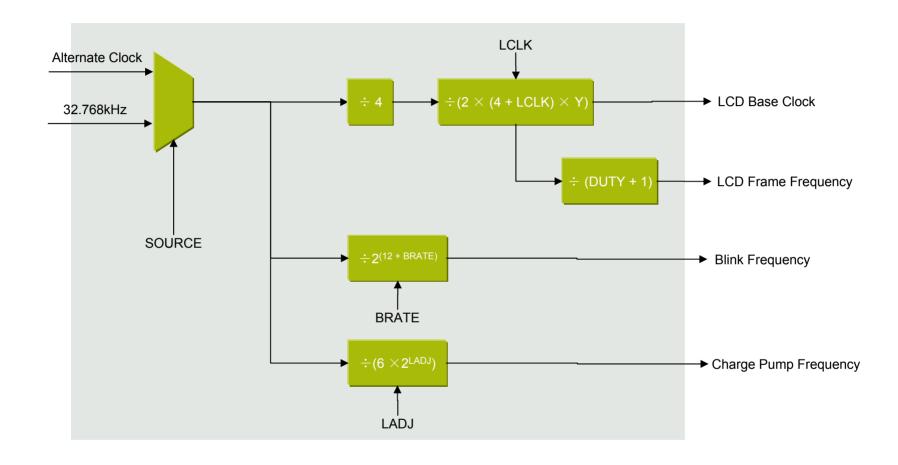

#### ► LCD Clocking Control

- Providing Clock reference to generate LCD waveform and light charge pump

- ▶ LCD Power Control

- Providing Power Supply to LCD waveform

- ► LCD Pin Control

- Enable / Disable LCD Pins

- Enable / Disable LCD Backplane Pins

- Waveform Control

- Generate LCD waveforms on each LCD driver pin

- Blink Control

- Control LCD Blink mode and frequency

- MUX Control

- Mapping LCD waveforms on LCD pins

- Control Registers and Interface

- Interfacing CPU and contains all configuration information

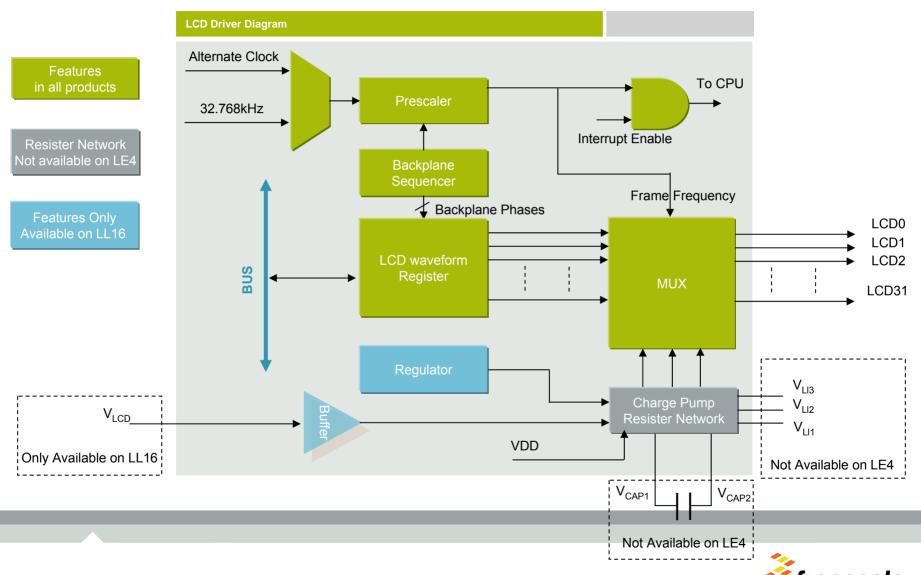

### **LCD Driver Diagram**

# Freescale Technology Forum

**Design Innovation.**

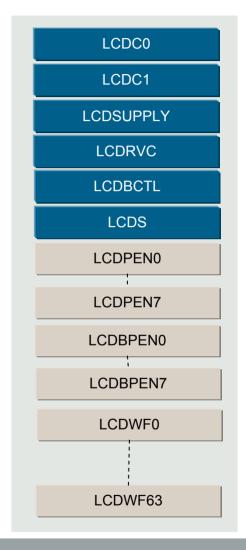

# **LCD Driver Register Definition**

### **LCD Control Registers**

- ► LCD Control & Status Registers

- LCD Control Register 0 (LCDC0)

- LCD Control Register 1 (LCDC1)

- LCD Voltage Supply Register (LCD SUPPLY)

- LCD Regulated Voltage Control Register (LCDRVC)

- LCD Blink Control Register (LCDBCTL)

- LCD Status Register (LCDS)

- ► LCD Pins & Waveforms Registers

- LCD Pin Enable Registers ( LCDPEN0 LCDPEN7)

- LCD Backplane Pin Enable Registers (LCDBPEN0 – LCDBPEN7)

- LCD Waveform Registers (LCDWF0 LCDWF63)

LCD Control & Status Registers

LCD Pins & Waveforms Registers

### **LCD Control & Status Registers**

LCD Control Register 0

LCD Control Register 1

LCD Voltage Supply Register

LCD Regulated Voltage Control

Register LCD Blink Control Register

> LCD Status Register

| Name       |   | 7       | 6        | 5     | 4     | 3       | 2        | 1        | 0        |

|------------|---|---------|----------|-------|-------|---------|----------|----------|----------|

| 1.0000     | R | LCDEN   | SOURCE   | LCLK2 | LCLK1 | LCLK0   | DUTY2    | DUTY1    | DUTY0    |

| LCDC0      | W |         |          |       |       |         |          |          | 50110    |

| LCDC1      | R | LCDIEN  | 0        | 0     | 0     | 0       | FCDEN    | LCDWAI   | LCDSTP   |

| LCDC1      | W | LODILIV |          |       |       |         | TODEN    | LODVVAI  | LOBOTI   |

|            | R | CPSEL   | HREFSEL  | LADJ1 | LADJ0 | 0       | BBYPASS  | VSUPPLY1 | VSUPPLY0 |

| LCDCSUPPLY | W | OFFE    | TINEFOLL | LADOT | LADOO |         | BBTI AGG |          |          |

| 1.000.40   | R | RVEN    | 0        | 0     | 0     | RVTRIM3 | RVTRIM2  | RVTRIM1  | RVTRIM0  |

| LCDRVC     | W |         |          |       |       |         |          |          | 100 1100 |

|            | R | BLINK   | ALT      | BLANK |       | BMODE   | BRATE2   | BRATE1   | BRATE0   |

| LCDBCTL    | W | BLINK   | ALI      | BLANK |       | BIVIODE | DIVATES  | DIVALET  | DIVATEO  |

| 1.000      | R | LCDIF   | 0        | 0     | 0     | 0       | 0        | 0        | 0        |

| LCDS       | W |         |          |       |       |         |          |          |          |

# LCD Control Register 0 (LCDC0)

#### LCD Control Register 0 (LCDC0)

R W Reset

| 7     | 6      | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|--------|-------|-------|-------|-------|-------|-------|

| LCDEN | SOURCE | LCLK2 | LCLK1 | LCLK0 | DUTY2 | DUTY1 | DUTY0 |

| 0     | 0      | 0     | 0     | 0     | 0     | 1     | 1     |

7 LCDEN LCD Driver Enable — LCDEN starts LCD-module-waveform generator.

6 SOURCE LCD Clock Source Select — To select clock source as the basis for LCD clock

5:3 LCLK **LCD Prescaler** — To use a clock divider to generate LCD waveform frame frequency. Detail

2:9 DUTY **LCD Duty Select** — To select the duty cycle of LCD module

# LCD Control Register 1 (LCDC1)

#### LCD Control Register 1 (LCDC1)

R W Reset

|        | 7      | 6 | 5 | 4 | 3 | 2     | 1      | 0      |

|--------|--------|---|---|---|---|-------|--------|--------|

| R<br>W | LCDIEN |   |   |   |   | FCDEN | LCDWAI | LCDSTP |

| et     | 0      | 0 | 0 | 0 | 0 | 1     | 0      | 0      |

- 7 LCDIEN **LCD Module Frame Frequency Driver Enable** Enables an LCD interrupt event that coincides with the LCD module frame frequency.

- 2 FCDEN **Full Complementary Drive Enable** To allow GPIO that are shared with LCD pins to operate as full complementary if the other conditions necessary have been met

- 1 LCDWAI **LCD Module Driver and Charge Pump in Wait Mode** To allow the LCD driver and charge pump to continue running during wait mode

- 0 LCDSTP LCD Module Driver and Charge Pump in Stop Mode To allow the LCD driver and charge pump to continue running during stop mode

# LCD Voltage Supply Register (LCDSUPPLY)

#### LCD Voltage Supply Register (LCDSUPPLY)

R W Reset

|        | 7     | 6       | 5     | 4     | 3 | 2       | 1        | 0        |

|--------|-------|---------|-------|-------|---|---------|----------|----------|

| R<br>W | CPSEL | HREFSEL | LADJ1 | LADJ0 |   | BBYPASS | VSUPPLY1 | VSUPPLY0 |

| et     | 0     | 0       | 0     | 0     | 0 | 1       | 0        | 0        |

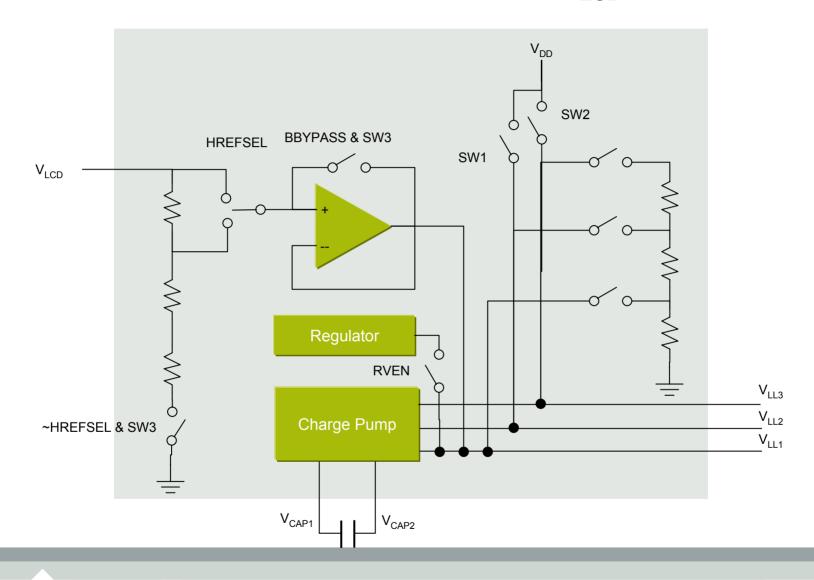

- 7 SPSEL Charge Pump or Resistor Bias Select —To select LCD module charge pump or a resistor network to supply the LCD voltages  $V_{LL1}$ ,  $V_{LL2}$ , and  $V_{LL3}$ .

- 6 HREFSEL **High Reference Select** To select reference bias divider

- 5:4 LADJ **LCD Module Load Adjust** To configure the LCD module to handle different LCD glass capacitance

- 2 BBYPASS Op Amp Control To determine whether the internal LCD op amp buffer is bypassed

- 1:0 VSUPPLY **Voltage Supply Control** To configure LCD module power supply

# LCD Regulated Voltage Control Register (LCDRVC)

#### LCD Regulated Voltage Control Register (LCDRVC)

R W Reset

|     | 7    | 6 | 5 | 4 | 3       | 2       | 1       | 0       |

|-----|------|---|---|---|---------|---------|---------|---------|

| R   |      |   |   |   |         |         |         |         |

| W   | RVEN |   |   |   | RVTRIM3 | RVTRIM2 | RVTRIM1 | RVTRIM0 |

| set | 0    | 0 | 0 | 0 | 0       | 0       | 0       | 0       |

7 RVEN Regulated Voltage Enable —To enable internal voltage regulator

3:0 RVTRIM Regulated Voltage Trim — To adjust the regulated input

# LCD Blink Control Register (LCDBCTL)

#### LCD Blink Control Register (LCDBCTL)

R W Reset

| 7     | 6   | 5     | 4 | 3     | 2      | 1      | 0      |

|-------|-----|-------|---|-------|--------|--------|--------|

| BLINK | ALT | BLANK |   | BMODE | BRATE2 | BRATE1 | BRATE0 |

| 0     | 0   | 0     | 0 | 0     | 0      | 0      | 0      |

- 7 BLINK Blink Command —To start LCD module blinking

- 6 ALT **Alternate Display Mode** —To start Alternate display mode for 4 backplanes or less configurations

- 5 BLANK Blink Display Mode —To start Blank display mode

- 3 BMODE Blink Display Mode —To select the blink mode displayed during the blink period

- 2:0 BRATE Blink-Rate Configuration —To select frequency at which the LCD display blinks

# LCD Status Register (LCDS)

#### **LCD Status Register (LCDS)**

|       | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------|---|---|---|---|---|---|---|

| R     |       |   |   |   |   |   |   |   |

| W     | LCDIF |   |   |   |   |   |   |   |

| Reset | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

7 LCDIF LCD Interrupt Flag Command —To indicate an interrupt condition occurred

### **LCD Pins and Waveforms Registers**

LCD Pin Enable Register

| Name   |   | 7                   | 6                  | 5                  | 4                  | 3                  | 2                        | 1                  | 0                   |

|--------|---|---------------------|--------------------|--------------------|--------------------|--------------------|--------------------------|--------------------|---------------------|

| LODDEN | R | PEN <sub>N+7</sub>  | PEN <sub>N+6</sub> | PEN <sub>N+5</sub> | PEN <sub>N+4</sub> | PEN <sub>N+3</sub> | PEN <sub>N+2</sub>       | PEN <sub>N+1</sub> | PEN <sub>N</sub>    |

| LCDPEN | W | . =: <b>\</b> N + / | . =: N + 6         | . =: N+5           | . = 1 N + 4        | . = 1 N + 3        | . = 1 1 <sub>N + 2</sub> | . = N+1            | . =. · <sub>N</sub> |

LCD Back Pin Enable Register

| Name    |   | 7                     | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                 |

|---------|---|-----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------|

| LODDDEN | R | BPEN <sub>N+7</sub>   | BPEN <sub>N+6</sub> | BPEN <sub>N+5</sub> | BPEN <sub>N+4</sub> | BPEN <sub>N+3</sub> | BPEN <sub>N+2</sub> | BPEN <sub>N+1</sub> | BPEN <sub>N</sub> |

| LCDBPEN | W | D1 211 <sub>N+7</sub> | DI 211N+6           | D1 211N+5           | D1 211N+4           | D1 211N+3           | D1 211N+2           | D1 211N+1           | 2. 2. N           |

LCD Waveform Register

| Name  |   | 7       | 6       | 5      | 4       | 3       | 2       | 1       | 0       |

|-------|---|---------|---------|--------|---------|---------|---------|---------|---------|

| LODIA | R | BPHLCD  | BPGLCD  | BPFLCD | BPELCD  | BPDLCD  | BPCLCD  | BPBLCD  | BPALCD  |

| LCDWF | W | 5111205 | B1 020B | 511205 | B1 220B | 51 5205 | DI 020D | B1 B20B | 2.7.202 |

# LCD Pin Enable Register (LCDPEN)

#### LCD Pin Enable Register (LCDPEN)

R W Reset

| 7                  | 6                  | 5                  | 4                  | 3                  | 2                  | 1                  | 0                |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|------------------|

| PEN <sub>N+7</sub> | PEN <sub>N+6</sub> | PEN <sub>N+5</sub> | PEN <sub>N+4</sub> | PEN <sub>N+3</sub> | PEN <sub>N+2</sub> | PEN <sub>N+1</sub> | PEN <sub>N</sub> |

| 0                  | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  | 0                |

7:0 PEN **LCD Pin Enable** —To enable LCD pin for LCD operation

# LCD Backplane Pin Enable Register (LCDBPEN)

#### LCD Backplane Pin Enable Register (LCDBPEN)

R W Reset

|   | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                 |

|---|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------|

| , | BPEN <sub>N+7</sub> | BPEN <sub>N+6</sub> | BPEN <sub>N+5</sub> | BPEN <sub>N+4</sub> | BPEN <sub>N+3</sub> | BPEN <sub>N+2</sub> | BPEN <sub>N+1</sub> | BPEN <sub>N</sub> |

|   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                 |

7:0 BPEN **LCD Backplane Pin Enable** —To enable LCD pin as front plane or backplane for LCD operation

# LCD Waveform Register (LCDWF)

#### **LCD Waveform Register (LCDWF)**

R W Reset

| 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|---------|---------|---------|---------|---------|---------|---------|

| BPHLCDx | BPGLCDx | BPFLCDx | BPELCDx | BPDLCDx | BPCLCDx | BPBLCDx | BPALCDx |

| 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

#### 7:0 BP[y]LCD[x]

#### **Segment-on-Frontplane Operation**

- switch on/off state if this pin is configured as front plane at phase Y

#### **Segment-on-Backplane Operation**

- switch on/off state if this pin is configured as back plane at phase X

# Freescale Technology Forum

**Design Innovation.**

# **Operate LCD Driver**

### **Operate LCD Driver**

- ▶ Select LCD Clock Source

- Select Internal or External Clock Reference

- ► Select LCD Power Supply

- Select Internal or External Power Supply

- Select Bias Voltage Generator

- ► Set LCD Duty Cycle and Bias

- Select Correct Duty Cycle

- 1/3 Bias

- Enable LCD Pin and Set Waveform

- Enable LCD Pin

- Enable LCD Backplane Pin

- Set Wave form

- Special effects

- Blink

#### **Select LCD Clock Source**

### ► LCD Clock Input

Optimized to operate using a 32.768kHz clock input

#### ► LCD Clock Distribution

- LCD Base Clock To generate each Backplane phase

- LCD Frame Frequency To generate each Frame Timing (28 ~ 58Hz preferred)

- LCD Charge Pump Clock To generate bias voltages via charge pump

- Blink Frequency

### **LCD Clock Distribution**

## **LCD Module Frame Frequency Calculation**

| Duty Cycle |   | 1/1  | 1/2  | 1/3  | 1/4  | 1/5  | 1/6  | 1/7  | 1/8  |

|------------|---|------|------|------|------|------|------|------|------|

| Υ          |   | 16   | 8    | 5    | 4    | 3    | 3    | 2    | 2    |

|            | 0 | 64   | 64   | 68.3 | 64   | 68.3 | 56.9 | 73.1 | 64   |

|            | 1 | 51.2 | 51.2 | 54.6 | 51.2 | 54.6 | 45.5 | 58.5 | 51.2 |

|            | 2 | 42.7 | 42.7 | 45.5 | 42.7 | 45.5 | 37.9 | 48.8 | 42.7 |

| LOLK       | 3 | 36.6 | 36.6 | 39   | 36.6 | 39   | 32.5 | 41.8 | 36.6 |

| LCLK       | 4 | 32   | 32   | 34.1 | 32   | 34.1 | 28.4 | 36.6 | 32   |

|            | 5 | 28.4 | 28.4 | 30.3 | 28.4 | 30.3 | 25.3 | 32.5 | 28.4 |

|            | 6 | 25.6 | 25.6 | 27.3 | 25.6 | 27.3 | 22.8 | 29.3 | 25.6 |

|            | 7 | 23.3 | 23.3 | 24.8 | 23.3 | 24.8 | 20.7 | 26.6 | 23.3 |

LCD input Frequency ~ 32.768kHz

28Hz <= Frame Frequency <= 58Hz

Frame Frequency < 28Hz Or Frame Frequency > 58Hz

# **LCD Module Frame Frequency Calculation**

| Duty | Cycle | 1/1  | 1/2  | 1/3  | 1/4  | 1/5  | 1/6  | 1/7  | 1/8  |

|------|-------|------|------|------|------|------|------|------|------|

| `    | (     | 16   | 8    | 5    | 4    | 3    | 3    | 2    | 2    |

|      | 0     | 76.3 | 76.3 | 81.4 | 76.3 | 81.4 | 67.8 | 87.2 | 76.3 |

|      | 1     | 61   | 61   | 65.1 | 61   | 65.1 | 54.3 | 69.8 | 61   |

|      | 2     | 50.9 | 50.9 | 54.3 | 50.9 | 54.3 | 45.2 | 58.1 | 50.9 |

| LOLK | 3     | 43.6 | 43.6 | 46.5 | 43.6 | 46.5 | 38.8 | 49.8 | 43.6 |

| LCLK | 4     | 38.1 | 38.1 | 40.7 | 38.1 | 40.7 | 33.9 | 43.6 | 38.1 |

|      | 5     | 33.9 | 33.9 | 36.2 | 33.9 | 36.2 | 30.1 | 38.8 | 33.9 |

|      | 6     | 30.5 | 30.5 | 32.6 | 30.5 | 32.6 | 27.1 | 34.9 | 30.5 |

|      | 7     | 27.7 | 27.7 | 29.6 | 27.7 | 29.6 | 24.7 | 31.7 | 27.7 |

LCD input Frequency ~ 39.0625kHz

28Hz <= Frame Frequency <= 58Hz

Frame Frequency < 28Hz Or Frame Frequency > 58Hz

## **Select LCD Power Supply**

- ▶ Power Supply Input

- V<sub>LL2</sub> internally from V<sub>DD</sub>

- V<sub>LL3</sub> internally from V<sub>DD</sub>

- V<sub>LL1</sub> internally from V<sub>LCD</sub>

- V<sub>LL3</sub> externally from V<sub>DD</sub>

- V<sub>LL1</sub> internally from V<sub>IREG</sub>

- Bias Generator

- Charge Pump

- Resister Network

- ▶ V<sub>LCD</sub> Operation

- Voltage Divider

- Op Amp Buffer

- ▶ V<sub>IREG</sub> Operation

- Monitor LCD Voltage

- V<sub>LCD</sub> on AD20

- $V_{LL1}^{-33}$  on AD21

- V<sub>IREG</sub> on AD22

# **LCD Charge Pump and V<sub>LCD</sub> Voltage Divider**

# **LCD Charge Pump and V<sub>LCD</sub> Voltage Divider**

| VSUPPLY[1:0] | Configuration                                                                       | SW1 | SW2 | SW3 |

|--------------|-------------------------------------------------------------------------------------|-----|-----|-----|

| 00           | V <sub>LL2</sub> internally from V <sub>DD</sub>                                    | 1   | 0   | 0   |

| 01           | V <sub>LL3</sub> internally from V <sub>DD</sub>                                    | 0   | 1   | 0   |

| 10           | V <sub>LL1</sub> internally from V <sub>LCD</sub>                                   | 0   | 0   | 1   |

| 11           | $ m V_{LL3}$ externally from $ m V_{DD}$ $ m V_{LL1}$ internally from $ m V_{IREG}$ | 0   | 0   | 0   |

# **Set LCD Duty Cycle and Bias**

## ► Set LCD Duty Cycle

- Support 8 duty cycle modes of operation

- 1/1 duty (1 backplane) (Phase A), 1/3 bias (4 voltage levels)

- 1/2 duty (2 backplanes) (Phase A, B), 1/3 bias (4 voltage levels)

- 1/3 duty (3 backplanes) (Phase A, B, C), 1/3 bias (4 voltage levels)

- 1/4 duty (4 backplanes) (Phase A, B, C, D), 1/3 bias (4 voltage levels)

- 1/5 duty (5 backplanes) (Phase A, B, C, D, E), 1/3 bias (4 voltage levels)

- 1/6 duty (6 backplanes) (Phase A, B, C, D, E, F), 1/3 bias (4 voltage levels)

- 1/7 duty (7 backplanes) (Phase A, B, C, D, E, F, G), 1/3 bias (4 voltage levels)

- 1/8 duty (8 backplanes) (Phase A, B, C, D, E, F, G, H), 1/3 bias (4 voltage levels)

#### ▶ Bias

The LCD module is designed to operate using the 1/3 bias mode

# **LCD Duty Cycle Modes**

| Durby | DUTY  |       |       | Number of Deskalance | Dhaca Carriana |  |  |

|-------|-------|-------|-------|----------------------|----------------|--|--|

| Duty  | DUTY2 | DUTY1 | DUTY0 | Number of Backplanes | Phase Sequence |  |  |

| 1/1   | 0     | 0     | 0     | 1                    | Α              |  |  |

| 1/2   | 0     | 0     | 1     | 2                    | АВ             |  |  |

| 1/3   | 0     | 1     | 0     | 3                    | ABC            |  |  |

| 1/4   | 0     | 1     | 1     | 4                    | ABCD           |  |  |

| 1/5   | 1     | 0     | 0     | 5                    | ABCDE          |  |  |

| 1/6   | 1     | 0     | 1     | 6                    | ABCDEF         |  |  |

| 1/7   | 1     | 1     | 0     | 7                    | ABCDEFG        |  |  |

| 1/8   | 1     | 1     | 1     | 8                    | ABCDEFGH       |  |  |

#### **Enable LCD Pin and Set Waveform**

- ► Enable LCD Pins

- To enable all LCD pins connecting to LCD glass

- ► Enable LCD Backplane Pins

- To enable LCD Backplane pins

- Up to 8 LCD Backplane pins

- ► Set Waveform

- Set Backplane Pins Phase

- Set Front plane Pins contents

#### **Enable LCD Pin and Set Waveform**

```

// Initialize LCDPENx

LCDPEN0 = 0xFF;

Enable

LCDPEN1 = 0xFF:

I CD Pins

LCDPEN2 = 0xFF:

LCDPEN3 = 0x1F;

// Initialize LCDBPENx

LCDBPEN0 = 0x80:

Fnable I CD

LCDBPEN1 = 0x7F;

Backplane Pins

LCDBPEN2 = 0x00;

LCDBPEN3 = 0x00:

// Initialize LCDWFx

LCDWF7 = 0x80:

LCDWF8 = 0x40:

LCDWF9 = 0x20:

LCDWF10 = 0x10;

Set LCD

LCDWF11 = 0x08;

Backplane Phase

LCDWF12 = 0x04;

LCDWF13 = 0x02;

LCDWF14 = 0x01:

```

LCD Pin: LCD0 ~ LCD29

8x21 mode

Backplane Pin: LCD7 ~ LCD14

## **Design resources**

#### Get started fast

### ► Get started with segment LCD solutions freescale.com/8bit

- Documentation

- CodeWarrior Development Studio for Microcontrollers 6.x

- DEMOS08LL16 demo board \$69

- DEMO9RS08LA8 demo board \$59

- DEMO9RS08LE4 demo board \$59

# ► Training and support—freescale.com/LCD

- Reference designs

- Migration application notes

- See a demonstration

- RS08

- HCS08

# How Freescale beats the LCD design challenge

| Challenge                                                                                                                                                                                                                                                                                                                                                                    | Solutions                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Too many pins required to drive many segments. Normally:                                                                                                                                                                                                                                                                                                                     | Freescale requires fewer pins to drive the same number of segments and also support 4x by mode                                                                                                                                                                                                                                    |  |  |  |

| 52 pins are required for 192 segments in 4x48 mode                                                                                                                                                                                                                                                                                                                           | 32 pins are required for 192 segments in 8x24 mode                                                                                                                                                                                                                                                                                |  |  |  |

| 44 pins are required for 160 segments in 4x40 mode                                                                                                                                                                                                                                                                                                                           | 28 pins are required for 160 segments in 8x20 mode                                                                                                                                                                                                                                                                                |  |  |  |

| 29 pins are required for 100 segments in 4x25 mode                                                                                                                                                                                                                                                                                                                           | 17 pins are required for 104 segments in 8x13 mode                                                                                                                                                                                                                                                                                |  |  |  |

| Blinking mode takes power and resources                                                                                                                                                                                                                                                                                                                                      | Freescale offers a low-power blinking mode                                                                                                                                                                                                                                                                                        |  |  |  |

| Competitor parts offer blinking mode by setting a bit in a register. However, the microcontroller must exit stop mode, execute the code and then go back to sleep in every blinking period, which increases power consumption                                                                                                                                                | Freescale's low-power blinking mode does not need to wake up the controller, Blinking mode can be activated and the CPU can go to sleep, but the segments will remain blinking at the pre-set frequency, In addition, an alternate display feature can be activated to display additional data (i.e., blink temperature and time) |  |  |  |

| Layout is very complex because the frontplanes (FPs) and backplanes (BPs) are fixed in pin-outs                                                                                                                                                                                                                                                                              | Freescale offers FP and BP re- assignments                                                                                                                                                                                                                                                                                        |  |  |  |

| FPs and BPs are commonly distributed on all sides of the microcontroller, so special device placement and layout has to be performed to reduce electromagnetic interference (EMI) and shorten communication lines between the microcontroller and the LCD display. This makes the layout very complex, and implementing changes to improve EMI will be a time consuming task | FP and BP can be software selectable to be either FP or BP, making board layout an easier task and very flexible for changes                                                                                                                                                                                                      |  |  |  |

| LCD glass requires many voltages, and voltage divider resistor ladders consume too much power                                                                                                                                                                                                                                                                                | Freescale's internal charge pump provides all voltages required to power up LCD glass                                                                                                                                                                                                                                             |  |  |  |

| Battery voltage drops over the time to the point where displays suffers degradation by not having the optimum voltage levels                                                                                                                                                                                                                                                 | Freescale solutions provide an internal software selectable regulated power supply that keeps constant voltage across LCD glass to avoid degradation. In addition, the LL16 offers 4 bits resolution trim to adjust contrast control (Only for S08 and V1 cores)                                                                  |  |  |  |

### **Related Session Resources**

### **Session Location – Online Literature Library**

http://www.freescale.com/webapp/sps/site/homepage.jsp?nodeId=052577903644CB

#### **Sessions**

| Session ID | Title |  |  |  |

|------------|-------|--|--|--|

|            |       |  |  |  |

|            |       |  |  |  |

|            |       |  |  |  |

|            |       |  |  |  |

|            |       |  |  |  |

|            |       |  |  |  |

#### **Demos**

| Pedestal ID | Demo Title |

|-------------|------------|

|             |            |

|             |            |

|             |            |