#### Nov. 6, 2008

#### Quality/Zero Defect: Freescale Strategies, Measures and Tools

PA101

**Peter Kang** China Automotive FAE Manager

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008.

### **Freescale Quality Vision**

| Vision   | It's impossible.<br>Zero = Zero                                                                                                                                                                                                         |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mission  | <ul> <li>Zero Defects for the Automotive Market</li> <li>Safe Launch on New Product Introductions</li> </ul>                                                                                                                            |

| Strategy | Defects <ul> <li>Containment</li> <li>Analysis</li> <li>Improvement</li> </ul> Spill Elimination Safe Launch <ul> <li>New Technology Introduction</li> <li>New Product Development</li> <li>Technology and Product Transfers</li> </ul> |

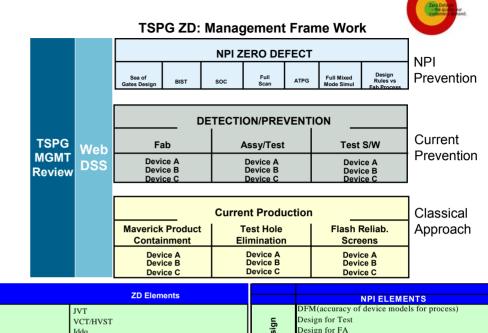

## Looking Back on the Journey

#### Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008.

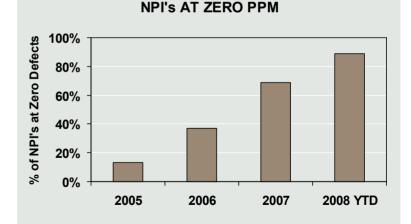

- In 2004/ 2005 we started the journey for Zero defects

- ► We set a management framework :

- Classical: i.e, Containment and screens

- Detection and Prevention

- Focus on Zero Defect techniques for New Products

- We defined a set of ZD elements in the Manufacturing, Product and Test and Design

- These were constantly upgraded and carried forward as 'ZD base' for each new technology and product.

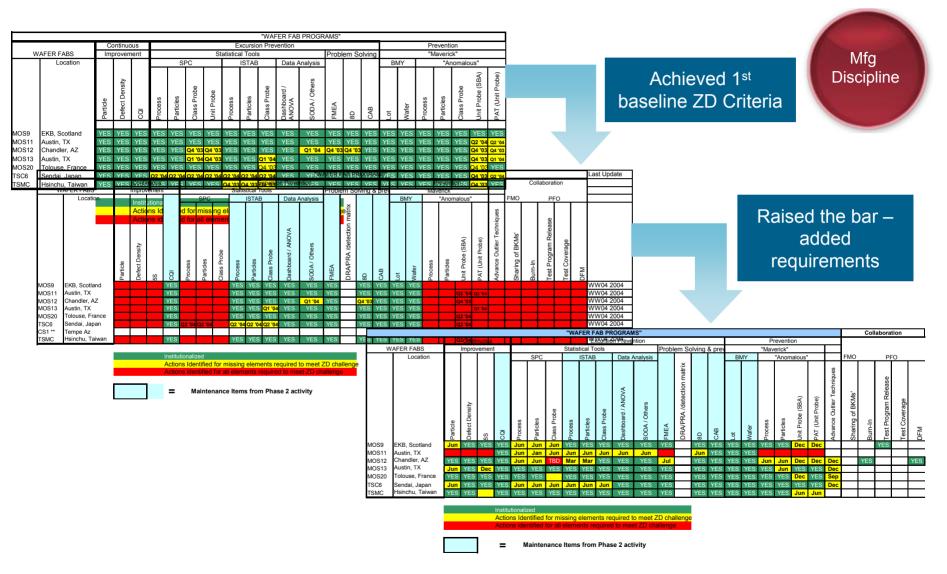

- In manufacturing we raised the bar successively

|                                      | ZD Elements                                                                                                                                                                                                                                                                                                                                                                                                        |              |                                                                                                                                                                                                                                  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Zero Defect<br>Program       | JVT<br>VCT/HVST<br>Iddq<br>Test Coverage (AEC Spec)<br>Lessons learned Look Across<br>Standardized NVM test methods<br>Burn-In                                                                                                                                                                                                                                                                                     | ion Design   | NPI ELEMENTS<br>DFM(accuracy of device models for process)<br>Design for Test<br>Design for FA<br>Full Chip STA vs Module<br>Flash & SRAM ECC<br>Independent Verification Team<br>Verification at module, platform, system level |

| Manufacturing Zero<br>Defect Program | WebDSS COI Entry<br>PAT (Unit Probe)<br>BMY<br>SBL Phase1<br>SBL Phase 2                                                                                                                                                                                                                                                                                                                                           | t            | Random Pattern generation at Module level<br>100% RTL block & expression coverage<br>Spec Tagging<br>SRAM & Flash BIST<br>Trace Matrix                                                                                           |

| Division Specific<br>Elements        | PAT (Final Test)<br>Gate Stress<br>100% Cold Test<br>100% Hot Test<br>Inductive Load                                                                                                                                                                                                                                                                                                                               | Product Test | Full Chip AC & DC Scan >98% Stuck Fault coverage<br>Code execution memory tests<br>Reliability Lookahead(ESD/ NVM/ HTOL/TV)<br>Burn-in Scan* & BIST                                                                              |

| Factory Driven                       | Continuos Improvement- Particle<br>Continuos Improvement- Defect Density<br>SPC- Process, Particles<br>SPC- Class Probe<br>SPC- Unit Probe<br>ISTAB- Process, Particles<br>ISTAB- Class Probe<br>Problem Solving- SD/ 5 Why's<br>Problem Solving- FMEA<br>Problem Solving- CAB<br>Maverick Prevention- Lot<br>Maverick Prevention- Lot<br>Maverick Prevention- Wafer BMY<br>Maverick Anamolous- Process, Particles | Pro          | Matrix CZ prior to launch & or 2nd tape out<br>Failure Analysis Capability<br>Smoke alarm / Volt storm<br>Top level simulation - mixed signal<br>Peer reviews<br>Analog HVST (SOA, inductive load, gate stress, bvd:             |

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008.

4

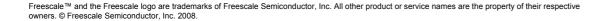

### Freescale TSPG ZD Approach

#### Institutionalize ZD elements as the foundation and add new learnings'

- Introduce 'Safe launch' process with the customer

- Continue to raise the ZD requirements every year for manufacturing

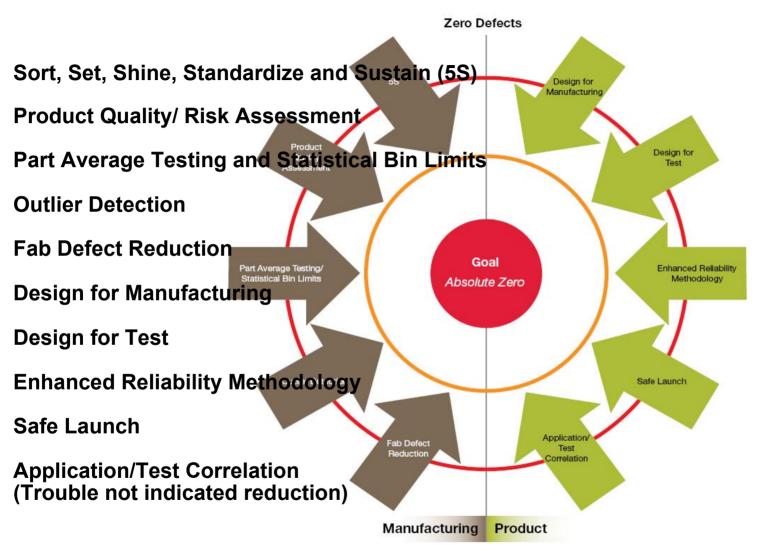

## What is the ZD Methodology in Freescale?

#### **Freescale Zero Defects Methodology**

## DFM in Freescale

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008.

### **Design for Manufacturability Strategy**

#### Freescale has invested substantially to advance DFM

A dedicated group is assigned to develop and aggressively deploy advanced techniques to impact our products

#### Target quality throughout the design lifecycle

- Standard cells are scored and corrected. Newer cells must ensure that area / quality is maximized

- SoC: Physical design flow is continuously updated to incorporate latest techniques nearly as transparently as possible

#### Continuously improve DTMS process

- DRC, DFM compliance are checked prior to tape-out

- Due diligence checks are added to ensure corrective actions have been successful

#### Drive the "Designed for Reality' initiative

• Close the gap between predicted and true product results

#### Occurrence of devices that Inability to print desired shapes due to physical fail to meet power and timing limitations of the litho process requirements Chemical & mechanical impacts of the mfg process on wafer/die planarity Model based parasitic extraction Statistical static timing analysis and optimization More intelligent margining Variation robust design **Original Design** Double-Cut Vias Inserted Design Chip Surface for Mfg

- Random particle induced opens & shorts

- Resistive vias & via opens • due to copper cladding and litho process

#### **DFM** Techniques

### SoC DFM Methodology by Technology

| Defect<br>Class | DFM Technique                       |                              | 0.35um<br>SMOS8,<br>CDR3 | 0.18/0.25um<br>25SGF,<br>LL18,<br>HiP6WRF | 0.13um<br>HiP7,<br>SMOS10 | 90nm<br>LP/GP,<br>NVM, RF,<br>SOI | 65nm<br>LP/GP | 45nm<br>LP/GP,<br>SOI |

|-----------------|-------------------------------------|------------------------------|--------------------------|-------------------------------------------|---------------------------|-----------------------------------|---------------|-----------------------|

| T               |                                     | Via                          | Recommend                | Required                                  | Required                  | Required                          | Required      | Required              |

| Random          | Optimization                        | Wire                         |                          |                                           | Required                  | Required                          | Required      | Required              |

| д               |                                     | Synthesis<br>for yield       |                          |                                           |                           | Recommend                         | Recommend     | Recommend             |

| Syste           | Timing Aware Tiling<br>(Metal Fill) |                              |                          |                                           |                           | Recommend                         | Recommend     | Recommend             |

| Systematic      | Model I<br>Lithography              |                              |                          |                                           |                           |                                   | Required      | Required              |

| Para            | Variation                           | SSTA                         |                          |                                           |                           |                                   |               | Pilot                 |

| Parametric      | Tolerant<br>Design                  | Model<br>based<br>extraction |                          |                                           |                           |                                   |               | Pilot                 |

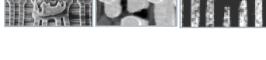

## Design-for-Test

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008.

### **Test Methodologies**

### Digital Logic

- Scan is dominant test method with SA fault coverage goal of >99%

- Scan test through I/O pads increases die area covered and through RAM increases coverage in RAM surrounding logic

- Inter clock domain scan increases transition fault coverage

- On-chip decompression / compression logic enables high parallel test and test pattern increase required for advanced fault models.

- Functional test patterns on top of scan

- Test basic functionality on module basis

- Covers what scan missed

- · Defect based tests IDDq, HVST

- Pseudo stuck at fault coverage

### SRAM and ROMs

- Memory BIST implemented for all SRAM and SDPRAM hard macros.

- Test Algorithms cover applicable Fault Models in SRAMs and SDPRAMs:

### **Test Methodologies**

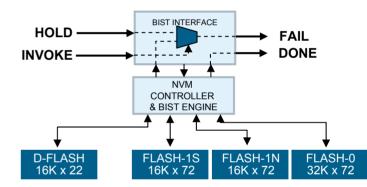

#### NVMBIST for Non-Volatile Memories

- Flexible, embedded test of NVM controlled via a dedicated test interface

- Next generation NVM BIST engine combines hard coded algorithm elements on chip in combination with pattern selectable features

- BIST serial scan chain loaded / unloaded via the 4 pin interface

- Benefits

- Highly parallel NVM test at Sort-1 (x16 already).

- Test all P-Flash and D-Flash blocks on a die in parallel.

- Provides means for easy test standardization/control

#### Analog

- Approach

- Test specification derived from electrical specification, test guide, and module characterization results

- Functional patterns/functional tests development according to test development process

- Test Quality

- Fault coverage achieved through functional coverage of tests

#### Example NVM BIST LL18

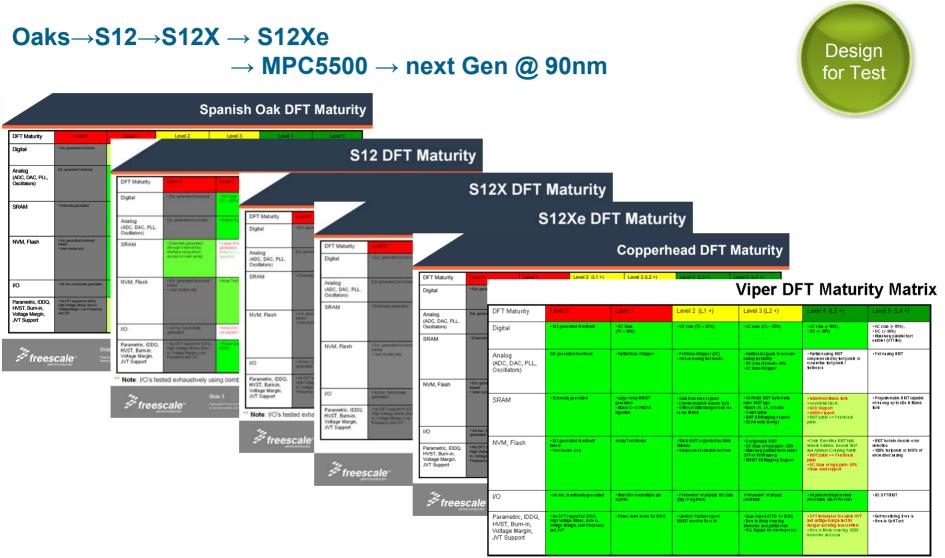

#### **DFT Maturity Matrix–Clear standard for Design-for-Test**

Design for Test

| DFT Maturity                                                             | Level 0                                                                                                  | Level 1                                                          | Level 2                                                                                                                                               | Level 3                                                                                                                                                                                   | Level 4                                                                                                                                                                                                  | Level 5                                                                                                                                                                                 |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital                                                                  | <ul> <li>Ext. generated<br/>functional</li> </ul>                                                        | • SAF > 90%                                                      | • SAF > 95%                                                                                                                                           | <ul> <li>SAF &gt; 98%</li> <li>Transition &gt;85%</li> <li>Path Delay &gt;= 200 out of 1000<br/>most critical</li> </ul>                                                                  | • Transition > 90%<br>• SAF > 99%                                                                                                                                                                        | <ul> <li>SAF &gt; 99.5%</li> <li>Transition &gt; 95%</li> <li>Bridge &gt; 70%</li> <li>70% SI CFs</li> <li>Massively parallel test<br/>enabler (UTI like)</li> </ul>                    |

| Analog<br>(ADC, DAC, PLL,<br>Oscillators)                                | Ext. generated<br>functional                                                                             | Partial Scan Wrapper                                             | <ul> <li>Full Scan Wrapper (DC)</li> <li>Ad-hoc analog test<br/>modes (based on<br/>designer intuition)</li> </ul>                                    | <ul> <li>Additional signals to increase<br/>analog testability</li> <li>DC scan stuck-at &gt; 95%</li> </ul>                                                                              | <ul> <li>Appropriate level of critical test<br/>points and test modes with<br/>Appropriate level of Analog<br/>BIST</li> <li>AC Scan Wrapper</li> </ul>                                                  | <ul> <li>Quantifiable boundary<br/>coverage &gt; 99%</li> <li>100% SAF &amp; 95%Transition<br/>testing of logic</li> <li>Structural test of analog</li> <li>Full Analog BIST</li> </ul> |

| SRAM                                                                     | Externally generated                                                                                     | Large Array<br>MBIST generated<br>March C- or<br>PMOVI algorithm | <ul> <li>Data Retention support</li> <li>Checkerboard &amp; Inverse<br/>tests</li> <li>Different data<br/>backgrounds run on the<br/>March</li> </ul> | <ul> <li>All RAMs BIST tested with same<br/>BIST type</li> <li>BIST March LR/LA better</li> <li>BIST X/Y fast addressing</li> <li>BIST Bit Mapping</li> <li>SCAN write through</li> </ul> | <ul> <li>Sep BIST for DP RAMS</li> <li>BIST Intra-Word Coverage</li> <li>BIST Any-bit-fast tests</li> <li>Cell Stability Test</li> <li>Cell Stress Test</li> <li>BIST paths &gt;= Func paths.</li> </ul> | <ul> <li>Programmable BIST capable<br/>of running up to 40+ N<br/>March tests</li> <li>In the Field BISR</li> </ul>                                                                     |

| ROM                                                                      | Externally generated                                                                                     | MBIST tested     100% SAF                                        | <ul> <li>100% AF (inc and dec addressing)</li> </ul>                                                                                                  | <ul> <li>BIST X/Y fast addressing</li> <li>MBIST Bit Mapping Support</li> <li>Scan read support</li> <li>BIST MISR Aliasing probability &lt;<br/>1PPM (&gt;= 20-bit MISR)</li> </ul>      | <ul> <li>BIST Any-bit-fast tests</li> <li>BIST paths &gt;= Functional paths.</li> <li>BIST MISR Aliasing probability</li> <li>&lt; 0.1PPM (&gt;=24-bit MISR)</li> </ul>                                  |                                                                                                                                                                                         |

| NVM, Flash                                                               | <ul> <li>Ext. generated<br/>functional based</li> <li>User modes only</li> </ul>                         | • Array Test Modes                                               | <ul> <li>Basic BIST supported by<br/>State Machine</li> <li>Independent erasable<br/>test row</li> </ul>                                              | <ul> <li>Configurable BIST</li> <li>DC Scan logic &gt; 98%</li> <li>Massively parallel test enabler<br/>(UTI or BDM based)</li> <li>MBIST Bit Mapping Support</li> </ul>                  | <ul> <li>Code Execution BIST that<br/>detects Address Decode SOF<br/>and Address Coupling Faults</li> <li>BIST paths &gt;= Functional paths</li> <li>DC Scan logic part &gt; 99%</li> </ul>              | <ul> <li>BIST include decode error<br/>detection</li> <li>100% testpoints or BISTs of<br/>embedded analog</li> <li>Scan read support</li> </ul>                                         |

| I/O                                                                      | <ul> <li>Ad hoc, functionally<br/>generated</li> </ul>                                                   | <ul> <li>Most I/Os<br/>controllable via<br/>register</li> </ul>  | <ul> <li>Full control* of all pads<br/>I/O state (jtag or<br/>registers)</li> </ul>                                                                   | <ul> <li>Full control* of all pad electricals</li> <li>High speed IO 2^^7-1 random<br/>sequence for BER (PRBS<br/>loopback to PRSA):</li> </ul>                                           | <ul> <li>All pad electrical controls<br/>observable via ATPG scan</li> </ul>                                                                                                                             | • I/O DFT/BIST                                                                                                                                                                          |

| Parametric,<br>IDDQ, HVST,<br>Burn-in, Voltage<br>Margin, JVT<br>Support | No DFT support for<br>IDDQ, High Voltage<br>Stress, Burn in,<br>Voltage Margin, Low<br>Frequency and JVT | Power down<br>mode for IDDQ                                      | Limited / Partial support     MBIST used for Burn IN                                                                                                  | <ul> <li>Scan based ATPG for IDDq</li> <li>Burn In Mode covering Memories<br/>and partial scan</li> <li>PLL Bypass for low frequency</li> </ul>                                           | <ul> <li>DFT techniques to enable HVT<br/>and voltage margin test for<br/>designs including level shifters</li> <li>Burn In Mode covering 100%<br/>memories and scan</li> </ul>                          | <ul> <li>Self monitoring Burn In</li> <li>Burn-in Self Test</li> </ul>                                                                                                                  |

### **Design For Test – Continuous Improvement**

### **Planned DFT Maturity for New NPIs**

| DFT Maturity                                                                | Level 0                                                                                                                                  | Level 1                                                                                      | Level 2                                                                                                                                                   | Level 3                                                                                                                                                                                   | Level 4                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital                                                                     | <ul> <li>Ext. generated<br/>functional</li> </ul>                                                                                        | • SAF > 90%                                                                                  | • SAF > 95%                                                                                                                                               | <ul> <li>Transition &gt;85%</li> <li>Path Delay &gt;= 200 out of<br/>1000 most critical</li> </ul>                                                                                        | <ul> <li>Transition &gt; 90%</li> <li>SAF &gt; 99%</li> <li>Bridge &gt; 80%</li> <li>Small-delay defect coverage</li> <li>Selective path-delay testing</li> </ul>                                                                                                                                                      |

| Analog<br>(ADC, DAC,PLL,<br>Oscillators)                                    | <ul> <li>Ext. generated<br/>functional</li> </ul>                                                                                        | <ul> <li>Partial Scan<br/>Wrapper</li> </ul>                                                 | <ul> <li>Full Scan Wrapper<br/>(DC)</li> <li>Ad-hoc analog test<br/>modes (based on<br/>designer intuition)</li> </ul>                                    | <ul> <li>Additional signals to<br/>increase analog testability</li> <li>DC scan stuck-at &gt; 95%</li> <li>AC Scan Wrapper if module<br/>running near Fsys.</li> </ul>                    | <ul> <li>Partial Analog BIST and/or<br/>critical test points (tool<br/>determined test points)</li> </ul>                                                                                                                                                                                                              |

| SRAM                                                                        | <ul> <li>Externally<br/>generated</li> </ul>                                                                                             | <ul> <li>Large Array MBIST<br/>generated</li> <li>March C- or PMOVI<br/>algorithm</li> </ul> | <ul> <li>Data Retention<br/>support</li> <li>Checkerboard &amp;<br/>Inverse tests</li> <li>Different data<br/>backgrounds run on<br/>the March</li> </ul> | <ul> <li>All RAMs BIST tested with<br/>same BIST type</li> <li>BIST March LR/LA better</li> <li>BIST X/Y fast addressing</li> <li>BIST Bit Mapping</li> <li>SCAN write through</li> </ul> | <ul> <li>Programmable BIST based on<br/>14N coverage</li> <li>Sep BIST for DP RAMS</li> <li>BIST Intra-Word Coverage</li> <li>BIST Any-bit-fast tests</li> <li>SDD BIST Support **</li> <li>LWSH BIST support **</li> <li>BIST paths &gt;= Func paths.</li> <li>** - Only required if RAM has<br/>test mode</li> </ul> |

| NVM, Flash                                                                  | <ul> <li>Ext. generated<br/>functional based</li> <li>User modes<br/>only</li> </ul>                                                     | Array Test Modes                                                                             | <ul> <li>Basic BIST<br/>supported by State<br/>Machine</li> <li>Independent<br/>erasable test row</li> </ul>                                              | <ul> <li>Configurable BIST</li> <li>DC Scan logic &gt; 98%</li> <li>Massively parallel test<br/>enabler (UTI or BDM based)</li> <li>MBIST Bit Mapping Support</li> </ul>                  | <ul> <li>Code Execution BIST that<br/>detects Address Decode SOF<br/>and Address Coupling Faults</li> <li>BIST paths &gt;= Functional paths</li> <li>DC Scan logic part &gt; 99%</li> <li>Transition delay on logic &gt; 85%</li> </ul>                                                                                |

| I/O                                                                         | <ul> <li>Ad hoc,<br/>functionally<br/>generated</li> </ul>                                                                               | <ul> <li>Most I/Os<br/>controllable via<br/>register</li> </ul>                              | <ul> <li>Full control* of all<br/>pads I/O state (jtag<br/>or registers)</li> </ul>                                                                       | Full control* of all pad electricals                                                                                                                                                      | All pad electrical controls     observable via ATPG scan                                                                                                                                                                                                                                                               |

| Parametric,<br>IDDQ,<br>HVST,Burn-<br>in, Voltage<br>Margin, JVT<br>Support | <ul> <li>No DFT support<br/>for IDDQ, High<br/>Voltage Stress,<br/>Burn in, Voltage<br/>Margin, Low<br/>Frequency and<br/>JVT</li> </ul> | Power down mode<br>for IDDQ                                                                  | <ul> <li>Limited / Partial<br/>support</li> <li>MBIST used for Burn<br/>IN</li> </ul>                                                                     | <ul> <li>Scan based ATPG for IDDq</li> <li>Burn In Mode covering<br/>Memories and partial scan</li> <li>PLL Bypass for low<br/>frequency</li> </ul>                                       | <ul> <li>DFT techniques to enable HVT<br/>and voltage margin test for<br/>designs including level shifters</li> <li>Burn In Mode covering 100%<br/>memories and scan</li> </ul>                                                                                                                                        |

### Ongoing

- FSL uses best-in-class Design-for-Test technology, test engineering processes to proactively enable Zero Defect Quality for NPIs.

- Statistical analysis through volume diagnosis ensures efficiency of institutionalized methods and enables further improvements through 'lessons learned'.

- FSL working with leading EDA vendors and universities and investing in research for new DFT technology:

- New Fault Models to better model silicon defects:

- Bridging Fault Model (statistical and layout based)

- Timing Aware ATPG Small Delay Defects

- Opens Defects

- New DFT architectures:

- Field Programmable BIST for SRAMs

- Core Self Test for Safety Critical applications

- New technology is integrated into DFT Maturity Matrix as standard best practice and rolled out world wide.

## Manufacturing & Continuous Improvement

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008.

### **Zero Defects Methods in Manufacturing**

- Manufacturing uses a structured approach to institutionalize zero defect elements

- Die and Final Manufacturing SPC programs and specification limits identify rogue product & processes

- Specification limits are used as the gauge to determine if product is fit for use.

- Capability (CpK) studies are performed monthly on various inline process and class probe parameters

- Advanced Intelligent Manufacturing techniques such 'input controls' and Fault Detection Control are being deployed

|                                      | ZD Elements                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Product<br>Zero Defect<br>Program    | JVT<br>VCT/HVST<br>Iddq<br>Test Coverage (AEC Spec)<br>Lessons learned Look Across<br>Standardized NVM test methods<br>Burn-In<br>WebDSS CQI Entry                                                                                                                                                                                                                                                                                                 | Containment<br>Safe Launch<br>Process |

| Manufacturing Zero<br>Defect Program | PAT (Unit Probe)<br>BMY<br>SBL Phase1<br>SBL Phase 2                                                                                                                                                                                                                                                                                                                                                                                               | Tiocess                               |

| Division Specific<br>Elements        | PAT (Final Test)<br>Gate Stress<br>100% Cold Test<br>100% Hot Test<br>Inductive Load                                                                                                                                                                                                                                                                                                                                                               |                                       |

| Factory Driven                       | Continuos Improvement- Particle<br>Continuos Improvement- Defect Density<br>SPC- Process, Particles<br>SPC- Class Probe<br>SPC- Unit Probe<br>ISTAB- Process, Particles<br>ISTAB- Class Probe<br>Problem Solving- 8D/ 5 Why's<br>Problem Solving- FMEA<br>Problem Solving- FMEA<br>Problem Solving- CAB<br>Maverick Prevention- Lot<br>Maverick Prevention- Wafer BMY<br>Maverick Anamolous- Process, Particles<br>Maverick Anamolous- Class Probe | Mfg<br>Discipline                     |

### **Zero Defects: Continuous Improvement**

### Safe Launch Plan Template

- The Safe Launch Template defines elements to be reviewed

- 1. Information Overview

- Goal, Team, Module info, Part info

- 2. Shipment Plan Review

- 3. IC Manufacturing Review

- 4. Module Design Review

- 5. Module Manufacturing Review

- 6. Failure Analysis Plan Review

- 7. Returns History Review

- 8. Risk Assessment

- Actions items are captured and tracked within each section

#### **Freescale Zero Defects Methodology**

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008.

####

## Results

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008.

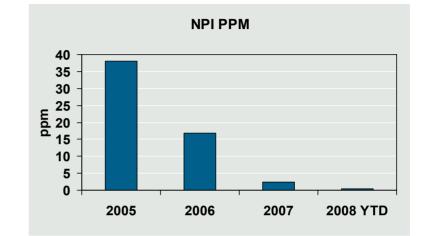

### **New Product Launch PPM**

#### ► Launch PPM

First unit shipped through 100K units shipped, plus six months

### Improving Launch PPM through:

- Design for Zero Defect Methodology

- Improved Test Maturity Prior to Launch

- Manufacturing

- Safe Launch Partnerships

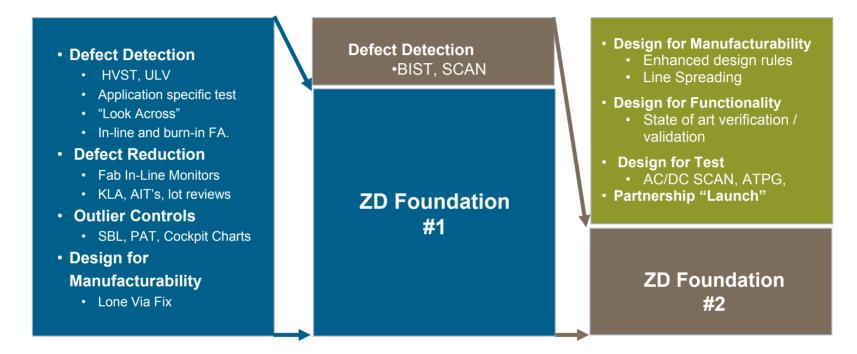

### **Microcontroller History**

### **Microcontroller Zero-Defect Strategy**

| 19                                           | <b>aks</b><br>996 design                                           | <b>S12</b><br>2000 design<br><10 ppm capability<br>Q4'07 ~ 5.0 ppm | eSYS<br>2003 design<br><1 ppm capability                                                                                                                                                    | <b>C90</b><br>2008 design<br><1 ppm capability                                                                                                                                 |

|----------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design f     Manufac                         | 0 ppm capability<br>Q07 ~10 ppm<br>for<br>cturability<br>e Via Fix | <ul> <li>Defect Detection</li> <li>BIST, SCAN</li> </ul>           | <ul> <li>Design for Manufacturability</li> <li>Enhanced design rules</li> <li>Line spreading</li> <li>Design for Functionality</li> <li>State of art<br/>verification/validation</li> </ul> | <ul> <li>4th Cycle of Zero<br/>Defect Learning</li> <li>Enhanced tools<br/>and processes improve<br/>maturity of our DFx<br/>capabilities.</li> <li>Design for Test</li> </ul> |

| •Applic<br>•"Look<br>•In-line<br>• Outlier ( | Γ, ULV<br>cation specific test<br>cacross"<br>e and burn-in FA     | <ul> <li>Zero Defects Foundation</li> </ul>                        | <ul> <li>Design for Test</li> <li>AC/DC SCAN,<br/>ATPG, IDDQ</li> <li>Partnership "Launch"</li> </ul>                                                                                       | <ul> <li>Design for<br/>Manufacturability</li> <li>Design for<br/>Functionality</li> <li>Design for<br/>Failure analysis</li> </ul>                                            |

| <ul> <li>Defect F</li> <li>Fab</li> </ul>    | Reduction<br>in-line monitors<br>, AIT's, lot reviews              |                                                                    | <ul> <li>Zero Defects Foundation</li> </ul>                                                                                                                                                 | Zero Defect Foundation                                                                                                                                                         |

|                                              |                                                                    |                                                                    |                                                                                                                                                                                             | 14 A A A A A A A A A A A A A A A A A A A                                                                                                                                       |

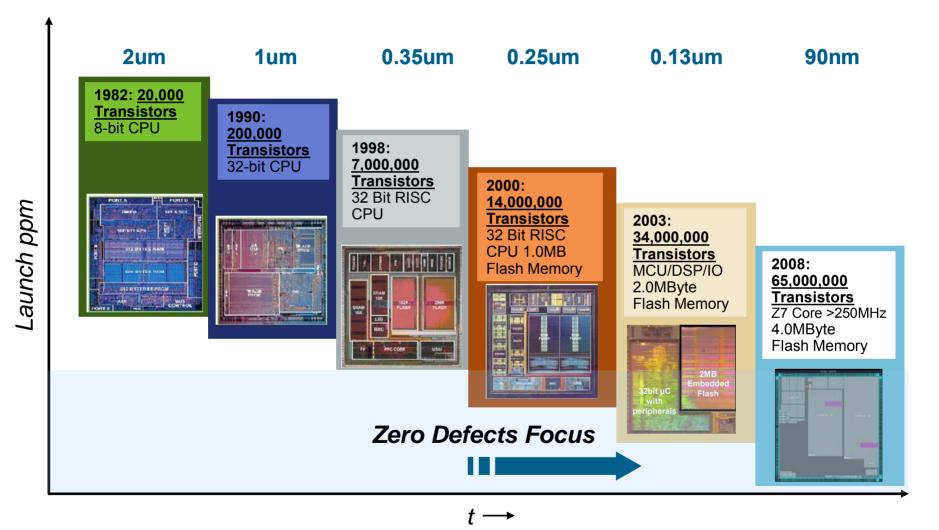

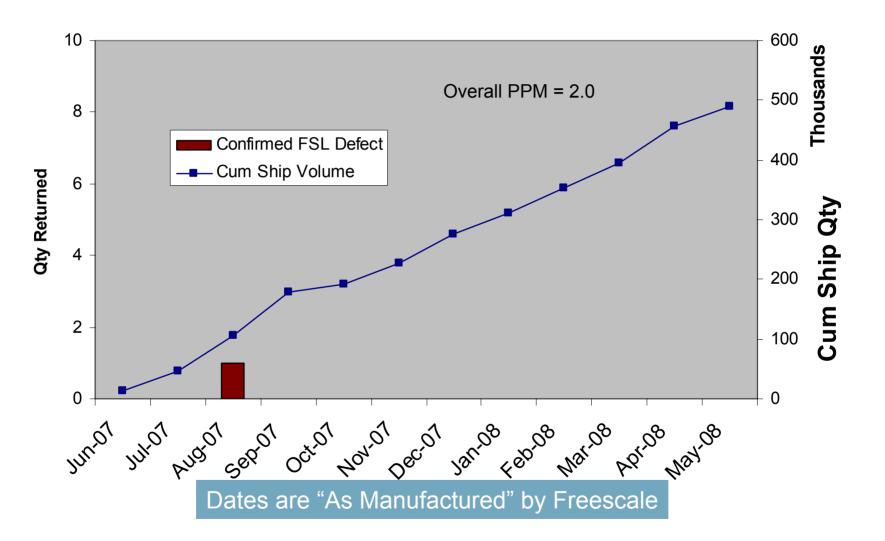

### **Copperhead PPM Trend**

Dates are "As Manufactured" by Freescale

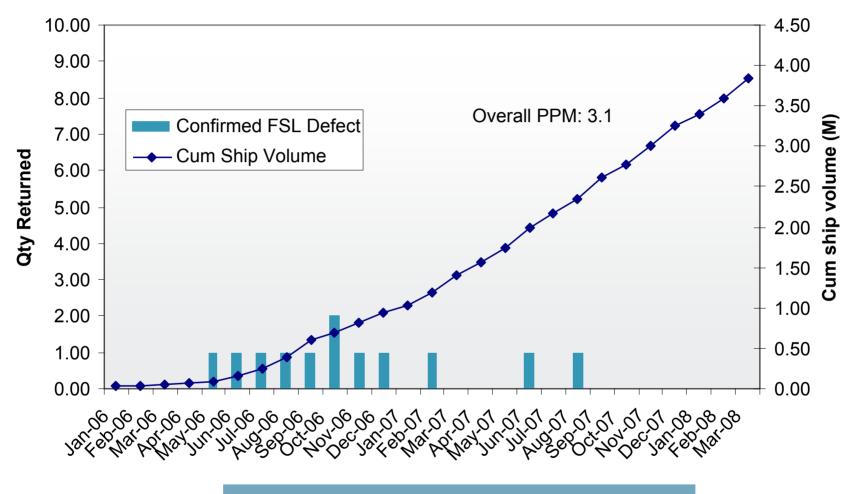

## IMX31 Auto 27x27mm PPM Trend

### **Freescale Zero Defects Summary**

# Moving Forward on this Journey

## Challenges for Semiconductor Reliability in the Automotive Industry

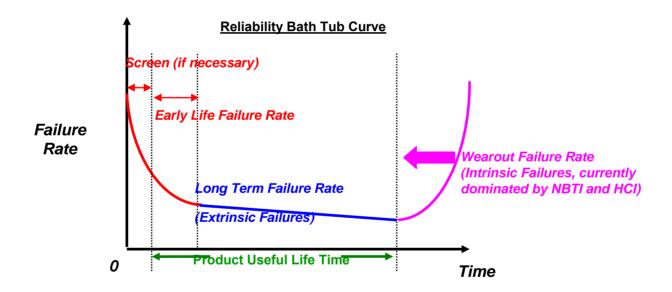

As technology advances, gate oxides and transistor channel lengths are shrunk at a faster rate than voltage is decreased, and material compositions are changing (nitrogen content in oxides, etc.); thus, the wear out portion of the curve generally shifts to the left.

Intrinsic reliability lifetimes of new technologies are now on the order of expected product use times in the field.

#### **Advanced CMOS Intrinsic Wearout Mechanisms**

Dominant intrinsic reliability failure mechanisms in advanced CMOS technologies are <u>Negative Bias Temperature Instability</u> (NBTI) and <u>Hot Carrier Injection</u> (HCI) which cause parametric shifts with some distribution, instead of hard failures.

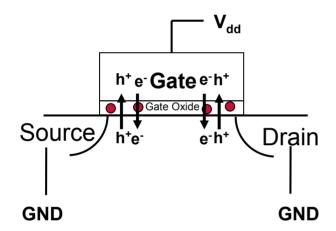

#### **Negative Bias Temperature Instability (NBTI):**

#### **Physical Mechanism:**

• Electrons/holes that tunnel across the gate oxide create energetic positive charges that damage or get trapped in the gate oxide.

#### Effect:

- Primarily an increase in Vt due to trapped charges.

- Occurs in PMOS only.

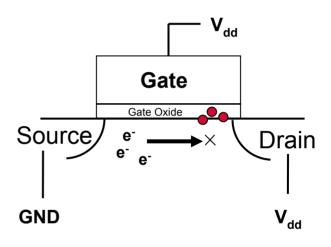

#### Hot Carrier Injection (HCI):

#### **Physical Mechanism:**

- Electrons/Holes scatter as they go from source to drain.

- Damaging the interface and oxide.

#### Effect:

- Reduction of mobility (conductance) of the transistor.

- Change in Vt due to charge build-up in oxide.

- Occurs in both NMOS and PMOS

## Performance Shift Mitigation Activities at Freescale

#### 1) Life Test Simulation Optimization

Life Test stress conditions (voltage, temperature) are optimized to ensure AEC required stress time simulates expected field-use time.

#### 2) Life Test Shift Analysis

Critical AC/DC parameters are measured before and after required life test to check for general shifts due to extrinsic or intrinsic failure mechanisms.

#### 3) Intrinsic Reliability Shift Analysis

Required for products in CMOS090 and newer technologies. The general procedure is as follows:

- a) Measure performance before and after life test, preferably at a readpoint that simulates expected field-use time assuming the <u>NBTI</u> failure mechanism (may be different readpoint than (1))

- b) Extrapolate life test performance shifts to expected field shifts, based on NBTI models developed during intrinsic reliability testing. Control sample data is taken into account at this step.

- c) Add HCI effects based on NBTI versus HCI shifts observed during intrinsic reliability testing, since HCI effects are not generally observed during low frequency life testing.

- d) Create product test guardbands based on statistical distribution of normalized shifts.

## Performance Robustness Validation Activities Moving Forward

#### 1) Split Lot Analysis

Performance data is being taken on nominal versus slow PMOS transistor lots to check which patterns may be affected by NBTI. Split lot results will be checked against life test results to determine correlation.

#### 2) Aging Simulation in Design

Aged transistor models are being input to design simulation tools and performance estimates checked against split lot and life test results.

#### 3) Test Vehicle Evaluations

Stress ring oscillators and other test circuits are being stressed in parallel to device stresses to check for shift correlation.

### **Performance Shifts for Automotive Products**

- At this time, performance shift concerns are minimal for Automotive devices, since they generally lag in technology and do not push performance limits.

- To minimize future risks and to assure Zero Defects for Automotive devices in advanced technologies, proactive steps are being taken to understand, minimize, and mitigate risks of performance shifts. Advanced reliability robustness validation techniques will be applied.

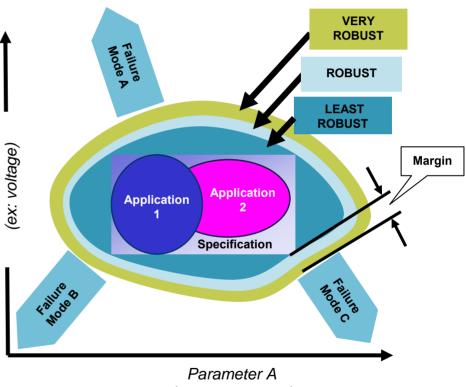

### **Robustness Validation**

There are several techniques under evaluation in Freescale to understand Die, Die / Package, and Package wear out mechanisms

- ESD testing at multiple voltages followed by Operation Life studied to determine failure curves

- Test intrinsic silicon mechanisms to failure

- Extend traditional package level stresses to failure

#### ZVEI Robustness Validation Diagram

(ex: temperature)

Parameter B

## It's Impossible. Zero=Zero.

- Freescale is committed to Zero Defects for Automotive

- Proven commitment to Drive Quality Improvement

- Demonstrated the Ability to Launch Products at Zero Defect Levels

- Continue to Develop and Implement New Zero Defect Strategies on Next Generation Products

### **Related Session Resources**

#### **Session Location – Online Literature Library**

http://www.freescale.com/webapp/sps/site/homepage.jsp?nodeId=052577903644CB

#### **Sessions**

| Session ID | Title |      |      |      |

|------------|-------|------|------|------|

|            |       |      |      |      |

|            |       | <br> | <br> | <br> |

|            |       | <br> | <br> | <br> |

|            |       |      |      |      |

#### Demos

| Pedestal ID | Demo Title |

|-------------|------------|

|             |            |

|             |            |

|             |            |