# Virtex-5 系列概述 LX、LXT 和 SXT 平台

DS100 (v3.0) 2007 年 2 月 2 日

#### 先期产品技术说明

### 概述

Virtex™-5 系列提供 FPGA 市场中最新最强大的功能。Virtex-5 系列采用第二代 ASMBL™(高级硅片组合模块)列式架构,包含四种截然不同的平台(子系列),比此前任何 FPGA 系列提供的选择范围都大。每种平台都包含不同的功能配比,以满足诸多高级逻辑设计的需求。本概述包含关于 LX、LXT 和 SXT 平台的详细信息。除了最先进的高性能逻辑架构,Virtex-5 FPGA 还包含多种硬 IP 系统级模块,包括强大的 36Kb Block RAM/FIFO、第二代 25 x 18 DSP Slice、带有内置数控阻抗的 SelectIO™ 技术、ChipSync™ 源同步接口模块、系统监视器功能、带有集成 DCM(数字时钟管理器)和锁相环 (PLL) 时钟发生器的增强型时钟管理模块以及高级配置选项。LXT 和 SXT 器件还包含针对增强型串行连接的电源优化高速串行收发器模块、一个符合 PCI Express™ 的集成端点模块和三态以太网 MAC(媒体访问控制器)。这些功能使高级逻辑设计人员能够在其基于 FPGA 的系统中体现最高档次的性能和功能。Virtex-5 FPGA 以最先进的 65nm 铜工艺技术为基础,是定制 ASIC 技术的可编程替代方案。大多数高级系统设计都需要 FPGA 的可编程能力。Virtex-5 FPGA 以前所未有的逻辑、DSP、软 / 硬微处理器和连接功能提供最佳解决方案,以满足高性能逻辑设计人员、高性能 DSP 设计人员和高性能嵌入式系统设计人员的需求。Virtex-5 LXT、SXT 和 FXT 平台具有先进的高速串行连接功能和链路 / 事务层功能。

## Virtex-5 特性提要

- LX、LXT、SXT 和 FXT 四个平台

- Virtex-5 LX: 高性能通用逻辑应用

- Virtex-5 LXT: 具有高级串行连接功能的高性能逻辑

- Virtex-5 SXT: 高性能信号处理应用

- Virtex-5 FXT: 高性能嵌入式系统

- 跨平台兼容性

- LXT、SXT 和 FXT 器件在相同封装中的占用空间兼容

- 最先进的最佳利用率高性能 FPGA 架构

- 真 6 输入查找表 (LUT) 技术

- 双 5-LUT 选项

- 改进的布线减少了中间连线

- 64 位分布式 RAM 选项

- SRL32/ 双 SRL16 选项

- 强大的时钟管理模块 (CMT) 时钟控制

- 具有零延迟缓冲、频率综合和时钟相移功能的数字时钟管理器模块

- 具有输入抖动滤波、零延迟缓冲、频率综合和相位匹配时 钟分频功能的 PLL 模块

- 36Kb Block RAM/FIFO

- 真双端口 RAM 模块

- 增强的可选可编程 FIFO 逻辑

- 可编程

- · 高达 36 位的真正双端口宽度

- · 高达 72 位的简单双端口宽度

- 内置可选纠错电路

- 可选择将每个模块作为两个独立的 18Kb 模块进行编程

- 65nm 铜 CMOS 工艺技术

- 1.0V 核电压

- 可选择标准或无铅的具有高度信号完整性的倒装芯片 封装

- 高性能并行 SelectIO 技术

- 1.2 到 3.3V I/O 运行

- 使用 ChipSync 技术的源同步接口连接

- 数控阻抗 (DCI) 有效终端

- 灵活的细粒度 I/O 分组

- 支持高速存储器接口

- · 高级 DSP48E Slice

- 25x18 补数乘法运算

- 可选加法器、减法器和累加器

- 可选流水线功能

- 可选位宽逻辑功能

- 专用的级联连接

- 灵活的配置选项

- SPI 和并行 FLASH 接口

- 专用的回读重新配置逻辑,可支持多比特流

- 自动总线宽度检测功能

- 用于 PCI Express (LXT/SXT) 的集成端点模块

- 符合 PCI Express 基础规范 (PCI Express Base Specification) 1.1

- 每模块支持 1 倍、2 倍、4 倍或 8 倍通道宽度

- 与 RocketIO™ 收发器配合使用

- 三态 10/100/1000 Mb/s 以太网 MAC (LXT/SXT)

- 可以将 RocketlO 收发器用作 PHY,也可以用多种软 MII (媒体独立接口)方案将其连接到外部 PHY

- 100 Mb/s 到 3.2 Gb/s 的 RocketIO GTP 收发器 (LXT/SXT)

- 所有器件都有系统监视功能

- 片上/片外热特性监视

- 片上/片外电源监视

- 通过 JTAG 端口访问所有监视量

© 2006 - 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. PowerPC is a trademark of IBM, Inc. All other trademarks are the property of their respective owners. All specifications are subject to change without notice.

#### 表 1: Virtex-5 FPGA 系列成员

| 器件         | 可配置逻辑块<br>(CLB) |                                   |                       | DSP48E               | Block RAM 模块         |       |         |                    | PCI Express | 以太网        | RocketIO GTP       | I/O 组 | 最大                         |

|------------|-----------------|-----------------------------------|-----------------------|----------------------|----------------------|-------|---------|--------------------|-------------|------------|--------------------|-------|----------------------------|

|            | 阵列<br>(行×列)     | Virtex- 5<br>Slice <sup>(1)</sup> | 最大<br>分布式<br>RAM (Kb) | Slice <sup>(2)</sup> | 18 Kb <sup>(3)</sup> | 36 Kb | 最大 (Kb) | CMT <sup>(4)</sup> | 端点模块        | MAC 模<br>块 | 收发器 <sup>(5)</sup> | 总数    | 用户<br>I/O 数 <sup>(6)</sup> |

| XC5VLX30   | 80 x 30         | 4,800                             | 320                   | 32                   | 64                   | 32    | 1,152   | 2                  | 无           | 无          | 无                  | 13    | 400                        |

| XC5VLX50   | 120 x 30        | 7,200                             | 480                   | 48                   | 96                   | 48    | 1,728   | 6                  | 无           | 无          | 无                  | 17    | 560                        |

| XC5VLX85   | 120 x 54        | 12,960                            | 840                   | 48                   | 192                  | 96    | 3,456   | 6                  | 无           | 无          | 无                  | 17    | 560                        |

| XC5VLX110  | 160 x 54        | 17,280                            | 1,120                 | 64                   | 256                  | 128   | 4,608   | 6                  | 无           | 无          | 无                  | 23    | 800                        |

| XC5VLX220  | 160 x 108       | 34,560                            | 2,280                 | 128                  | 384                  | 192   | 6,912   | 6                  | 无           | 无          | 无                  | 23    | 800                        |

| XC5VLX330  | 240 x 108       | 51,840                            | 3,420                 | 192                  | 576                  | 288   | 10,368  | 6                  | 无           | 无          | 无                  | 33    | 1,200                      |

| XC5VLX30T  | 80 x 30         | 4,800                             | 320                   | 32                   | 72                   | 36    | 1,296   | 2                  | 1           | 4          | 8                  | 12    | 360                        |

| XC5VLX50T  | 120 x 30        | 7,200                             | 480                   | 48                   | 120                  | 60    | 2,160   | 6                  | 1           | 4          | 12                 | 15    | 480                        |

| XC5VLX85T  | 120 x 54        | 12,960                            | 840                   | 48                   | 216                  | 108   | 3,888   | 6                  | 1           | 4          | 12                 | 15    | 480                        |

| XC5VLX110T | 160 x 54        | 17,280                            | 1,120                 | 64                   | 296                  | 148   | 5,328   | 6                  | 1           | 4          | 16                 | 20    | 680                        |

| XC5VLX220T | 160 x 108       | 34,560                            | 2,280                 | 128                  | 424                  | 212   | 7,632   | 6                  | 1           | 4          | 16                 | 20    | 680                        |

| XC5VLX330T | 240 x 108       | 51,840                            | 3,420                 | 192                  | 648                  | 324   | 11,664  | 6                  | 1           | 4          | 24                 | 27    | 960                        |

| XC5VSX35T  | 80 x 34         | 5,440                             | 520                   | 192                  | 168                  | 84    | 3,024   | 2                  | 1           | 4          | 8                  | 12    | 360                        |

| XC5VSX50T  | 120 x 34        | 8,160                             | 780                   | 288                  | 264                  | 132   | 4,752   | 6                  | 1           | 4          | 12                 | 15    | 480                        |

| XC5VSX95T  | 160 x 46        | 14,720                            | 1,520                 | 640                  | 488                  | 244   | 8,784   | 6                  | 1           | 4          | 16                 | 19    | 640                        |

#### 注:

- Virtex-5 Slice 的组织方式与前几代不同。每个 Virtex-5 Slice 包含四个 LUT 和四个触发器(以前是两个 LUT 和两个触发器)。每个 DSP 48E 包含一个 25 x 18 位乘法器、一个加法器和一个累加器。 Virtex-5 Block RAM 的基本容量为 36 Kb。每个模块也可用作两个独立的 18Kb 模块。

- 每个时钟管理模块 (CMT) 包含两个 DCM 和一个 PLL。

- RocketIO GTP 收发器的设计运行速度为 100 Mb/s 到 3.2 Gb/s。

- 此数字不包括 RocketIO 收发器。

# Virtex-5 逻辑架构

- 高达 50% 的速度提升

- 与 Virtex-4 器件相比,平均提升一到两个速度级别

- 可级联的 32 位变量移位寄存器或 64 位分布式存储器功

- 优异的布线架构,增强了对角线方向的布线支持,模块 与模块连接使用中间连线极少

- 多达 330,000 个逻辑单元,包括:

- 多达 207,360 个具有时钟使能的内部架构触发器 (XC5VLX330)

- 多达 207,360 个真 6 输入 LUT, 总 LUT 位数大于 1300万

- 两个双 5-LUT 模式输出提高了利用率

- 逻辑扩展多路复用器和 I/O 寄存器

# 550 MHz 时钟技术

- 多达六个时钟管理模块 (CMT)

- 每个 CMT 包含两个 DCM 和一个 PLL/PMCD 时 钟发生器总数多达 18 个

- 灵活的 DCM 对 PLL 或 PLL 对 DCM 级联

- 精密时钟去歪斜和相移

- 灵活的频率综合

- 多种运行模式,便于性能权衡决策

- 提高了输入/输出频率上限

- 细粒度相移分辨率

- 输入抖动滤波

- 低功耗运行

- 相移范围大

- 相位匹配时钟分频器 (PMCD) 功能

- 可实现优化低抖动时钟和精确占空比的差分时钟树结构

- 32 个全局时钟网络

- 除了全局时钟,还有局部时钟、I/O 时钟和本地时钟

## 550 MHz 集成块存储器

- LXT 平台的集成模块存储器容量高达 11.6 Mb

- 带有可选双 18Kb 模式的 36Kb 模块

- 真双端口 RAM 单元

- 独立的端口宽度选择 (1位宽到72位宽)

- 对于真双端口运行,每端口宽度可达 36 位宽

- 对于简单双端口运行 (一个读端口和一个写端口),每端口宽度可达 72 位宽

- 9 位、18 位、36 位和72 位宽度的存储器位数及奇偶校验/边带存储器支持

- 从 32K x 1 到 512 x 72 的配置(8K x 4 到 512 x 72 用 于 FIFO 运行)

- 多采样率 FIFO 支持逻辑

- 具有完全可编程近满标志和近空标志的满标志和空标志

- 同步 FIFO 支持,没有标志不确定的问题

- 用于提高性能的可选流水线级数

- 字节写功能

- 专用级联布线,无需 FPGA 布线即可形成 64K x 1 存储器

- 满足高可靠性存储器要求的集成可选 ECC

- 针对 18 Kb (及以下)运行的特殊降功耗设计

#### 550 MHz DSP48E Slice

- 25 x 18 补数乘法运算

- 用于增强性能的可选流水线级数

- 用于乘法累加 (MACC) 运算的可选 48 位累加器,可选 择将累加器级联为 96 位

- 用于复数乘法运算或乘加运算的集成加法器

- 可选按位逻辑运行模式

- 每 Slice 独立 C 寄存器

- 在一个 DSP 列中完全可级联,无需外部布线资源

# SelectIO 技术

- 多达 1,200 个用户 I/O

- 广泛的 I/O 标准选择范围: 从 1.2V 到 3.3V

- 极高的性能

- 高达 800 Mb/s 的 HSTL 和 SSTL (在所有单端 I/O F)

- 高达 1.25 Gb/s LVDS (在所有差分 I/O 对上)

- 真差分片上终端

- 输入和输出 I/O 同边沿采集

- 广泛的存储器接口支持

## 65 nm 铜 CMOS 工艺

- 1.0V 核电压

- 12 层金属提供最强的布线功能,并可容纳硬 IP 植入

- 确实可减少静态功耗的三栅极氧化层技术

# ChipSync 源同步接口逻辑

- 与 SelectlO 技术配合使用, 简化源同步接口

- 所有 I/O 模块均内置逐比特去歪斜功能 (所有输入和输出上的可变延迟线)

- 专用的 I/O 和区域时钟资源 (引脚和时钟树)

- 所有 I/O 均内置数据串行器/解串器逻辑,具有相应的时 钟分频器支持

- 速度高达 1.25 Gb/s 的网络 / 电信接口

## 数控阻抗 (DCI) 有效的 I/O 终端

- 可选串行或并行终端

- 温度和电压补偿

- 大幅度简化电路板布局

- 减少电阻器

- 在理想的位置设置终端,可以在信号源或信号终点

#### 配置

- 支持 Platform Flash 配置、标准 SPI Flash 配置或标准 并行 NOR Flash 配置

- 专用的回读重新配置逻辑,可支持比特流

- 256 位 AES 比特流解密,可保护知识产权并防止复制设计

- 改进的比特流检错/纠错功能

- 自动总线宽度检测功能

- 通过 ICAP 端口进行部分重配置

## 系统监视器

- 片上温度测量 (±4°C)

- 片上电源测量 (±1%)

- 易用性和自包含性

- 基本运行无需设计

- 所有片上传感器自行监视

- 片上传感器的用户可编程报警阀值

- 用户可访问的 10 位 200kSPS ADC

- 偏移和增益误差的自动校准

- DNL = ±0.9 LSB 最大

- 可支持多达 17 个外部模拟输入通道

- 输入范围为 OV 到 1V

- 监视外部传感器,如电压、温度

- 通用模拟输入

- 可以通过架构或 JTAG TAP 全面访问系统监视器

- 在 FPGA 配置之前和器件断电期间完全可运行 (仅通过 JTAG TAP 访问)

# 先进的倒装芯片封装

- 确实可实现优异信号完整性的预制封装技术

- 尽量减少信号到返回之间的感应环路

- 最佳信号与 PWR/GND 比

- 将 SSO 感应噪声降低到 1/7

- 无铅封装与标准封装

# 针对 LXT 和 SXT 器件的系统模块

### 与 PCI Express 兼容的集成端点模块

- 与 RocketIO GTP 收发器配合使用,在尽量少用 FPGA 逻辑的情况下提供全面的 PCI Express 端点功能。

- 符合 PCI Express 基础规范 1.1

- PCI Express 端点模块或传统 PCI Express 端点模块

- 8 倍、4 倍、2 倍或 1 倍通道宽度

- 电源管理支持

- 用 Block RAM 作缓冲

- 完全缓冲式发送与接收

- 访问 PCI Express 配置空间和内部配置的管理界面

- 全程支持最大有效载荷 (128 字节到 4096 字节)

- 最多两条虚拟通道 (VC)

- 循环、加权循环或严格优先级 VC 仲裁

- 最多 6 x 32 位或 3 x 64 位 BAR (或 32 位和 64 位组合)

## 三态以太网媒体访问控制器

- 符合 IEEE 802.3

- 以 10、100 和 1,000 Mb/s 运行

- 支持三态自动协商

- 接收地址滤波器 (5条地址)

- 使用 RocketIO GTP 的全单片 1000Base-X 解决方案

- 通过软逻辑和 SelectIO 资源支持多个外部 PHY 连接 (MII、GMII 等)接口

- 使用软逻辑和 RocketIO GTP 收发器通过 SGMII 支持对 外部 PHY 器件的连接

- 通过独立接口接收和发送可用统计数据

- 独立的主机和客户端接口

- 支持巨型帧

- 灵活的用户可配置主机接口

#### RocketIO GTP 收发器

- 具有 100 Mb/s 到 3.2 Gb/s 波特率能力的全双工串行收 发器

- 8B/10B、用户定义 FPGA 逻辑或无编码选项

- 支持通道绑定

- CRC 生成和检查

- 发射器可编程预加重或预均衡

- 可编程终端和电压摆幅

- 接收器可编程均衡

- 可选接收器片上 AC 耦合

- 接收器信号检测与信号丢失指示器

- 可用二级配置总线进行用户动态再配置

- 带外 (OOB) 支持串行 ATA (SATA)

- 电气闲置、信标、接收器检测以及 PCI Express 和 SATA 扩频时钟支持

- 小于 100 mW 的典型功耗

- 内置 PRBS 发生器和校验器

## 架构描述

### Virtex-5 阵列概述

Virtex-5 器件是用户可编程的门阵列,具有针对高密度和高性能系统设计优化的各种可配置元件和嵌入式核。Virtex-5 器件可实现以下功能:

- I/O 块提供连接封装引脚和内部可配置逻辑的接口。可配置 I/O 块 (IOB) 支持大多数流行的前沿 I/O 标准。可将 IOB 连接到非常灵活的 ChipSync 逻辑,以增强源同步接口连接。源同步优化,包括逐比特去歪斜(对于输入和输出信号)、数据串行器/解串器、时钟分频器以及专用 I/O 和本地时钟资源。

- 可配置逻辑块 (CLB) 是 Xilinx FPGA 的基本逻辑元件, 提供组合和同步逻辑以及分布式存储器和 SRL32 移位 寄存器功能。Virtex-5 CLB 以真 6 输入查找表技术为基础,可提供比前几代可编程逻辑更优异的功能和性能。

- Block RAM 块提供灵活的 36Kb 真双端口 RAM,这种 RAM 可级联为更大的存储器块。另外,Virtex-5 Block RAM 包含的可选可编程 FIFO 逻辑可提高器件利用率。还可将每个 Virtex-5 Block RAM 配置为两个独立的 18 Kb 真双端口 RAM 模块,以便为需要较小 RAM 模块的设计提供存储器粒度。

- 可级联嵌入式 DSP48E Slice, 具有 25x18 补数乘法器 和 48 位加法器 / 减法器 / 累加器, 可提供大规模并行 DSP 算法支持。另外,每个 DSP48E Slice 都可用于执行按位逻辑功能。

- 时钟管理模块 (CMT) 为 FPGA 提供最灵活、最高性能的时钟控制。每个 CMT 包含两个数字时钟管理器 (DCM) 模块 (自校准、全数字)和一个 PLL/PMCD 模块 (自校准、模拟),用于时钟分配延迟补偿、时钟乘法/除法运算、粗/细粒度时钟相移和输入时钟抖动滤波。

此外, LXT 和 SXT 器件还包含:

- 集成 PCI Express 端点模块,提供 1 倍、2 倍、4 倍或 8 倍 PCI Express 端点功能。当与 RocketIO 收发器配合使用时,可以用最少的 FPGA 逻辑实现一个完整的 PCI Express 端点。

- 10/100/1000 Mb/s 以太网媒体访问控制模块提供以太网功能。

- RocketIO GTP 收发器,运行速度可达 3.2 Gb/s。每个 GTP 收发器都支持全双工时钟与数据恢复。

通用布线矩阵 (GRM) 在各内部组件之间提供一个布线开关阵列。每个可编程元件均与一个开关矩阵绑定,以实现对通用布线矩阵的多重连接。总体可编程互连是层级式结构,可支持高速设计。在 Virtex-5 器件中,优化的布线连接能够以最少的中间连线支持 CLB 互连。减少中间连线极大地提高了后期布局布线 (PAR) 设计性能。

包括布线资源在内的所有可编程元件均由静态存储器元件中的存储值控制。这些值在配置过程中加载到 FPGA 中,可重新加载以便更改可编程元件的功能。

## Virtex-5 功能

本部分简述 Virtex-5 系列 FPGA 的功能。

### 输入/输出块(SelectIO)

IOB 可编程,并可分类如下:

- 可编程单端或差分 (LVDS) 运行

- 具有可选单倍数据速率 (SDR) 或双倍数据速率 (DDR) 寄存器的输入块

- 具有可选 SDR 或 DDR 寄存器的输出块

- 双向块

- 逐比特去歪斜电路

- 专用 I/O 和区域时钟资源

- 内置数据串行器/解串器

IOB 寄存器为边沿触发 D 型触发器或电平敏感锁存器。 IOB 支持以下单端标准:

- I VTTI

- LVCMOS (3.3V、2.5V、1.8V 1.5V 和 1.2V)

- PCI (33 和 66 MHz)

- PCI-X

- GTL 和 GTLP

- HSTL 1.5V 和 1.8V (I、II、III 和 IV 级)

- HSTL 1.2V (一级)

- SSTL 1.8V 和 2.5V ( I 和 II 级 )

数控阻抗 (DCI) I/O 功能可配置成为每个单端 I/O 标准和某些差分 I/O 标准提供片上终端。

IOB 元件还支持以下差分信令 I/O 标准:

- LVDS 和扩展 LVDS (仅 2.5V)

- BLVDS (总线 LVDS)

- ULVDS

- Hypertransport<sup>™</sup>

- 差分 HSTL 1.5V 和 1.8V ( I 级与 II 级 )

- 差分 SSTL 1.8V 和 2.5V ( I 和 II 级 )

- RSDS (2.5V 点对点)

每个差分对使用两个相邻的引脚。两个或四个 IOB 块连接到一个接入布线资源的开关矩阵。

逐比特去歪斜电路允许 FPGA 内部的可编程信号延迟。逐比特去歪斜灵活地提供细粒度延迟增量,以精细地生成一系列信号延迟。这对于在源同步接口中同步信号边沿尤其有用。对于位置选择得当的通用 I/O (每组八个),应该为同一局部区域内的 I/O 添加特殊的硬件连接,从而将其设计成具有"区域 clock-capable"的 I/O。这些区域时钟输入分布在限定的区域内,以尽量减轻各 IOB 之间的时钟歪斜。区域 I/O 时钟是对全局时钟资源的补充。

为每个 I/O 增加了数据串行器 / 解串器功能,以支持源同步接口。输入路径包含一个附有时间分频器的串并转换器,而输出路径则包含一个并串转换器。

有关 Virtex-5 IOB 的深入指导,请参阅《Virtex-5 用户指南》。

### 可配置逻辑块 (CLB)

一个 Virtex-5 CLB 资源由两个 Slice 组成。每个 Slice 包含并等效于:

- 四个函数发生器

- 四个存储元件

- 算术逻辑门

- 大型多路复用器

- 快速进位前瞻链

函数发生器可配置为 6 输入 LUT 或双输出 5 输入 LUT。某些 CLB 中的 SLICEM 可配置成作为一个 32 位移位寄存器(或两个 16 位移位寄存器)或 64 位分布式 RAM 运行。另外,可将四个存储元件配置成边沿触发的 D 型触发器或电平敏感型锁存器。每个 CLB 具有内部快速互连,并且连接到一个接入通用布线资源的开关矩阵。

《Virtex-5 用户指南》中进一步讨论了 Virtex-5 CLB。

#### **Block RAM**

36Kb 真双端口 RAM 模块资源可以编程为从 32K x 1 到 512 x 72 的各种深度和宽度配置。另外,每个 36Kb 模块也可配置成作为两个独立的 18Kb 双端口 RAM 模块运行。

每个端口都完全同步并独立,提供三种 "边写边读"模式。 Block RAM 可以级联,以实现大型嵌入式存储块。此外,作 为选项还提供了后端流水线寄存器、时钟控制电路、内置 FIFO 支持、ECC 和字节写使能功能。

《Virtex-5 用户指南》中进一步讨论了 Virtex-5 器件中的 Block RAM 功能。

#### 全局时钟

CMT 和全局时钟多路复用器缓冲器为设计高速时钟网络提供了完善的解决方案。

每个 CMT 包含两个 DCM 和一个 PLL/PMCD。DCM 和 PLL/PMCD 可独立使用,也可广泛级联。最多可使用六个 CMT 模块,总共可提供 18 个时钟发生器元件。

每个 DCM 都提供常用的时钟生成功能。为了生成无歪斜的内部或外部时钟,可以把每个 DCM 都用于消除时钟分配延迟。DCM 还提供输出时钟的 90°、180°和 270°相移版本。细粒度相移以数分之一时钟周期的增量提供更高分辨率的相位调整。灵活的频率综合提供等于输入时钟频率分数或整数倍的时钟输出频率。

为增强 DCM 功能, Virtex-5 CMT 还包含一个 PLL/PMCD。该模块提供参考时钟抖动滤波和更多频率综合选项。

Virtex-5 器件具有 32 个全局时钟 MUX 缓冲器。时钟树设计为差分式。差分时钟可帮助减少抖动和占空比失真。

#### DSP48E Slice

DSP48E Slice 资源包含一个 25 x 18 补数乘法器和一个 48 位加法器 / 减法器 / 累加器。每个 DSP48E Slice 还含有广泛的级联功能,可有效实现高速 DSP 算法。

《Virtex-5 XtremeDSP 设计考虑因素》中进一步讨论了 Virtex-5 DSP48E Slice 的功能。

#### 布线资源

Virtex-5 器件中的所有部件都使用相同的互连方案以及相同的全局布线矩阵接入方式。另外,CLB 到 CLB 的布线设计以尽可能少的中间连线提供一整套连接功能。时序模型是共享的,可大大提高高速设计性能的可预测性。

#### 边界扫描

边界扫描指令和相关数据寄存器支持接入和配置 Virtex-5 器件的标准方法,符合 IEEE 标准 1149.1 和 1532。另外,IEEE 1149.6 JTAG 标准支持含有 RocketIO 收发器 (LXT和 SXT 平台)的器件。

#### 配置

Virtex-5 器件的配置方法是用下列模式之一将比特流载入内部配置存储器:

- 从动串行模式

- 主动串行模式

- 从动 SelectMAP 模式

- 主动 SelectMAP 模式

- 边界扫描模式 (IEEE-1532 和 IEEE-1149)

- SPI 模式 (串行外设接口标准 Flash)

- BPI 上 /BPI 下模式 (字节宽度外设接口标准 x8 或 x16 NOR Flash)

另外, Virtex-5 器件还支持下列配置选项:

- 用于 IP 保护的 256 位 AES 比特流解密

- 支持冷 / 热启动的多比特流管理 (MBM)

- 并行配置总线宽度自动检测

- 并行菊花链

- 配置 CRC 和 ECC 支持,可实现最强大、最灵活的器件 完整性校验

《Virtex-5 配置指南》中进一步讨论了 Virtex-5 器件配置。

#### 系统监视器

FPGA 是高可用性 / 可靠性基础架构的重要构建模块。因 此,有必要更好地监测 FPGA 的片上物理环境及其在系统内 紧邻的周边环境。Virtex-5 系统监视器首次为 FPGA 及其外 部环境提供了更简单的监测。Virtex-5系列的每个成员都包 含一个系统监视器模块。Virtex-5系统监视器是围绕一个 10 位 200kSPS ADC (模数转换器)构建的。这个 ADC 用 于对若干片上传感器进行数字化,以提供有关 FPGA 内部物 理环境的信息。片上传感器包括一个温度传感器和几个电源 传感器。对外部环境的访问是通过若干外部模拟输入通道提 供的。这些模拟输入是通用的,可用于对种类繁多的电压信 号类型进行数字化。提供了对单极、双极和真差分输入方案 的支持。可以通过 JTAG TAP 全面访问片上传感器和外部通 道,从而可以将 PC 板上现有的 JTAG 基础架构用于开发期 间和现场部署后的模拟测试和高级诊断。系统监视器在 FPGA 通电之后和配置之前完全可运行。系统监视器在设计 中不需要显式例示即可获得对其基本功能的访问权。这使得 即使在设计周期的最后阶段也可以使用系统监视器。

《Virtex-5 系统监视器用户指南》中进一步讨论了 Virtex-5 系统监视器。

## Virtex-5 LXT 和 SXT 平台的功能

本部分简要叙述仅在 LXT 和 SXT 器件中使用的模块。

## 三态 (10/100/1000 Mb/s) 以太网 MAC

Virtex-5 LXT 和 SXT 器件包含四个嵌入式以太网 MAC 模块。这些模块具有以下特点:

- 符合 IEEE 802.3

- 经过 UNH 一致性测试

- 使用 SelectIO 技术的 MII/GMII 接口,或者当与 RocketIO 收发器配合使用时的 SGMII 接口

- 半双工或全双工

- 支持巨型帧

- 1000 Base-X PCS/PMA: 当与 RocketIO GTP 收发器 配合使用时,可提供完全 1000 Base-X 片上实现

- 对微处理器的 DCR 总线连接

### 与 PCI Express 兼容的集成端点模块

Virtex-5 LXT 和 SXT 器件包含一个集成端点模块。该模块实现事务层、数据链路层和物理层功能,在尽量少用 FPGA 逻辑的情况下提供完整的 PCI Express 端点功能。这些模块具有以下特点:

- 符合 PCI Express 基础规范 1.1

- 与 RocketIO 收发器配合使用可提供完整的端点功能

- 每模块支持 1 倍、2 倍、4 倍、或 8 倍通道宽度

### RocketIO GTP 收发器

8 – 24 个通道 RocketIO GTP 收发器, 能够以 100 Mb/s 到 3.2 Gb/s 的速度运行。

- 完全时钟和数据恢复功能

- 8/16 位或 10/20 位数据通路支持

- 可选 8B/10B 或基于 FPGA 的编码 / 解码功能

- 集成 FIFO/ 弹性缓冲器

- 通道绑定和时钟校正支持

- 嵌入式 32 位 CRC 生成 / 检查

- 集成的间隔符检测或 A1/A2 检测功能

- 可编程预加重(AKA 发射器均衡)

- 可编程发射器输出摆幅

- 可编程接收器均衡

- 可编程接收器终端

- 嵌入式支持:

- 带外 (OOB) 信令: 串行 ATA

- 信标、电气空闲和 PCI Express 接收器检测

- 针对接收器的片上可旁路 AC 耦合

- 内置式 PRBS 生成器 / 校验器

《Virtex-5 RocketIO GTP 收发器用户指南》中进一步讨论了 Virtex-5 RocketIO GTP 收发器。

## 知识产权核

Xilinx 提供常用复合功能的 IP 核,包括 DSP、总线接口、处理器和处理器外设。客户使用 Xilinx LogiCORE™ 产品及第三方 AllianceCORE 参与方提供的核,可以缩短开发时间、降低设计风险并获得优良的设计性能。另外,CORE Generator™ 系统还允许客户在 Virtex-5 FPGA 中实现 IP 核,以获得可预测和可重复性的性能。该系统提供简单的用户界面,用以生成针对 FPGA 优化的基于参数的核。

System Generator for DSP 工具允许系统架构设计师用手工设计的 IP 快速建立 DSP 功能模型并实现这些功能;另外,该工具为使用第三方系统级 DSP 设计工具提供了界面。System Generator for DSP 可实现支持 Virtex-5 FPGA 的多种高性能 DSP 核,包括使用交织器 / 解交织器、Reed-Solomon 编码器 / 解码器和 Viterbi 解码器的 Xilinx 前向纠错解决方案。对于创建支持通讯市场的高灵活性连接码编解玛器,这些核是理想的选择。

使用 Virtex-5 RocketIO GTP 收发器,可实现业界领先的连接和网络 IP 核,其中包括最先进的 PCI Express、串行RapidIO、光纤通道和 10 Gb 以太网核。Xilinx SPI-4.2 IP 核使用 Virtex-5 ChipSync 技术实现动态相位对齐,以获得高性能源同步运行。Xilinx 还为高级系统同步运行提供了 PCI 核。

MicroBlaze™ 32 位核提供行业最快的软处理解决方案,用来构建面向网络、电讯、数据通信以及嵌入式和消费市场的复杂系统。MicroBlaze 处理器采用 RISC 架构,这种架构使用哈佛式独立 32 位指令和全速运行的数据总线,可以从片上和外部两种存储器执行程序和访问数据。一整套标准外设也启用了 CoreConnect™,以便为 MicroBlaze 设计人员提供兼容性和可重复利用性。

Virtex-5 FPGA 的所有 IP 核均可见于 "Xilinx IP 中心"门户网站,该网站提供最新的知识产权核和参考设计,可以通过智能搜索快速访问。

Xilinx 为 PCI Express 提供了两种不同的 Virtex-5 Logi-CORE™ 端点解决方案,用以配置 Virtex-5 LXT 和 SXT FPGA 中内置的 PCI Express 模块。这两种解决方案均免费提供。

#### 用于 PCI Express 的 Virtex-5 LogiCORE 模块和端点

这种 IP 为端点应用提供多种易用功能和优化配置,可简化设计过程,缩短上市时间。

### 用于 PCI Express 的 Virtex-5 LogiCORE 模块端点

这种 IP 非常适合需要访问模块全部功能的超级用户, 他们需要定制用户界面、通道可用性、通道请求、存储器 BAR 过滤和非存储器 TLP ID 校验以及为实现最高性能和最佳尺寸而进行的滤波。

这两种解决方案都是通过 Xilinx CORE 生成器实现。全面访问核(包括比特流生成功能)需要有 "完全许可证"(免费)。《Virtex-5 PCI Express 端点选择指南》中对使用这两种核的功能和设计指导原则有深入说明。

# 应用指南和参考设计

可以到 Xilinx 网站获取专门为 Virtex-5 系列撰写的应用指南和参考设计, 网址是:

http://www.xilinx.com/cn/virtex5

# Virtex-5 器件及封装组合和最大 I/O 数

表 2: Virtex-5 器件及封装组合和最大 I/O 数

| 封装         | FF324<br>FFG324<br>19 x 19 |     | FF676<br>FFG676<br>27 x 27 |     | FF1153<br>FFG1153<br>35 x 35 |     | FF1760<br>FFG1760<br>42.5 x 42.5 |       | FF665<br>FFG665<br>27 x 27 |     | FF1136<br>FFG1136<br>35 x 35 |     | FF1738<br>FFG1738<br>42.5 x 42.5 |     |

|------------|----------------------------|-----|----------------------------|-----|------------------------------|-----|----------------------------------|-------|----------------------------|-----|------------------------------|-----|----------------------------------|-----|

| 尺寸 (mm)    |                            |     |                            |     |                              |     |                                  |       |                            |     |                              |     |                                  |     |

| 器件         | GT                         | I/O | GT                         | I/O | GT                           | I/O | GT                               | I/O   | GT                         | I/O | GT                           | I/O | GT                               | I/O |

| XC5VLX30   | 无                          | 220 | 无                          | 400 |                              |     |                                  |       |                            |     |                              |     |                                  |     |

| XC5VLX50   | 无                          | 220 | 无                          | 440 | 无                            | 560 |                                  |       |                            |     |                              |     |                                  |     |

| XC5VLX85   |                            |     | 无                          | 440 | 无                            | 560 |                                  |       |                            |     |                              |     |                                  |     |

| XC5VLX110  |                            |     | 无                          | 440 | 无                            | 800 | 无                                | 800   |                            |     |                              |     |                                  |     |

| XC5VLX220  |                            |     |                            |     |                              |     | 无                                | 800   |                            |     |                              |     |                                  |     |

| XC5VLX330  |                            |     |                            |     |                              |     | 无                                | 1,200 |                            |     |                              |     |                                  |     |

| XC5VLX30T  |                            |     |                            |     |                              |     |                                  |       | 8 GTP                      | 360 |                              |     |                                  |     |

| XC5VLX50T  |                            |     |                            |     |                              |     |                                  |       | 8 GTP                      | 360 | 12 GTP                       | 480 |                                  |     |

| XC5VLX85T  |                            |     |                            |     |                              |     |                                  |       |                            |     | 12 GTP                       | 480 |                                  |     |

| XC5VLX110T |                            |     |                            |     |                              |     |                                  |       |                            |     | 16 GTP                       | 640 | 16 GTP                           | 680 |

| XC5VLX220T |                            |     |                            |     |                              |     |                                  |       |                            |     |                              |     | 16 GTP                           | 680 |

| XC5VLX330T |                            |     |                            |     |                              |     |                                  |       |                            |     |                              |     | 24 GTP                           | 960 |

| XC5VSX35T  |                            |     |                            |     |                              |     |                                  |       | 8 GTP                      | 360 |                              |     |                                  |     |

| XC5VSX50T  |                            |     |                            |     |                              |     |                                  |       | 8 GTP                      | 360 | 12 GTP                       | 480 |                                  |     |

| XC5VSX95T  |                            |     |                            |     |                              |     |                                  |       |                            |     | 16 GTP                       | 640 |                                  |     |

#### 注.

# Virtex-5 订购信息

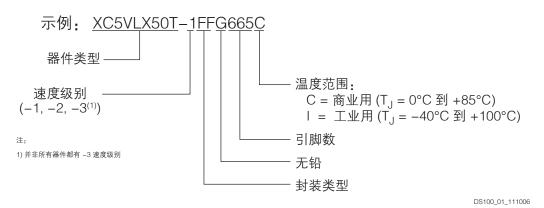

图 1 所示 Virtex-5 的订货信息适用于所有封装,包括无铅封装。

图 1: Virtex-5 订购信息

<sup>7.</sup> 1. 倒装芯片封装也有无铅版本 (FFG)。

## 修订历史

下表说明此技术文档的修订历史。

| 日期     | 版本  | 修订                                                                             |  |  |  |  |  |

|--------|-----|--------------------------------------------------------------------------------|--|--|--|--|--|

| 2006年  | 1.0 | Xilinx 最初版本。                                                                   |  |  |  |  |  |

| 4月14日  |     |                                                                                |  |  |  |  |  |

| 2006年  | 1.1 | 首版发布到 Xilinx 网站。少量排印修改以及为突出最新功能所做的描述更新。从第 2 页                                  |  |  |  |  |  |

| 5月12日  |     | <b>"Virtex-5 逻辑架构"</b> 中删除 LUT 使用项号。                                           |  |  |  |  |  |

| 2006 年 | 2.0 | 在整个文档中增加有关 LXT 平台的内容。其中包括对 RocketIO GTP 收发器、以太网 MAC                            |  |  |  |  |  |

| 9月6日   |     | 可PCI Express 端点模块的说明。                                                          |  |  |  |  |  |

| 2006 年 | 2.1 | 增加有关 LX85T 器件的内容。增加系统监视器描述和功能。                                                 |  |  |  |  |  |

| 10月12日 |     |                                                                                |  |  |  |  |  |

| 2006 年 | 2.2 | 增加有关 LX220T 器件的内容。修改表 1 中 LX330 的 I/O 组总数。修改图 1 中的                             |  |  |  |  |  |

| 12月28日 |     | XC5VLX50T-FFG665 示例。在第 6 页上阐明对 <b>"差分 SSTL 1.8V 和 2.5V ( I 和 II 级 )"</b> 的 支持。 |  |  |  |  |  |

| 2007年  | 3.0 | 在整个文档中增加有关 SXT 平台器件的内容。                                                        |  |  |  |  |  |

| 2月2日   |     |                                                                                |  |  |  |  |  |

## Virtex-5 文档

有关 Virtex-5 系列 FPGA 的最新完整文档可以从 Xilinx 网站获得。除了最新的 Virtex-5 系列概述,还可以下载以下文件:

《Virtex-5 数据手册。直流和开关特性》

本数据手册包含 Virtex-5 系列的直流和开关特性指标。

《Virtex-5 用户指南》

本指南包含有关以下内容的章节:

- 时钟资源

- 时钟管理技术 (CMT)

- 锁相环 (PLL)

- Block RAM 和 FIFO 存储器

- 可配置逻辑块 (CLB)

- SelectIO 资源

- I/O 逻辑资源

- 高级 I/O 逻辑资源

《Virtex-5 XtremeDSP设计考虑因素》

本指南介绍 DSP48E Slice, 并包含使用 DSP48E 数学函数 和各种滤波器的参考设计。

《Virtex-5 配置指南》

本配置指南包罗万象,各章节涉及内容包括配置接口(串行和并行)、多比特流管理、比特流加密、边界扫描和 JTAG 配置以及重新配置技术。 《Virtex-5 封装和引脚规范》

本规范包含器件 / 封装组合和最大 I/O 数表、引脚定义表、引脚布局表、引脚图、机械图和热性能技术规范。

《Virtex-5 PCB 设计指南》

本指南提供有关 Virtex-5 器件 PCB 设计的信息,着重讲述 PCB 级和接口级设计决策方略。

《Virtex-5 系统监视器用户指南》

本指南概述系统监视器的功能。

《Virtex-5 RocketIO GTP 收发器用户指南》

本指南描述 Virtex-5 LXT 和 SXT 平台器件中使用的 Rocke-tIO GTP 收发器。

《Virtex-5 嵌入式三态以太网媒体访问控制器》

本指南描述 Virtex-5 LXT 和 SXT 平台器件中使用的专用三态以太网媒体访问控制器。

《用于 PCI Express 设计的 Virtex-5 集成端点模块用户指南》

本指南描述 Virtex-5 LXT 和 SXT 平台器件中的符合 PCI Express 的集成端点模块。