# CMOS 触发器在 CP 边沿的工作特性研究

王接枝, 熊熙烈, 吕 岚, 黄先恺, 何锦军

(上饶师范学院 物理系, 江西 上饶 334001)

**摘要:** CMOS 触发器 CP 边沿时间与器件参数的关系, 用实验展现了 CP 边沿时间过长时出现的异变现象, 分析了传输门在 CP 边沿的共同导通问题, 提出了 CMOS 触发器在 CP 边沿工作的电路模型, 推导了 CP 边沿时间的计算公式, 完善和深化了 CMOS 触发器动态工作电路理论。

**关键词:** CMOS 触发器 CP 边沿工作特性 CP 边沿电路模型

对时钟脉冲(简称 CP)边沿时间的要求, 是触发器品质评价的重要指标之一。触发器只有在 CP 边沿陡峭(短的边沿时间)的条件下工作, 才能保证其可靠性。文献[1]指出, CMOS 电路的基本触发单元是由传输门和或非门组成的主从结构, 输入的数据由传输门引导, 因此, 对时钟脉冲的上升时间和下降时间就有一定的要求。但文献[1]对 CMOS 触发器在 CP 边沿的工作模式没有进行深入研究, 留下了两个有待探索的问题: 一是 CP 边沿时间过长, 触发器会出现什么异常现象及为什么会出现这种现象; 二是为保证触发器正常工作, CP 边沿时间不能超过多少, 它与触发器参数的关系及计算与测量方法。这些问题的回答都依赖于触发器在 CP 边沿工作特性的研究。为此, 采用标准 CMOS CD4000 系列、高速 CMOS 74HC 和 74HCT 系列中有关型号的触发器为实验样品, 观察 CP 边沿时间过长时出现的异常现象, 研究异常现象出现的原因, 提出 CMOS 触发器在 CP 边沿工作的电路模型, 探索触发器正常工作时 CP 边沿时间与触发器参数的关系, 从而使文献[1]的有关论述更加具体、深化、正确, 这对 CMOS 触发器的正确使用、研制和提高产品质量都有一定的理论指导意义。

## 1 CMOS 触发器的结构与工作原理

CMOS D 触发器是主-从结构形式的一种边沿触发器, CMOS T 型触发器、JK 触发器、计数单元、移位单元和各种时序电路都由其组成, 因此仅以 CMOS D 触发器为例进行说明。

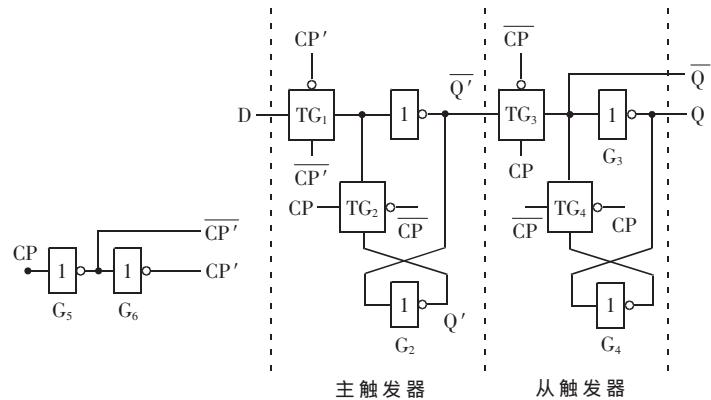

图 1 是用 CMOS 传输门和反相器构成的 D 触发器<sup>[1][2]</sup>, 反相器  $G_1$ 、 $G_2$  和传输门  $TG_1$ 、 $TG_2$  组成了主触发器, 反相器  $G_3$ 、 $G_4$  和传输门  $TG_3$ 、 $TG_4$  组成了从触发器。 $TG_1$  和  $TG_3$  分别为主触发器和从触发器的输入控制门。反相器  $G_5$ 、 $G_6$  对时钟输入信号 CP 进行反相及缓冲, 其输出 CP 和  $\overline{CP}$  作为传输门的控制信号。根据 CMOS 传输门的工作原理和图中控制信号的极性标注可知, 当传输门  $TG_1$ 、

图 1 CMOS D 触发器

$TG_4$  导通时,  $TG_2$ 、 $TG_3$  截止; 反之, 当  $TG_1$ 、 $TG_4$  截止时,  $TG_2$ 、 $TG_3$  导通。

当  $CP'=0$ ,  $\overline{CP'}=1$  时,  $TG_1$  导通,  $TG_2$  截止, D 端输入信号送入主触发器中, 使  $Q'=D$ ,  $\overline{Q'}=\overline{D}$ , 但这时主触发器尚未形成反馈连接, 不能自行保持。 $Q'$ 、 $\overline{Q}'$  跟随 D 端的状态变化; 同时, 由于  $TG_3$  截止,  $TG_4$  导通, 所以从触发器形成反馈连接, 维持原状态不变, 而且它与主触发器的联系被  $TG_3$  切断。

当  $CP'$  的上升沿到达(即  $CP'$  跳变为 1,  $\overline{CP'}$  下降为 0)时,  $TG_1$  截止,  $TG_2$  导通, 切断了 D 信号的输入, 由于  $G_1$  的输入电容存储效应,  $G_1$  输入端电压不会立即消失, 于是  $Q'$ 、 $\overline{Q}'$  在  $TG_1$  截止前的状态被保存下来; 同时由于  $TG_3$  导通,  $TG_4$  截止, 主触发器的状态通过  $TG_3$  和  $G_3$  送到了输出端, 使  $Q=Q'=D$ ( $CP$  上升沿到达时 D 的状态), 而  $\overline{Q}=\overline{Q'}=\overline{D}$ 。

在  $CP'=1$ ,  $\overline{CP'}=0$  期间,  $Q=Q'=D$ ,  $\overline{Q}=\overline{Q'}=\overline{D}$  的状态一直不会改变, 直到  $CP'$  下降沿到达时(即  $CP'$  跳变为 0,  $\overline{CP'}$  跳变为 1),  $TG_2$ 、 $TG_3$  又截止,  $TG_1$ 、 $TG_4$  又导通, 主触发器又开始接收 D 端新数据, 从触发器维持已转换后的

状态。

可见,这种触发器的动作特点是输出端的状态转换发生在 CP' 的上升沿,而且触发器所保持的状态仅仅取决于 CP' 上升沿到达时的输入状态。正因为触发器输出端状态的转换发生在 CP' 的上升沿(即 CP 的上升沿),所以这是一个 CP 上升沿触发的边沿触发器,CP 上升沿为有效触发沿,或称 CP 上升沿为有效沿(下降沿为无效沿)。若将四个传输门的控制信号 CP' 和  $\overline{CP'}$  极性都换成相反的状态,则 CP 下降沿为有效沿,而上升沿为无效沿。下面以 CP 上升沿为有效触发沿进行分析。

## 2 触发器在 CP 边沿的工作特性研究

### 2.1 触发器在 CP 边沿工作状况的实验观察

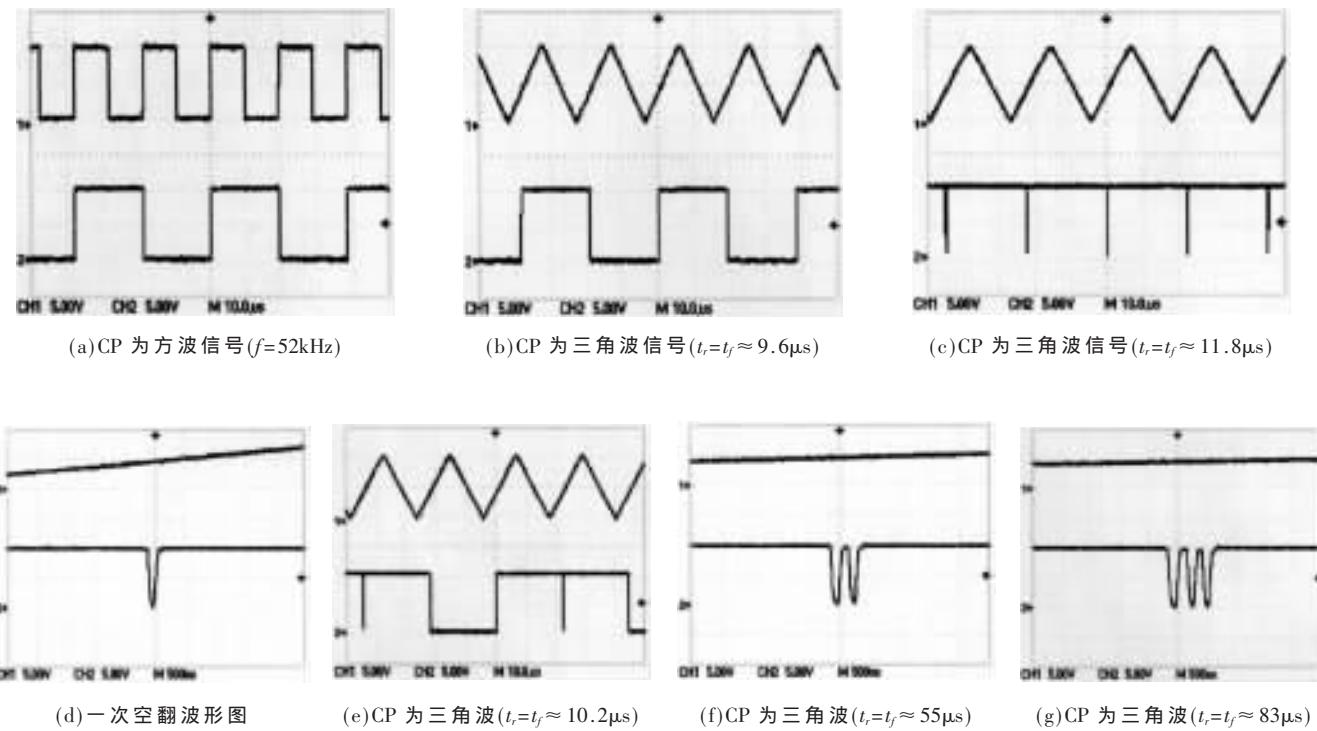

把 CMOS D 触发器 CD4013 接成计数工作方式(D 端与  $\overline{Q}$  端连接,即  $D = \overline{Q}$ ),工作电源电压  $V_{DD} = 10V$ ,由函数发生器 DF1641D 输出的信号作为时钟端输入信号 CP,用数字存储示波器 TDS1000(带宽 60MHz)同时观察触发器时钟端和输出端波形,如图 2 所示,称之为工作波形图。

图 2(a)所示是 CP 为频率  $f = 52kHz$ ,幅度  $U_m = 10V$  的方波信号时所观察到的工作波形图(图中上方是 CP 信号,下方为输出信号,以下同)。由图可见,对应于每一 CP 信号有效沿(上升沿),输出状态翻转一次,计数工作正常。将上述 CP 信号转变为同频率的三角波,它的上升沿和下降沿作为 CP 的上升沿和下降沿,则 CP 边沿时间  $t_r = t_f \approx 9.6\mu s$ ,这时工作波形如图 2(b)所示,可见输出波形没有发生变化,在对应于 CP 上升沿某一时刻,输出

状态翻转一次。

增大 CP 上升时间(调节信号频率即可),在  $t_r = t_f \approx 11.8\mu s$  时,工作波形如图 2(c)所示,输出波形在 CP 上升沿出现了一次空翻,即从高电平翻转为低电平,又从低电平翻转为高电平的两次翻转。若将示波器时间坐标扩展 20 倍,该空翻波形如图 2(d)所示。

在调节 CP 上升时间使触发器输出波形由正常计数状态向一次空翻变化时,还出现了图 2(e)所示的过渡状态,这是在 CP 上升时间为  $t_r \approx 10.2\mu s$  瞬间捕捉(采样)到的工作波形图。由图可见,对应于 CP 第 1 个和第 4 个上升沿输出空翻一次,出现异常现象。而对于第 2、3、5 个 CP 上升沿,输出只翻转一次,属正常工作状态。

继续增大 CP 上升时间,对应 CP 上升沿还会出现图 2(f)、图 2(g)所示的波形图以及更多次空翻现象,事实上,输出已出现振荡现象。

在对其他 CMOS 触发器如 CD4027(JK 触发器)、高速 CMOS 触发器 74HC73(JK 触发器)、74HC74(D 触发器)、74HC107(JK 触发器)和 74HCT107(JK 触发器)的实验中,也出现了类似的现象。即若 CP 边沿时间过长,对应于 CP 有效沿,触发器输出状态会出现振荡现象,一次空翻只是一次振荡而已,而在 CP 无效沿,输出状态不会出现异常现象。

### 2.2 传输门在 CP 边沿的共同导通现象

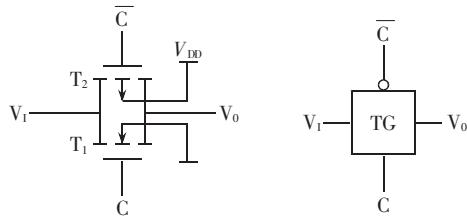

CMOS 传输门电路结构如图 3 所示。它是由增强型 NMOS 管  $T_1$  和 PMOS 管  $T_2$  的源极和漏极分别相接而成,其连接处就是传输门的输入端  $V_i$  和输出端  $V_o$ ,PMOS 管衬底接工作电源电压  $V_{DD}$ ,NMOS 管衬底接地,电压 0

图 2 工作波形图

图 3 CMOS 传输门电路结构和逻辑符号

伏, 加在两管栅极的是一对互补的控制信号  $C$  和  $\bar{C}$ , 它们的极性变换控制传输门输入端与输出端之间的导通与截止。

通常传输门中 NMOS 管开启电压  $V_{TN}$  和 PMOS 管的开启电压  $V_{TP}$  大小相等, 即  $V_{TN} = |V_{TP}| = V_T$ , 且工作电源电压  $V_{DD} > V_{TN} + |V_{TP}|$ 。当  $C=0, \bar{C}=1$  时, NMOS 管和 PMOS 管的栅极和衬底之间电压均为零, 源极和漏极之间不存在导电沟道, 两管均截止,  $V_1$  和  $V_0$  之间是断开的。在  $C$  由 0 开始上升的过程中, 当它上升到 NMOS 管的开启电压  $V_{TN}$  时, 相应的  $\bar{C}$  则要由高电平  $V_{DD}$  下降同样的幅度, 即下降为  $V_{DD} - |V_{TP}|$ 。这时 NMOS 管和 PMOS 管均开始导通。所以图 1 中  $TG_2, TG_3$  在  $CP'$  上升到  $V_{TN}$  时便会开始导通, 尽管  $TG_1, TG_4$  所加的控制信号与  $TG_2, TG_3$  是反相的, 但这时它们的 NMOS 管和 PMOS 管的栅极对衬底的电压还在开启电压之上(因为  $V_{DD} > V_{TN} + |V_{TP}|$ ),  $TG_1, TG_4$  还是处于导通状态, 直到  $CP'$  上升到  $V_{DD} - |V_{TP}|$  (相应的  $\bar{CP}'$  下降到  $V_{TN}$ ) 时,  $TG_1, TG_4$  才会截止。可见  $CP'$  上升过程中, 存在  $TG_1, TG_4$  和  $TG_2, TG_3$  共同导通的工作状态, 共同导通的时间是  $CP'$  由  $V_{TN}$  上升到  $(V_{DD} - |V_{TP}|)$  所经历的时间。

对  $CP'$  下降过程作同样分析可知, 在  $CP'$  下降过程中, 也会出现  $TG_1, TG_4$  和  $TG_2, TG_3$  共同导通的现象, 共同导通的时间是  $CP'$  从  $(V_{DD} - |V_{TP}|)$  下降到  $V_{TN}$  所经历的时间。

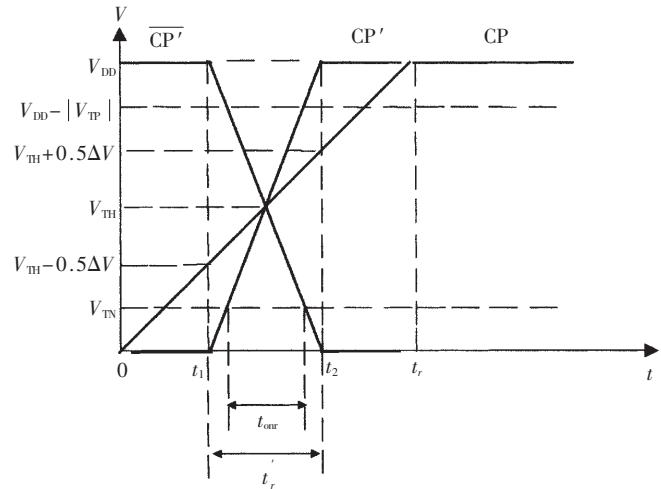

图 1 中传输门  $TG_1, TG_4$  和  $TG_2, TG_3$  在  $CP$  上升时共同导通时间  $t_{onr}$  可由图 4 示意说明。图中  $CP$  是触发器时钟端输入信号上升沿波形, 设其为线性上升, 上升时间为  $t_r$ 。  $\bar{CP}'$  和  $CP'$  分别为在  $CP$  作用下,  $G_5, G_6$  输出的折线近似波形,  $V_{TH}$  是它们的阈值电压, 通常近似为电源电压  $V_{DD}$  的一半, 即  $V_{TH} \approx \frac{1}{2} V_{DD}$ 。设反相器转换区电压大小为  $\Delta V$ , 由于它们的传输特性在阈值电压处有非常陡峭的变化, 所以在  $CP$  上升过程中, 当它小于  $(V_{TH} - 0.5\Delta V)$  时, 即未进入转换区时,  $\bar{CP}'$ 、 $CP'$  几乎不变。而  $CP$  电压处在转换区内,  $\bar{CP}'$  和  $CP'$  均会急剧变化, 当  $CP$  电压上升到  $V_{TH} + 0.5\Delta V$  以后, 则  $\bar{CP}'$ 、 $CP'$  又几乎不变。所以图 4 中曲线  $\bar{CP}'$  和  $CP'$  采用了折线近似, 它们的转折点分别为  $CP$  上升到  $V_{TH} - 0.5\Delta V$  的  $t_1$  时刻和上升到  $V_{TH} + 0.5\Delta V$  的  $t_2$

图 4  $t_{onr}$  图解分析示意图

时刻, 故  $\bar{CP}'$  的下降时间和  $CP'$  的上升时间都等于  $CP$  在转换区内所经历的时间  $t_r' = t_2 - t_1 = \frac{\Delta V}{V_{DD}} t_r$ 。

$V_{TN}$  和  $V_{TP}$  表示传输门中 NMOS 管和 PMOS 管的开启电压, 由前面分析可知,  $CP$  上升过程中,  $TG_1, TG_4$  和  $TG_2, TG_3$  共同导通的时间是  $CP'$  由  $V_{TN}$  上升到  $(V_{DD} - |V_{TP}|)$  所经历的时间, 也等于  $\bar{CP}'$  由  $(V_{DD} - |V_{TP}|)$  下降到  $V_{TN}$  的时间, 故共同导通时间为  $t_{onr}$ :

$$t_{onr} = \frac{V_{DD} - V_{TN} - |V_{TP}|}{V_{DD}} t_r' = \frac{\Delta V}{V_{DD}} \cdot \frac{V_{DD} - V_{TN} - |V_{TP}|}{V_{DD}} t_r$$

$$\text{设 } \alpha = \frac{V_T}{V_{DD}} \text{ (称为 CMOS 管归一化开启电压), } \beta = \frac{\Delta V}{V_{DD}},$$

由于  $V_{TN} = |V_{TP}| = V_T$

$$\text{则: } t_{onr} = \beta(1 - 2\alpha)t_r \quad (1)$$

同样分析可知, 在  $CP$  下降过程中, 设下降时间为  $t_f$ , 则  $TG_1, TG_4$  和  $TG_2, TG_3$  共同导通的时间  $t_{off}$  为:

$$t_{off} = \beta(1 - 2\alpha)t_f \quad (2)$$

## 2.3 触发器在 $CP$ 边沿的工作特性

### 2.3.1 在 $CP$ 上升沿的工作特性

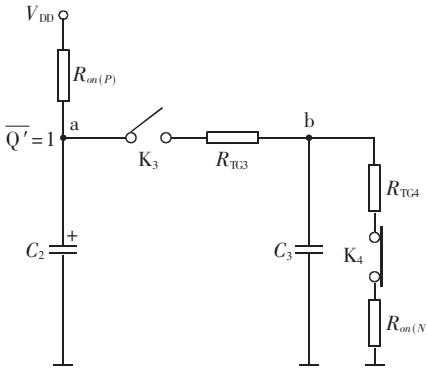

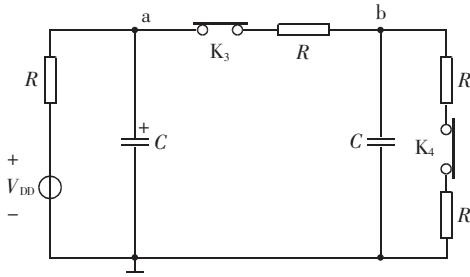

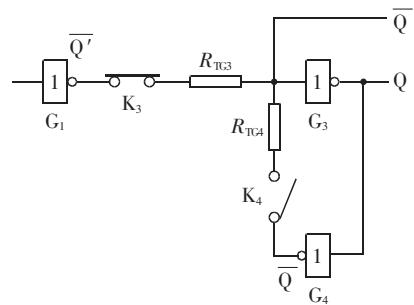

图 1 中  $CP' = 0, \bar{CP}' = 1$  时,  $TG_3$  断开,  $TG_4$  导通。若  $\bar{Q}' = 1, \bar{Q} = 0$ , 则表示反相器  $G_1$  中的 PMOS 管导通, 而 NMOS 管截止; 反相器  $G_4$  中的 PMOS 管截止, NMOS 管导通。采用 MOS 管的开关等效电路<sup>[2]</sup>, 则主、从触发器之间的等效电路如图 5 所示。图中  $R_{on(P)}$  是  $G_1$  中 PMOS 管的导通电阻,  $R_{on(N)}$  是  $G_4$  中 NMOS 管的导通电阻,  $a, b$  点分别为  $G_2, G_3$  的输入端,  $C_2, C_3$  是其输入电容,  $R_{TG3}, R_{TG4}$  是传输门  $TG_3, TG_4$  的导通电阻, 开关  $K_3, K_4$  则表示其工作状态。

文献[3]表明, 触发器最简单的版图布局结构选取所有器件有相同的宽长比  $W/L$ , 所以  $R_{on(P)} \approx R_{on(N)} \approx R_{TG3} \approx R_{TG4} = R, C_2 \approx C_3 = C$ , 在  $CP'$  上升沿传输门共同导通时间阶段  $t_{onr}$  内, 主、从触发器间的等效电路如图 6 所示。这是一个含有两个同类储能元件的二阶电路, 固有频率只可能是两个不相等的负实根, 电路的响应是欠阻尼的, 利用

图 5  $CP'=0, \bar{\theta}'=1, \bar{\theta}=0$  时主、从触发器之间等效电路

图 6  $CP'$  上升沿  $t_{oxr}$  期间主、从触发器之间等效电路

拉普拉斯变换, 可以求得 a、b 两点电压分别为:

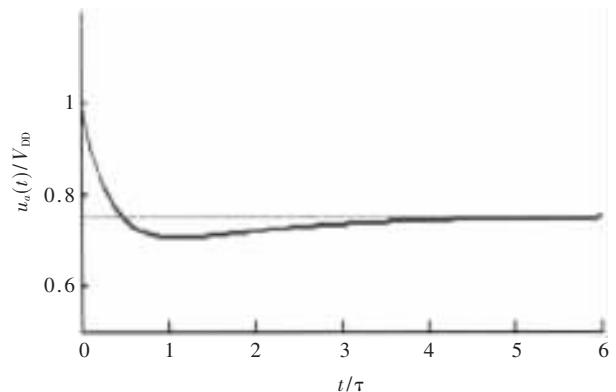

$$u_a(t) = 0.75V_{DD}(1 + 0.53e^{-\frac{1}{0.36\tau}} - 0.20e^{-\frac{1}{1.39\tau}}) \quad (3)$$

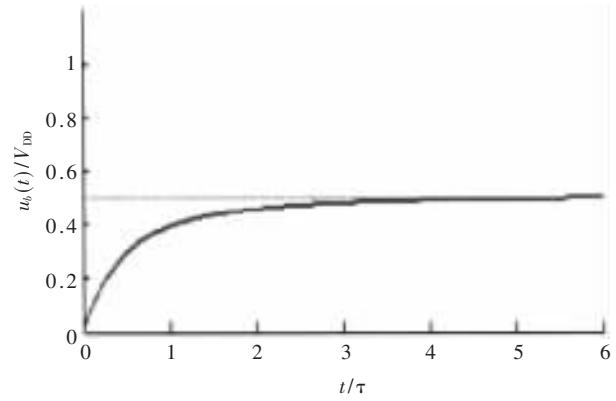

$$u_b(t) = 0.5V_{DD}(1 - 0.62e^{-\frac{1}{0.36\tau}} - 0.38e^{-\frac{1}{1.39\tau}}) \quad (4)$$

式中  $\tau = RC$  是反相器  $G_1 \sim G_4$  中 MOS 管的导通电阻与输入电容的乘积。

可以画出  $u_a(t)$  和  $u_b(t)$  的波形如图 7 所示。式(3)和图 7(a)表明, 在  $t_{oxr}$  期间, 门  $G_2$  的输入电压大于阈值电压, 且在逻辑 1 区, 从而通过  $G_2$  的输出保证  $G_1$  中 PMOS 管导通。式(4)和图 7(b)表明,  $G_3$  的输入电压将趋向阈值电压  $0.5V_{DD}$ , 一旦该电压进入阈值电压附近的转换区范围内, 则  $G_3$  被偏置在放大工作状态, 对输入信号起放大作用<sup>[1]</sup>。目前生产的 CD4000 系列和 74HC 系列的 CMOS 电路都采用带缓冲级的结构, 线性增益很高, 干扰信号或电路内部的噪声扰动会被放大并经  $G_4$  又反馈到  $G_3$  输入端, 形成强烈的正反馈过程。因而出现了图 2 中的异变现象, 直到  $CP'$  继续上升, 传输门的共同导通时间结束,  $TG_4$  截止(图 6 中  $K_4$  断开)时为止。

在  $\bar{Q}'=0, \bar{Q}=1$  的条件下进行同样的分析, 可得到类似的结果, 这时:

$$u_a(t) = 0.25V_{DD}(1 - 1.59e^{-\frac{1}{0.36\tau}} + 0.59e^{-\frac{1}{1.39\tau}}) \quad (5)$$

$$u_b(t) = 0.5V_{DD}(1 + 0.62e^{-\frac{1}{0.36\tau}} + 0.38e^{-\frac{1}{1.39\tau}}) \quad (6)$$

式(5)所表示的  $G_2$  输入电压小于阈值电压, 在逻辑 0 区, 从而通过  $G_2$  的输出保证  $G_1$  中 NMOS 管的导通, 使  $\bar{Q}'=0$ ; 而式(6)所表示的  $G_3$  输入电压也会趋向阈值电压

(a)  $u_a(t)$  波形

(b)  $u_b(t)$  波形

图 7  $CP'$  上升沿  $t_{oxr}$  期间  $u_a(t)$ 、 $u_b(t)$  波形

0.5V<sub>DD</sub>, 使输出出现异变现象。

### 2.3.2 在 CP 下降沿的工作特性

在  $CP'=1, \bar{CP}'=0$  时,  $TG_3$  导通,  $TG_4$  截止, 主、从触发器之间工作的等效电路如图 8 所示。这时  $G_4$  的输出总是等于  $G_3$  的输入, 即截止的传输门  $TG_4$  输出端与输入端之间的信号相等。所以在 CP 下降沿, 传输门  $TG_4$  开始导通(图中  $K_4$  闭合)时, 会使  $G_3$  的输出锁定, 而  $TG_3$  的继续导通对输出不产生影响。这就是说, 在 CP 下降沿, 传输门的共同导通状态不会引起触发器输出状态的异常变化。

图 8  $CP'=1$  时主、从触发器之间等效电路

### 2.3.3 触发器对 CP 边沿时间的要求

要使触发器在 CP 上升沿不出现异变现象, 则要求  $G_3$  的输入电压  $u_b(t)$  变化到转换区之前, 传输门  $TG_4$  必须

截止。测试表明,转换区电压  $\Delta V=(0.01\sim 0.05)V_{DD}$ ,这就要求  $u_b(t)$  变化到稳态值  $0.5V_{DD}$  的 95%~99% 之前,传输门共同导通时间结束,  $TG_4$  截止。在式(4)  $u_b(t)$  表达式中,第二项指数函数的时间常数比第三项小得多,故在  $u_b(t)$  趋向转换区时,其变化规律主要由第三项指数函数的时间常数  $1.39\tau$  决定。所以要求传输门的共同导通时间  $t_{onr}$  为:

$t_{onr} < (3\sim 5) \times 1.39\tau$ , 即  $t_{onr} < (4.17\sim 6.95) \tau$ , 约为:

$$t_{onr} < (4\sim 7) \tau \quad (7)$$

由式(1)可得:  $\beta(1-2\alpha)t_r < (4\sim 7) \tau$

$$\text{即 } t_r < \frac{(4\sim 7)\tau}{\beta(1-2\alpha)} \quad (8)$$

对于 CD4000 系列触发器,取典型值  $\tau=1000\Omega \times 10PF=0.01\mu s$ ,若  $V_{DD}=10V$ ,  $V_T=2V$ ,  $\Delta V=0.1V$ ,  $\alpha=\frac{V_T}{V_{DD}}=0.2$ ,  $\beta=\frac{\Delta V}{V_{DD}}=0.01$ ,则

$$t_r < \frac{(4\sim 7) \times 0.01}{0.01(1-2 \times 0.2)}$$

即  $t_r < (6.67\sim 11.67)\mu s$

本实验测得  $t_r$  应小于  $010.2\mu s$ ,理论计算与实验测试取得了比较吻合的结果。

对于有效触发沿是 CP 下降沿的 CMOS 触发器,同样分析可得要求 CP 下降时间  $t_f$  为:

$$t_f < \frac{(4\sim 7)\tau}{\beta(1-2\alpha)} \quad (9)$$

### 3 结论与说明

(1) CMOS 触发器在 CP 边沿会出现传输门共同导通的工作状态,这种工作状态会导致触发器在 CP 有效触发沿产生输出状态振荡的异变现象。

(2) 为了使触发器在 CP 触发沿不产生异变现象,保证其正常的工作状态,应对 CP 触发沿提出时间要求,它除与器件自身参数有关外,还与工作电源电压  $V_{DD}$  有关,式(8)、式(9)表明了这种关系。

(3) 触发器在 CP 信号无效触发沿不会出现输出状态的异变现象,从这个角度讲,对 CP 信号无效触发沿不存在时间要求,但 CP 边沿时间大,电路的功耗也大,所以也应同样加以限制。

### 参考文献

- [1]《中国集成电路大全》编写委员会.中国集成电路大全(CMOS 集成电路)[M].北京:国防工业出版社,1985.

- [2] 阎石.数字电子技术基础[M],第四版.北京:高等教育出版社,1998.

- [3] 朱正涌.半导体集成电路[M].北京:清华大学出版社,2001.

(收稿日期:2006-09-20)