## 基于 TMS320C6202 和 FPGA 的红外导引头 图像处理系统设计

蔡胜兵, 段哲民, 许家栋

(西北工业大学 电子信息学院, 陕西 西安 710072)

**摘要:**介绍了基于 TMS320C6202 和 FPGA 的红外成像导引头图像处理系统的设计原理和设计要求, 以及硬件调试过程。实验表明, 本系统能完成从背景和干扰的实时图像中区分目标和干扰、检测目标和跟踪目标, 并将跟踪误差信号送至导引头跟踪回路和导弹制导回路, 且始终是跟踪目标不受干扰, 实现从远到近制导的全过程, 直至击中目标的功能。

**关键词:**红外 图像处理 TMS320C6202 FPGA

红外成像制导技术是第四代近距格斗空空导弹的核心技术之一。与红外点源寻的制导导弹相比, 红外成像制导导弹具有抗红外干扰能力强、对目标迎头探测距离远、制导精度高等无可比拟的优点。为了满足未来高科技局部战争的迫切需求, 必须尽快研究第四代红外近距格斗导弹, 其核心技术就是红外成像制导技术, 故对红外成像制导技术的研究对我国第四代红外型空空导弹的研制起着极为关键的作用<sup>[1~2]</sup>。

DSP 与 FPGA 相结合是一般图像处理系统硬件设计的首选方式。本文选用了 TI 公司最新推出的 TMS320C6202(以下简称 C6202)高性能图像处理芯片和 XILINX 公司的 FPGA XCV600E 作为系统的核心器件, 设计了红外成像导引头图像处理系统, 进一步改善了导引头成像系统成像质量, 从而提高了导引头系统的性能。

### 1 系统原理

红外图像处理系统的作用在图像序列中提取目标信息以维持对目标的稳定跟踪。由于弹目相对距离不同, 目标在导引头中所成图像大小亦不同, 可以利用的特征也不同, 因此需要分远距、中距、近距三个阶段, 选择不同的算法来处理图像, 给出制导所需的误差信号。在复杂背景干扰条件下, 导引头应能够预测目标受到遮挡, 并预测目标受遮挡后的特征变化, 以便及时采取措施保证不丢失目标, 一旦目标重新出现, 导引头可以恢复对其跟踪。检测和跟踪过程中, 导引头还应该能够抗人工干扰。抗干扰问题存在于目标的捕获和跟踪两个阶段。捕获阶段的抗干扰目的在于对标记出来的每个可能目标计算其各种特征, 并根据这些特征将真实目标与干扰区分开来, 捕获真实目标进行跟踪。可供使用的特征包括目标的面积( $S$ )、目标的长度( $L$ )、目标的宽度( $W$ )、目标的质心( $X_c, Y_c$ )、目标的最大灰度( $G_{max}$ )、目标的平均灰度( $G_{mean}$ )、目标的运动速度( $V_x, V_y$ )、目标的运动方

向( $Dir$ )等。经过对多帧的考察, 根据这些特征将当前帧图像中的所有目标及其历史组成若干条目标链, 再根据目标链得出每个目标的生长过程, 其中最为“健壮”的目标就被认为是真实目标并加以锁定。根据目标距离的远近, 图像处理子系统使用不同的跟踪算法。

近距离的主要算法是相关匹配跟踪, 切换时目标图像已占整个视场的三分之二以上, 此时干扰弹还没起燃就已经超出视场, 不会干扰对目标的跟踪。远距离的图像处理系统首先对图像进行空间滤波, 提高信噪比, 然后从中检测出可能的目标并对目标进行标记, 根据标记出目标的各种特征识别出真实的目标再对其进行跟踪。

抗干扰的第一步是先要判定是否出现了干扰。通过对现有的各种红外图像资料分析, 干扰出现前帧与帧之间的灰度和面积变化很小, 而干扰出现之后, 目标区的灰度和面积明显增大。因此, 可以认为跟踪过程中若目标灰度显著增加、面积骤然增大, 运动状态突然改变, 则可能出现了干扰。如果判断出现干扰, 就转入抗干扰跟踪算法。首先应将干扰出现前的目标特征保存下来, 将其冻结, 并以目标出现前的检测门限进行目标分割, 计算各目标的特征, 生成目标链, 与干扰出现之前的目标特征进行匹配, 找出跟踪对象。这里有两个阶段: 一是干扰刚出现时, 目标、干扰融合在一起, 形成一个大目标, 这时应维持对此目标的跟踪; 二是目标、干扰已经分离, 跟踪窗内分割出两个区域, 这时应该将两个区域的特征与干扰弹出现之前的特征进行匹配, 经过若干帧的考察识别出真正的目标。如果干扰接连出现, 使得跟踪窗内有几个干扰区域, 目标一直被干扰弹遮挡, 这时就应该利用目标的方向信息和速度信息始终跟踪最后一次抛出的干扰弹, 直至目标、干扰分离, 再按前面论述的方法识别出真实目标。

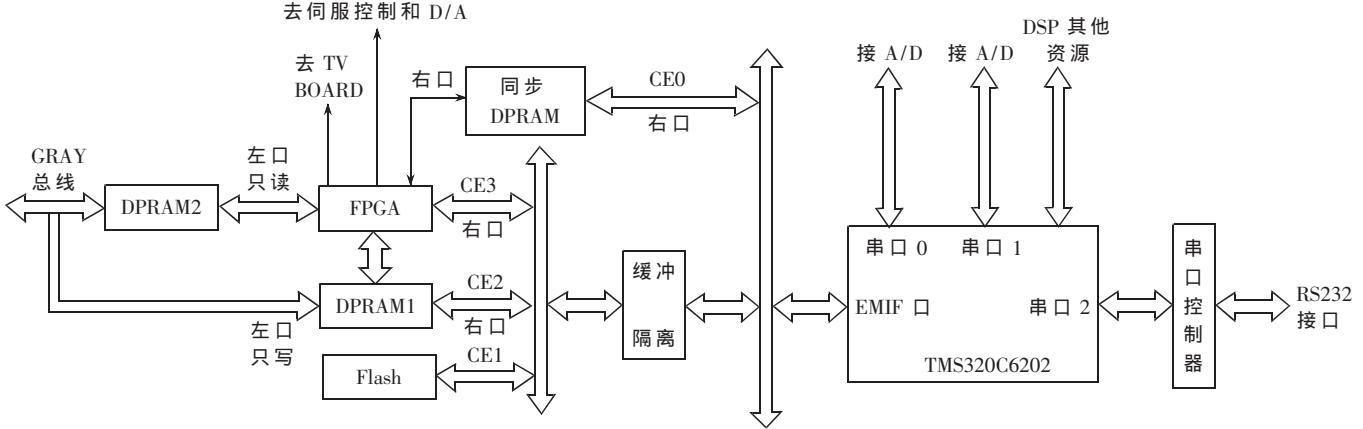

图 1 系统原理图

本系统是一个基于 C6202 DSP 芯片的高速数字信号处理板,包括一片 C6202,一片用于存储 DSP 程序的 Flash ROM,一片 XILINX 公司的 XCV600E,一片同步 DPRAM,两片异步 DPRAM,一个 RS232 串口控制器。该板通过自定义底板总线和系统中的其他板接口。另外板上还留有自定义背板接口,背板上完成 A/D、D/A 功能。信号处理板的原理图如图 1 所示。

## 2 硬件设计

### 2.1 C6202 部分的设计<sup>[3]</sup>

在本系统中,选用 TI 公司的 C6000 系列 DSP 作为系统的图像处理芯片,FPGA 产生系统的时序,对 DSP 的处理速度进行优化。C6202 能否正常工作,从原理角度来分析只与芯片本身一些信号的设置有关系。因为本信号处理板上 C6202 的 XBUS 没有用到,所以将其设为无效,对 XBUS 工作时信号的参数所进行的设置也将没有意义,不会影响 DSP 的工作。

#### (1)C6202 的地址空间设计

C6202 的地址空间被分为 CE0、CE1、CE2 和 CE3 四部分。在本系统中各部分具体设计如下:

①CE0 的访问对象为同步 DPRAM 存储器,地址范围映射到 0x004000000~0x0043fff,但此时 EMIF 需设置为 0x00000040,而且该接口是一个 32bit 的接口,但只用了其低 16bit。

②CE1 的访问对象为 Flash,地址范围为 0x014000000~0x0147ffff,EMIF 设置为 0xfffffff03,EMIF 只在写 Flash 时需要设置。

③CE2 的访问对象为异步 DPRAM 存储器,地址范围映射到 0x02000000~0x0200fffc,EMIF 设置为 0x20D20321,而且该接口是一个 32bit 的接口,但只用了其低 16bit。

④CE3 的访问对象为 FPGA,地址范围映射到 0x03000000~0x03ffff,EMIF 设置由用户定义,CE3 的片选信号同时引到了 FPGA 和系统总线接插件上,FPGA 被当作 DSP 的异步外设来访问。

#### (2)C6202 的外中断分配设计

C6202 有七个外部中断和一个全局中断 NMI。其中 EXT\_INT4 用于 12 800Hz 中断,信号来自 FPGA;EXT\_INT5 和 EXT\_INT6 用于 A/D 中断;EXT\_INT7 用于 RS232 串口中断,该信号来自串口控制器。外部中断的极性是可编程的,上电时是上升沿中断,由 EXTPOL 寄存器来设置极性。

#### (3)C6202 的串口分配设计

C6202 有三个串口,串口 0 和串口 1 用于 A/D 采样数据通道的数据通信,串口 2 用于通过 RS232 的串口控制器与标准 RS232 设备通信。另外,C6202 的通用输出管脚 DMAC0..3 和 TOUT0..1 引到了 FPGA 上,DSP 可以通过这些信号对 FPGA 进行控制,或者用作 DSP 程序中的状态指示信号,DMAC3 同时驱动一个 LED 灯,可用来指示 DSP 上电时加载程序是否正确。

### 2.2 FPGA 部分的设计

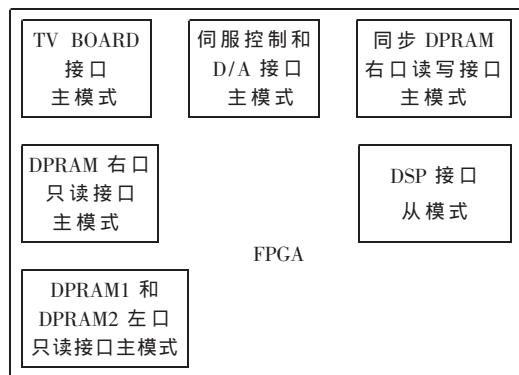

FPGA 是该图像信号处理板上的另外一个核心器件,在其上要实现比较复杂的功能接口和逻辑,其内部要实现的功能框图如图 2 所示。

图 2 FPGA 功能框图

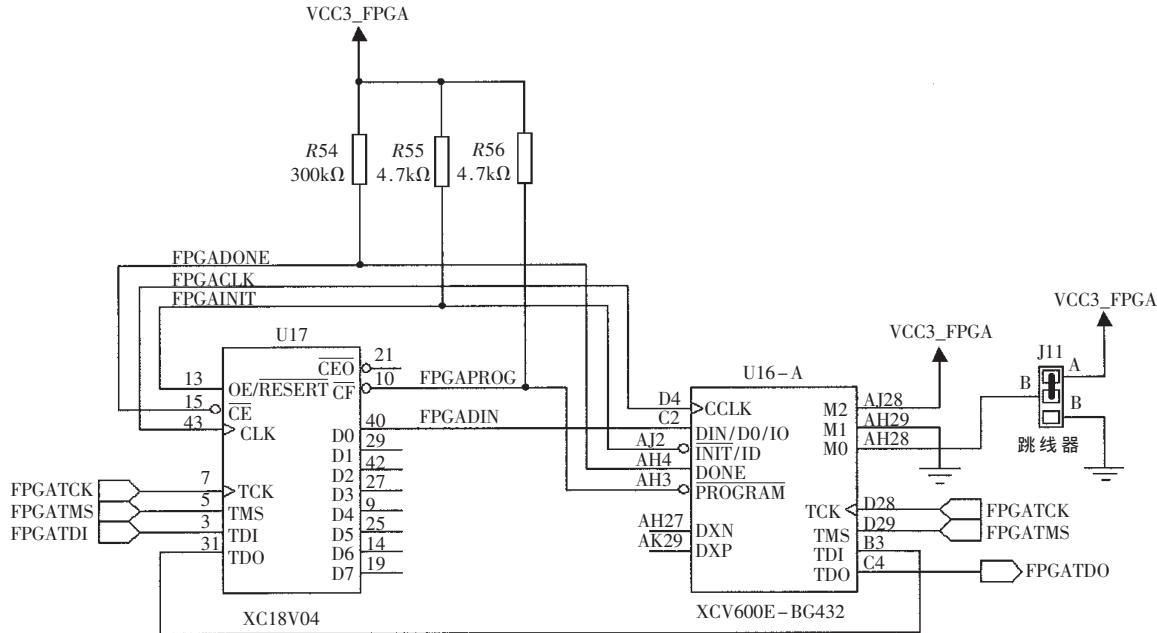

XCV600E 芯片通过一片 PROMs XC18V04 进行配置,其配置电路如图 3 所示。配置模式有 Slave-Serial Mode、Master-Serial Mode、Slave SelectMAP Mode、Master SelectMAP Mode 和 Boundary (JTAG, IEEE1532) Mode 五种

图 3 FPGA 配置电路

<sup>[4]</sup>。由 XCV600E 上的模式控制管脚 M2、M1 和 M0 来设置不同的配置模式。本系统只采用了 Master-Serial Mode 和 Boundary Mode 两种配置模式，此时模式控制管脚分别为 M [2:0]=0x100 和 M [2:0]=0x101，两种模式之间通过跳线器进行选择。

### 2.3 RS232 串口的设计

C6202 的 McBSP(Multi-channel Buffered Serial Port) 在 SPI 模式下与 MAX3111E 芯片相连，将 C6202 的串口信号转换成标准的 RS232 串口信号。SPI (Series Peripheral Interface) 是一个利用四根信号线的串行接口协议，包括主从模式(Master Mode 和 Slave Mode)接口，这里把 McBSP 配置为 SPI 主模式。

### 2.4 电源设计

本系统从系统总线供电，采用+3.3V 和+5V 电压，背板上用+3.3V、+5V、+27V、-5V 电压。DSP 和 FPGA 的核心电压都是+1.8V，I/O 电压都是+3.3V，两个片子分别通过一片电源芯片 TPS70351 来供电。两个片分开供电是出于对电源芯片自身热耗散的考虑。除了 DSP 和 FPGA 外，其他器件直接从系统总线上得到 3.3V 供电。

### 2.5 复位电路设计

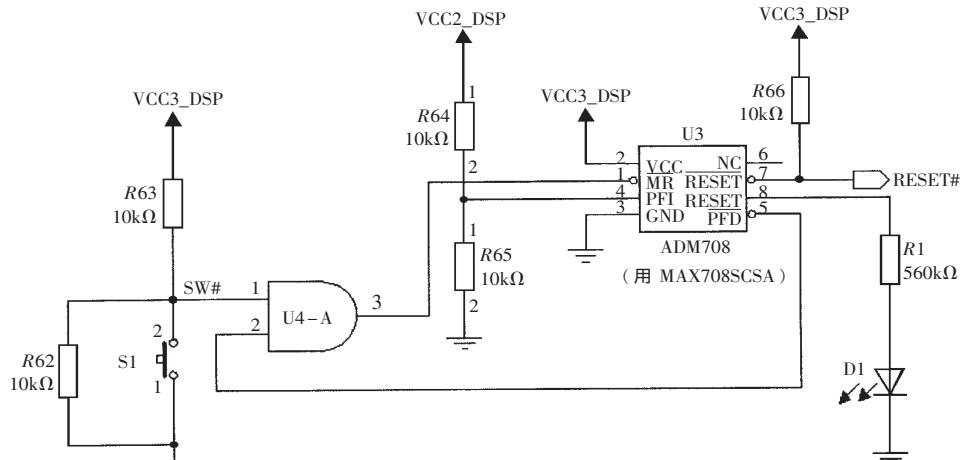

为了调试方便，在电路板上设计了手动复位电路，最终工作时不需要复位信号。复位电路中用了一片 MAX708，除了可以产生手动复位信号外，在上电和掉电时该芯片可以产生复位信号。另外，还可以通过 PFI 管脚监视+1.8V 电压，当 PFI 管脚电压低于+1.25V 时，该

图 4 复位电路

电路也产生复位信号，通过该电路也可以起到保护作用。复位电路如图 4 所示。

### 3 硬件电路测试

PCB 板上有外界通信的串口部分需要测试。利用串口通信对 C6202 的 McBSP 进行配置<sup>[5]</sup>。由于在本图像处理系统中把 C6202 的 McBSP 作为 SPI 的主模式，所以在 McBSP 和串口控制之间只需要连四根线，一根是主设备对从设备的使能，一根是移位时钟，另外两根是串行数据的输入和输出。以下是配置程序中的步骤：

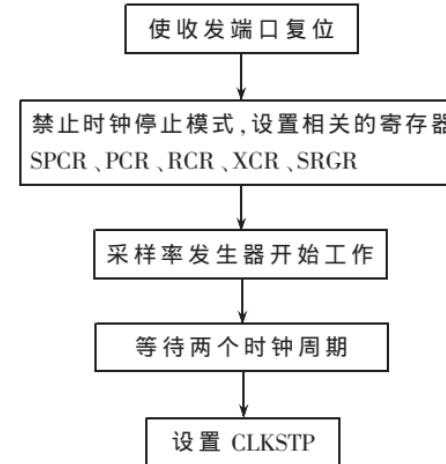

(1) 复位 SPCR 寄存器中的帧同步发生器和采样率发生器，使收发端口复位。

(2) McBSP 在保持复位的状态下，设置有关寄存器。需要注意的是，先设置 CLKSTP=0xB，禁止时钟停止模式，然后设置相关寄存器包括串口控制寄存器 SPCR、管脚控制寄存器 PCR、接收控制寄存器 RCR、发送控制寄存器 XCR 和采样率发生器寄存器 SRGR。

(接上页)

(3) 设置 SPCR 寄存器中 GRST 为 1, 采样率发生器退出复位状态, 开始工作。

(4) 等待两个时钟周期, 以确保 McBSP 在初始化过程中, 内部能够正确地同步。

(5) 设置 SPCR 中 CLKSTP 为相应的值。此时, 需要参考 MAX3111E 的接收时序, 选择上升沿触发。

McBSP 初始化流程如图 5 所示。

本文设计了基于 C6202 和 FPGA 红外成像导引头图像处理系统, 经过系统联调, 能够满足系统设计指标要求。该系统也为数字图像处理算法的实时实现提供了良好的硬件平台, 改善了图像成像质量, 从而提高了导引头的作用距离, 将进一步提高我国红外成像制导技术研究水平。同时由于采用了 DSP 技术, 系统可满足小型化、系统化要求, 使系统的功能便于扩充。

#### 参考文献

- 1 付伟. 红外制导武器的现状及发展趋势[J]. 红外技术, 1999;21(3):8~13

- 2 宋凯英, 岳敏, 杨军等. 对红外成像制导系统干扰效果的

图 5 McBSP 初始化流程图

研究[J]. 西北工业大学学报, 2000;18(1):166~169

3 Texas Instruments Incorporated. TMS320C6202, TMS320C6202B fixed pointed digital signal processors (Rev.1). 2004

4 XILINX Incorporated. Virtex-II platform FPGAs: complete data Sheet. 2005

5 Texas Instruments Incorporated. TMS320C6000 McBSP initialization, 2004

(收稿日期: 2006-05-20)