# 一种多通道同步数据采集预处理电路的设计与仿真

许春康<sup>1</sup>, 李俊<sup>2</sup>, 黄筱调<sup>1</sup>

(1.南京工业大学 机电一体化研究所, 江苏 南京 210009;

2.南京工业大学 自动化学院, 江苏 南京 210009)

**摘要:** 提出了一种多通道同步数据采集预处理电路的设计方案。该方案采用简单可靠的硬件高速锁相环电路控制多通道 A/D 转换器, 保证了同步整周期采样, 实现了相互关联的多路信号的采集。并对整个电路进行了仿真。仿真结果证明了电路设计的正确性。

**关键词:** 多路信号 锁相环 同步采样 仿真

随着我国电力事业的快速发展, 电力系统对发、输、配、用等电量的采集有了更高的要求。但是, 在电量采集过程中, 由于存在谐波、电网频率变化等干扰因素, 很难使采集准确无误。因此, 如何准确、快速地采集电力系统中的各个相互关联的模拟量(例如多路电压、电流等), 一直是电力系统研究中的热点<sup>[1]</sup>。

另外, 在电力测试系统中, 目前使用的装置中的 CPU 多采用 51 系列和 96 系列单片机<sup>[2]</sup>, A/D 芯片的精度为 8 位或 12 位, A/D 芯片的采样速度在  $\mu\text{s}$  级, 普遍存在反应速度慢、连线准确性差、正确动作率低等缺陷。许多电力工作者为此做了长期的努力, 由于受到原理、工艺、技术等方面的限制, 至今未有十分满意的结果, 技术难点主要在于对数据采集的速度、精度以及数据处理的速度要求高<sup>[3]</sup>。

针对上述问题, 本文设计一种基于高速数据处理器(如 DSP)的多通道同步数据采集预处理电路, 并应用目前流行的电路通用分析程序 PSpice 对整个硬件电路进行仿真<sup>[4]</sup>。由于采用高速锁相环电路跟踪锁定电网频率, 实现了多路信号的同步整周期采样。另外, 作为以高速数据处理器为核心控制器的数据采集系统的前置电路, 由于充分利用控制器的高速数据处理能力(指令周期多为 ns 级), 保证了同步数据采集的快速性和准确性。

## 1 硬件电路设计

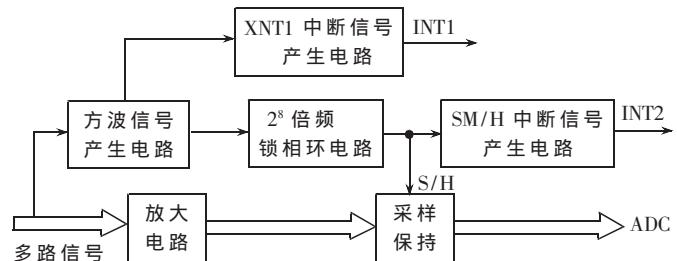

本文提出的预处理电路的输入信号为幅值不超过 1.5V 的多路交流电压信号。原始的多路电压、电流等交流电信号要经过电压或电流互感器转换为幅值不超过 40mA 的交流电流信号(主要考虑到电流中干扰较少), 再经过一定阻值的电阻即可转换为满足上述要求的电压信号。整个电路结构框图如图 1 所示, 主要由放大电路、方波信号产生电路、锁相环电路、XNT1 和 SM/H 中断信号产生电路

图 1 预处理电路总体结构框图

电路以及采样保持电路等五部分组成。

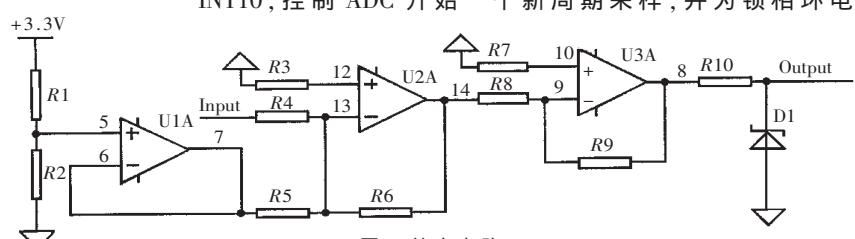

### 1.1 放大电路

为了保证后续的高速数据处理器能够更加简单而快速地进行数据处理, 在这里通过放大电路将多路幅值不超过 1.5V 的交流电压信号均处理为正信号。本设计各路同步数据采集通道的放大电路完全相同, 其中一路如图 2 所示。比较器 U2A、U3A 采用低功耗四运放集成器件, 由于它具有电源电压范围宽、静态功耗小、可单电源使用、价格低廉等优点, 各路独立通道的放大电路均采用这种运放。而 1.5V 基位电压则通过 JFET 高速四运算放大器 U1A 获得。

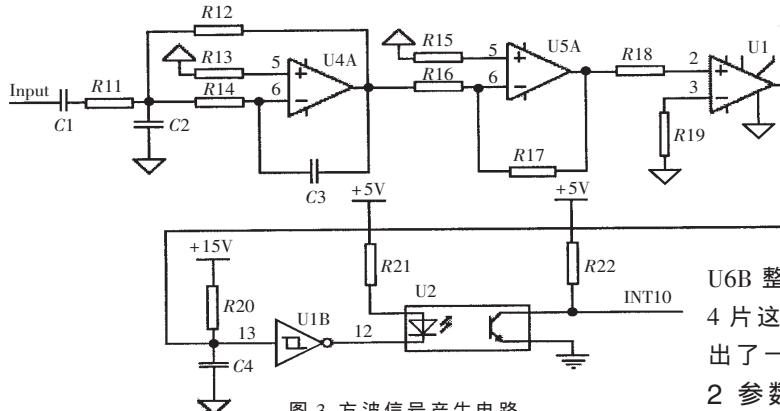

### 1.2 方波信号产生电路

方波信号产生电路如图 3 所示, C1 对输入信号进行直流滤波, 滤除交流电压信号中可能含有的直流分量。R11、R14、R12、C2、C3 与运算放大器 U4A、U5A 构成低通滤波和放大电路, 得到的工频信号经过零比较器 U1、斯密特反相器 U1B 和光耦合器 U2 后, 转换为方波信号 INT10, 控制 ADC 开始一个新周期采样, 并为锁相环电

图 2 放大电路

## 集成电路应用

图 3 方波信号产生电路

路实现同步整周期采样提供参考输入信号。

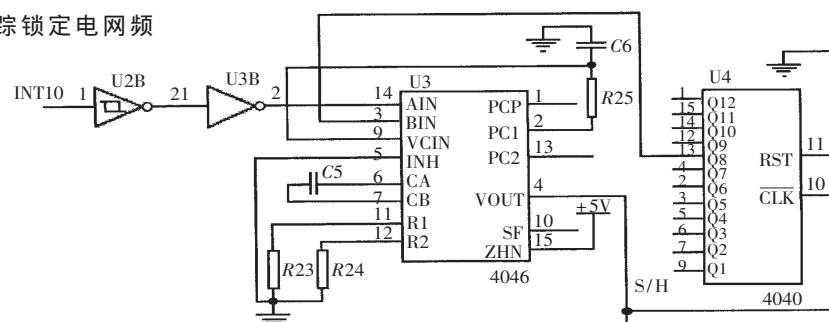

### 1.3 锁相环电路

在电力系统运行中,由于种种原因可能引起电网频率漂移,使得  $N$  个采样点并不均匀地分布在一个整周波内,从而使测量出现误差<sup>[1]</sup>。采用锁相环跟踪锁定电网频率则可解决上述问题,即利用硬件方法实现同步采集<sup>[5]</sup>。这要比使用多路循环采样、软件延时等方法更能保证精度和速度。

锁相环电路如图 4 所示, 方波信号 INT10 经斯密特反相器 U2B 和反相器 U3B 后作为锁相环 4046 的参考输入信号, 电容  $C_6$  和电阻  $R_{25}$  构成锁相环 4046 的环滤波器, 电容  $C_5$ 、电阻  $R_{23}$  和  $R_{24}$  决定 4046 的中心振荡频率。12 级二进制串行计数/分频器 4040 的输出 Q8 接 4046 的比较输入端 BIN, 压控振荡器的输出信号 S/H 进入 4040, 则对 INT10 实现  $2^8$  倍增频。这样  $2^8$  个采样点就均匀分布在被测输入电信号的一个周波内, 从而实现了用硬件方法保证同步采样的目的。

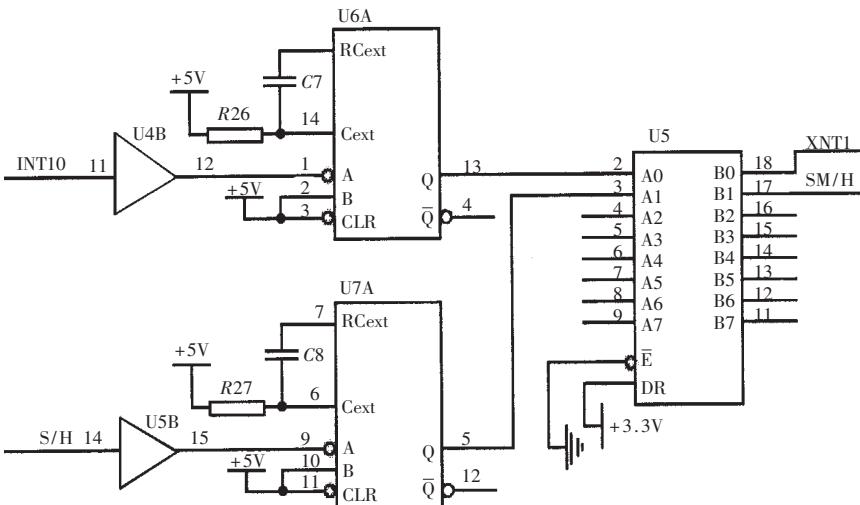

#### 1.4 XNT1 和 SM/H 中断信号产生电路

如图 5 所示, 方波信号 INT10 和被测的输入电信号的  $2^8$  倍增频信号 S/H 在后续要与高速数据处理器的两个外部用户中断引脚相连, 通过它们申请中断。其中, INT10 是 ADC 模块开始一个新周期采样的中断申请信号, 用于保证后面的采集信号和外部被测的输入电信号同步; S/H 则是 ADC 模块进行模数转换的中断申请信号。由于

一般高速数据处理器的外部申请中断为内部上拉，所以在和其相应引脚相连前必须对它们进行适当处理，即将它们处理成脉冲信号，这样外部用户便能正确地申请中断，而控制器也能及时而准确响应中断。

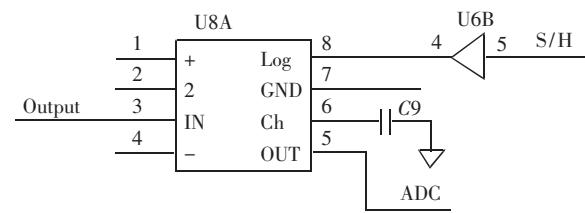

## 1.5 采样保持电路

因为现场信号总是在变化的,而 A/D 转换总是需要一定时间,所以需要把要转换的信号采样后再保持一段

时间,以备转换。在本设计中,采样保持器采用单片采样保持集成器件,其具有价格低廉、采样速度高、下降率低、运行稳定可靠等优点。由于本预处理电路有多路同步数据采集通道,并且可根据控制器的数据处理能力进行扩展,因此需多片这样的采样保持器。考虑到驱动能力,S/H 经单片六同相缓冲/变换器

## 2 参数计算和仿真

本设计对原始信号的一个周期采样 256 个点, 允许工频信号在 40~60Hz 范围内发生波动。在这里, 应用 PSpice 进行仿真, 具体设置如下:

(1) 被测输入信号为  $V(t) = 1.5 \sin(31\Delta t)$ 。

图 4 锁相环电路

图 5 XNT1 和 SM/H 中断信号产生电路

图 6 采样保持电路

# 集成电路应用

(2) 锁相环 4046 采用相位比较器 1, PC1out 同步时其在电压控制振荡器 VCO 的中心频率的相位差为  $90^\circ$ 。由式(1)可确定 VCO 电路的电容  $C_5$  和电阻  $R_{23}、R_{24}$  的值。

$$\begin{cases} f_{\min} = \frac{1}{R_{24}(C_5 + 32\text{pF})} \\ f_{\max} = \frac{1}{R_{23}(C_5 + 32\text{pF})} + f_{\min} \\ f_0 = \frac{f_{\min} + f_{\max}}{2} \\ f_0 = 12800\text{Hz} \end{cases} \quad (1)$$

而决定 PLL 响应特性的环滤波器的电容  $C_6$  和电阻  $R_{25}$  则由式(2)确定。

$$\begin{cases} 2f_c \approx \frac{1}{\pi} \sqrt{\frac{2\pi f_l}{R_{25}C_6}} \\ f_c \leq f_l \end{cases} \quad (2)$$

式中,  $f_c$  为捕捉频率范围,  $f_l$  为锁定频率范围。

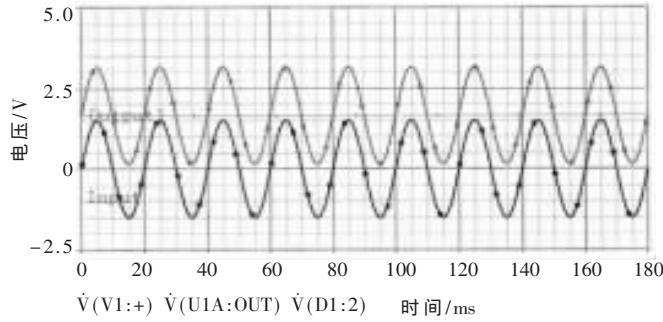

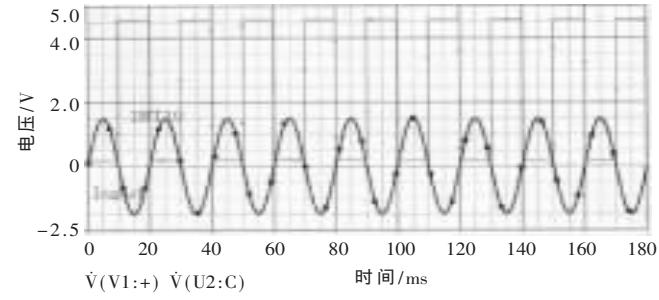

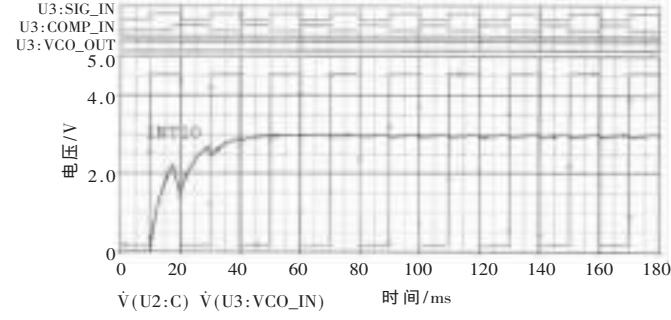

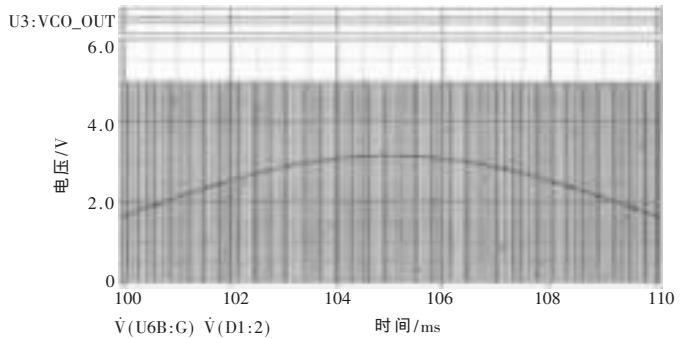

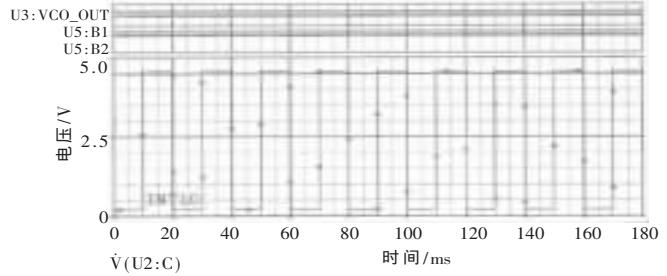

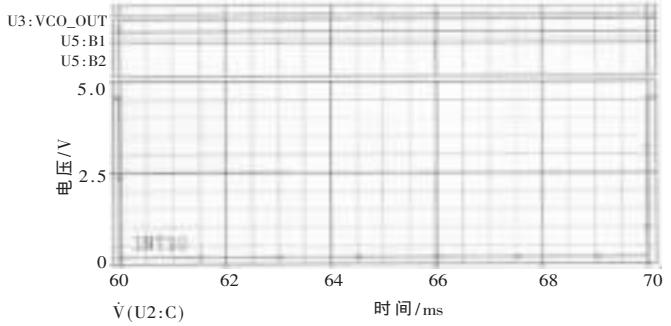

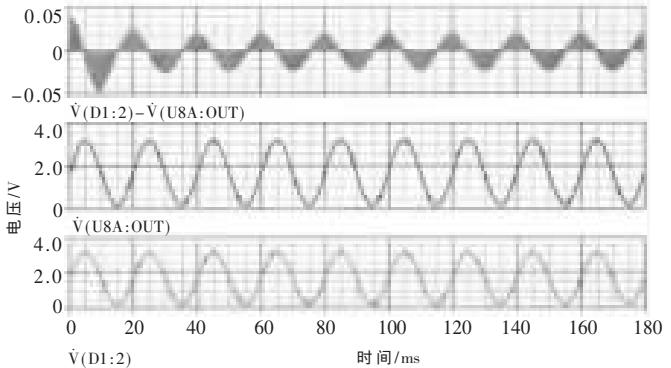

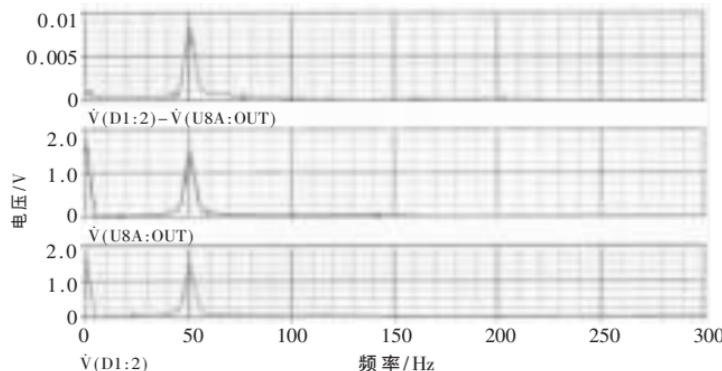

经过仿真可得到放大电路的仿真波形图如图 7, 方波信号产生电路的仿真波形图如图 8, 锁相环电路的仿真波形图如图 9, 采样保持信号仿真波形图如图 10, XNT1 和 SM/H 中断信号产生电路的仿真波形图如

图 7 放大电路的仿真波形

图 8 方波信号产生电路的仿真波形

图 9 锁相环电路的仿真波形

图 11, XNT1 和 SM/H 脉冲信号波形图如图 12, 采样保持器输入信号、输出信号及误差曲线图如图 13, 采样保持器输入信号、输出信号波形图及误差曲线快速傅立叶变换图如图 14。

参看图 8, 通过计算可知方波信号 INT10 超前被测输入信号  $18\mu\text{s}$  左右。这样便可利用其下降沿产生中断申请信号 INT1, 及时启动 ADC 模块开始一个新周期采样, 如图 11 和图 12 所示。

图 10 采样保持信号波形

图 11 XNT1 和 SM/H 中断信号产生电路的仿真波形

图 12 XNT1 和 SM/H 脉冲信号波形

图 13 采样保持器输入、输出信号及误差曲线

图 14 采样保持器输入、输出信号及误差曲线快速傅立叶变换

参看图 9, 由 VCO 输入曲线可知, 锁相环电路在 3 个周期内即可跟上并锁定输入信号, 快速实现对工频信号的 256 倍增频。分析图 11 和图 12 中的中断申请信号 INT1 和 SM/H 可知, SM/H 第一次出现高电平滞后 INT1 约  $30\mu\text{s}$ 。因此对于一个新周期采样, 采样保持信号滞后输入信号约  $12\mu\text{s}$ 。由于一个周期采样 256 个点, 则这个时延基本上可以忽略不计。

参看图 13 和图 14, 对采样保持器输入、输出信号进

行逐点比较可知, 误差在峰峰值处最小, 最大误差不超过  $25\text{mV}$ , 其为后续控制器提供了较高精度的预处理数据。

通过以上分析和仿真可以看出, 本文设计的多通道同步数据采集预处理电路具有结构简单、价格低廉、适应性强和良好的动态特性等诸多优点。其可广泛应用于基于高速数据处理器的同步数据采集系统中, 依靠控制器的高速数据处理能力, 扩展更多通道、采集更多点、进一步降低时延、提高预处理数据的精度。

#### 参考文献

- 1 黄开长, 刘和平, 邓力等. 同步数据采集技术在电力系统中的应用[J]. 仪器仪表学报, 2002; 23(3):494~496

- 2 李广弟, 朱月秀, 王秀山. 单片机基础[M]. 北京: 北京航空航天大学出版社, 2004

- 3 扬旭, 朱斌. 高速多通道同步数据采集 DSP 系统在电力系统中的应用[J]. 暨南大学学报(自然科学版), 2001; 22(3):57~60

- 4 刘湲. PSpice 电路设计与实现[M]. 北京: 国防工业出版社, 2005

- 5 贝斯特. 锁相环设计、仿真与应用[M]. 北京: 清华大学出版社, 2003

(收稿日期: 2006-06-19)