# Active-HDL LE Tutorial

Lattice Semiconductor Corporation 5555 NE Moore Court Hillsboro, OR 97124 (503) 268-8000

April 2008

### Copyright

Copyright © 2008 Lattice Semiconductor Corporation.

This document may not, in whole or part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior written consent from Lattice Semiconductor Corporation.

### **Trademarks**

Lattice Semiconductor Corporation, L Lattice Semiconductor Corporation (logo), L (stylized), L (design), Lattice (design), LSC, E<sup>2</sup>CMOS, Extreme Performance, FlashBAK, flexiFlash, flexiMAC, flexiPCS, FreedomChip, GAL, GDX, Generic Array Logic, HDL Explorer, IPexpress, ISP, ispATE, ispClock, ispDOWNLOAD, ispGAL, ispGDS, ispGDX, ispGDXV, ispGDX2, ispGENERATOR, ispJTAG, ispLEVER, ispLeverCORE, ispLSI, ispMACH, ispPAC, ispTRACY, ispTURBO, ispVIRTUAL MACHINE, ispVM, ispXP, ispXPGA, ispXPLD, LatticeEC, LatticeECP, LatticeECP-DSP, LatticeECP2, LatticeECP2M, LatticeMico8, LatticeMico32, LatticeSC, LatticeSCM, LatticeXP, LatticeXP2, MACH, MachXO, MACO, ORCA, PAC, PAC-Designer, PAL, Performance Analyst, PURESPEED, Reveal, Silicon Forest, Speedlocked, Speed Locking, SuperBIG, SuperCOOL, SuperFAST, SuperWIDE, sysCLOCK, sysCONFIG, sysDSP, sysHSI, sysI/O, sysMEM, The Simple Machine for Complex Design, TransFR, UltraMOS, and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in the United States and/or other countries. ISP, Bringing the Best Together, and More of the Best are service marks of Lattice Semiconductor Corporation.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium in the U.S. and other jurisdictions.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE SEMICONDUCTOR CORPORATION (LSC) OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

LSC may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. LSC makes no commitment to update this documentation. LSC reserves the right to discontinue any product or service without notice and assumes no obligation

to correct any errors contained herein or to advise any user of this document of any correction if such be made. LSC recommends its customers obtain the latest version of the relevant information to establish, before ordering, that the information being relied upon is current.

### **Type Conventions Used in This Document**

| Convention        | Meaning or Use                                                                                    |  |

|-------------------|---------------------------------------------------------------------------------------------------|--|

| Bold              | Items in the user interface that you select or click. Text that you type into the user interface. |  |

| <italic></italic> | Variables in commands, code syntax, and path names.                                               |  |

| Ctrl+L            | Press the two keys at the same time.                                                              |  |

| Courier           | Code examples. Messages, reports, and prompts from the software.                                  |  |

|                   | Omitted material in a line of code.                                                               |  |

|                   | Omitted lines in code and report examples.                                                        |  |

| [ ]               | Optional items in syntax descriptions. In bus specifications, the brackets are required.          |  |

| ( )               | Grouped items in syntax descriptions.                                                             |  |

| { }               | Repeatable items in syntax descriptions.                                                          |  |

| I                 | A choice between items in syntax descriptions.                                                    |  |

# Contents

| ACTIVE-HUL LE TUTORIAI 1                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Learning Objectives 1                                                                                                                                                         |

| Time to Complete This Tutorial 2                                                                                                                                              |

| System Requirements 2                                                                                                                                                         |

| Accessing Online Help 3                                                                                                                                                       |

| About the Tutorial Design 3                                                                                                                                                   |

| About Lattice Edition (LE) 3                                                                                                                                                  |

| Task 1: Setting Up Project Navigator to Start Active-HDL 4                                                                                                                    |

| Task 2: Create a New Project 6                                                                                                                                                |

| Task 3: Functional Simulation 8                                                                                                                                               |

| Task 4: Browsing the Design 11                                                                                                                                                |

| Task 5: Source-Level Debugging 12 Controlling the Simulation with a Code Breakpoint 12 Controlling the Simulation with a Signal Breakpoint 14 Viewing Instantaneous States 16 |

| Task 6: Waveform Analysis 17 Adding Port and Signal Objects 17 Adjusting the Waveform View 18 Measuring the Time Between Waveform Events 20                                   |

| Task 7: Scripting a Simulation 22                                                                                                                                             |

| Task 8: Interactive Simulation 24 Running Active-HDL LE in Interactive Mode 24 Examining HDL Compiler Options 29 Compiling Design Source Files 30                             |

| Summary 32                                                                                                                                                                    |

| Glossary 33                                                                                                                                                                   |

| Recommended References 33                                                                                                                                                     |

# Active-HDL LE Tutorial

This tutorial leads you through a typical simulation scenario using Active-HDL Lattice Edition (Active-HDL LE) as the simulation environment for ispLEVER. The tutorial design models a project using both VHDL and Verilog HDL blocks. It shows you how to set up ispLEVER and Active-HDL LE so you can use them interactively to manage a simulation run, use basic simulation and HDL debugging features, perform waveform analysis, and write scripts.

Although this tutorial emphasizes the feature set provided with Active-HDL LE, you can use all procedures described with more advanced versions of the Aldec Active-HDL product line.

## **Learning Objectives**

When you have completed this tutorial, you should be able to do the following:

- Configure the ispLEVER Project Navigator to use Active-HDL LE as the default simulator.

- Execute simulation and perform HDL debugging tasks.

- Perform waveform analysis.

- Create scripts to automate simulation tasks.

- Use Active-HDL LE in both batch or interactive simulation scenarios.

This tutorial emphasizes using Active-HDL LE exclusively as a simulator launched as a "point" tool from the ispLEVER Project Navigator. Other Active-HDL licenses may include design entry features, such as schematics, state machines, and IP generators, and project management features that can be used to complement a Lattice Semiconductor FPGA design flow. Refer to the tutorial resources in the Aldec Active-HDL online help for more information.

# **Time to Complete This Tutorial**

The time to complete this tutorial is about 90 minutes.

# **System Requirements**

The following software configuration is required to complete the tutorial:

- Active-HDL Lattice Edition 7.3 or later

- ispLEVER-Starter (7.1 or later): FPGA Module and Precision RTL Synthesis Module

or

ispLEVER (7.1 or later) and Mentor Graphics® Precision® RTL Synthesis for Lattice

or

ispLEVER (7.1 or later) and Synplicity<sup>®</sup> Synplify Pro<sup>®</sup>

### **Note**

Synplify for Lattice does not support concurrent synthesis of Verilog HDL and VHDL source.

Active-HDL LE Tutorial Accessing Online Help

# **Accessing Online Help**

You can find online help information on any tool included in the tutorial at any time by pressing the F1 key. Both ispLEVER Project Navigator and Active-HDL LE respond to F1 in a similar way.

# **About the Tutorial Design**

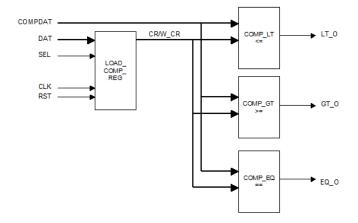

The small design in this tutorial consists of both VHDL and Verilog HDL blocks targeted to a LatticeECP2M FPGA device. The block diagram in Figure 1 illustrates the design. Three comparator blocks evaluate the COMPDAT input data against the value of a storage register. Most of the model is coded in VHDL, and the COMP\_EQ block is coded in Verilog.

Figure 1: Tutorial Design

# **About Lattice Edition (LE)**

Lattice Edition is a special configuration of Aldec Active-HDL that includes features focused on the needs of the FPGA designer, including mixed-language support, a variety of debugging tools, and powerful documentation and visualization tools. Figure 2 illustrates its architecture and major features.

**Design Entry Tools** HDL Language Waveform **IPexpress** Editor Assistant Editor IP: Obfuscated Verilog Module: VHDL or Verilog **HDL Testbench Control Tools Debugging Tools** VHDL Design Browser Processes Compiler Compiler Design Flow Manager Watch/Debug Simulator Kernel Library Manager Call Stack Console Follow Object Waveform List Data Flow Viewer Viewer Memory Simulation Output Viewers

Figure 2: Architecture and Features of Active-HDL LE

# Task 1: Setting Up Project Navigator to Start Active-HDL

In the following procedure, you will configure the ispLEVER Project Navigator to use Active-HDL LE as the default HDL simulator. Whenever a simulation-related process is run from within Project Navigator, Active-HDL LE is launched with a script to compile the simulation file list and run a default simulation based on the test bench.

To configure Project Navigator to start Active-HDL:

- 1. Start the ispLEVER Project Navigator, if it is not already running.

- 2. From Project Navigator, choose **Options > Environment**.

- The Environment Options dialog box appears.

- 3. Click the **Directories** tab, then click the browse (...) button next to the Active-HDL box.

- The Set Active-HDL Install Path dialog box appears.

- 4. Select the folder where the Active-HDL LE executable file (ahdl.exe) is installed, for example, c:\Program Files\Aldec\Active-Hdl < version>\bin.

The directory for Active-HDL LE appears in the ActiveHDL box in the Directories tab of the Environment Options dialog box, as shown in Figure 3.

Figure 3: Active-HDL LE Directory in Environment Options Dialog Box

5. Click OK.

The Active-HDL LE button The Active-HDL LE but

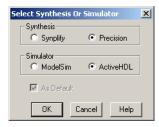

- 6. Choose Options > Select RTL Synthesis or Simulator.

- In the Synthesis box of the Select Synthesis or Simulator dialog box, choose Precision.

- In the Simulator box, choose ActiveHDL.

Figure 4 illustrates these settings.

Figure 4: Select Synthesis Or Simulator Dialog Box

9. Click OK.

# Task 2: Create a New Project

The ispLEVER software employs the concept of a project. A project is a design. Each project has its own directory in which all source files, intermediate data files, and resulting files are stored. To begin a new project, you must create a project directory. Then you must give the project file a name with a .syn suffix. The Project Navigator will use this file name later to reload the project.

Since this tutorial incorporates a combination of VHDL and Verilog source files, a mixed-language-type project is required.

#### **Note**

If you want to preserve the original tutorial design files, save the active\_hdl\_tutor directory to another location on your computer before proceeding.

To create a new project:

- 1. Start the ispLEVER Project Navigator, if it is not already running.

- 2. In the Project Navigator, choose File > New Project.

- 3. In the Project Wizard dialog box, enter or select the following:

- a. In the Project Name box, enter compare.

- b. In the Location box, enter the following directory:

- <install\_path>\examples\Tutorial\active\_hdl\_tutor

- c. In the Design Entry Type box, select Mixed Verilog/VHDL.

- d. In the Synthesis Tools box, choose **Precision** (or **Synplify** if you have access to a Synplify Pro license).

- e. In the Simulator Tools box, choose ActiveHDL.

- 4. Click Next.

- 5. In the Project Wizard Select Device dialog box, enter or select the following:

- a. In the Family box, choose LatticeECP2.

- b. In the Device box, choose LFE2-6E.

- c. In the Speed Grade box, choose -5.

- d. In the Package type box, choose TQFP144.

- e. In the Operating Conditions box, choose **Commercial**.

- 6. Click Next.

- In the Project Wizard Add Source dialog box, click Add Source. appears.

- 8. In the Import File: (Mixed Verilog/VHDL) dialog box, select the following HDL files:

- comp\_eq.v

- gt.vhd

- It.vhd

- tb\_top.vhd

- top.vhd

### 9. Click Open.

In the Import Source Type dialog box, choose the following source type using the following pattern:

| comp_eq.v  | Verilog Module  |

|------------|-----------------|

| lt.vhd     | VHDL Module     |

| gt.vhd     | VHDL Module     |

| tb_top.vhd | VHDL Test Bench |

| top.vhd    | VHDL Module     |

The file source types tell the Project Navigator how to construct file lists for logic synthesis and simulation. In this case, the VHDL Test Bench, tb\_top.vhd, is included in the file list for simulation but is ignored during the synthesis process.

- 10. Click Next.

- 11. In the The Project Wizard Project Information dialog box, click Finish.

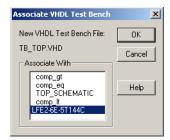

- 12. In the Associated VHDL Test Bench dialog box, shown in Figure 5, choose **LFE2-6E-5T144C** and click **OK**.

Figure 5: Associated VHDL Test Bench Dialog box

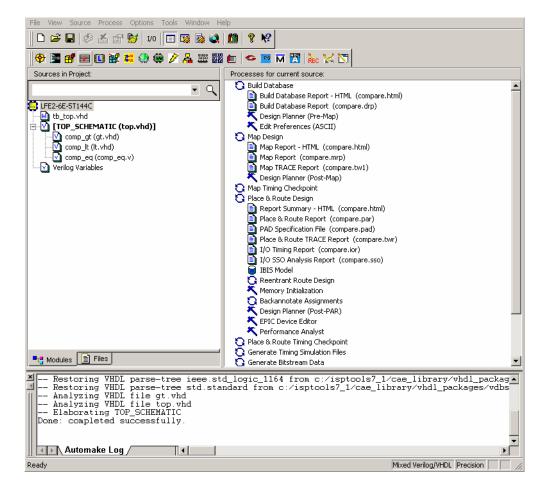

The Project Navigator analyzes all HDL source files and creates a list of modules in the Modules tab of the Sources in Project window, as shown in Figure 6. The VHDL test bench file, tb\_top.vhd, appears with a special icon above top.vhd.

Figure 6: Modules in Modules Tab of Project Navigator

### **Task 3: Functional Simulation**

Functional simulation in the ispLEVER design flow allows you to confirm the behavior of the project model without regard to the timing characteristics of the target device. Delay through the model is either single-unit (1 ps) delay or zero, depending on how the model is constructed. Source files at this stage are typically the register transfer level (RTL) HDL, IP cores, and a test bench to create input stimulus patterns and confirm that the output logic is correct. You may also request a gate-level, post-route functional simulation that reflects the post-synthesis, post-PAR version of the design.

You can access functional simulation in one of two ways from the Project Navigator:

Batch interface, which starts Active-HDL LE using a Tcl script that references the project file list, libraries for the target FPGA, and a default waveform display and run time. No simulation project is created. The batch interface is preferred when the file list is not yet stable and when

there is no need for a simulation project to carry options from session to session.

Interactive interface, which starts Active-HDL LE from the Tools menu (or toolbar) or Start menu. You can create a simulation project and manage the file list and libraries for the target FPGA manually. You can also run and debug the design interactively. The interactive interface is preferred when the project source is more stable and you require intimate control over the simulator that the batch interface does not provide.

This task demonstrates the batch simulation interface. For more information on using Active-HDL LE interactively, see the Active-HDL online help and tutorials.

To run the batch interface to Active-HDL LE:

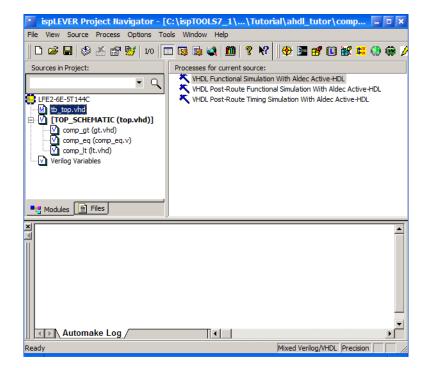

From the Sources in Project window, select tb\_top.vhd.

The Processes for current source window adjusts to display three simulation processes, as shown in Figure 7:

- VHDL Functional Simulation with Aldec Active-HDL

- VHDL Post-Route Functional Simulation with Aldec Active-HDL

- VHDL Post-Route Timing Simulation with Aldec Active-HDL

Figure 7: Simulation Processes in Project Navigator

The tutorial project could have used a Verilog test fixture for stimulus as well. You can use any combination of HDL types within the project, as long as your simulator and synthesis tool is licensed to support mixed HDL.

To run gate-level simulation or gate-level-with-timing simulation based on post-place-and-route data, use either of the Post-Route processes that appear when you select a test bench file.

Double-click the VHDL Functional Simulation with Aldec Active-HDL process.

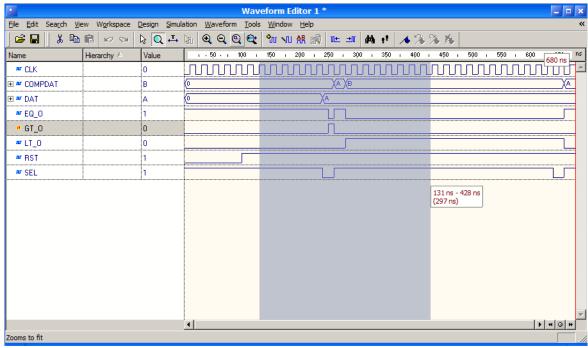

The Active-HDL LE interface appears and runs the batch script produced by Project Navigator. Waveform Editor 1 appears with signal patterns based on the test bench and output of the model.

Click the **Zoom to Fit** button of the Waveform Editor toolbar.

The waveform adjusts so all events are visible in the display, as shown in Figure 8.

Figure 8: Adjusting the Waveform Display

4. Scroll up through the Console tab, noting the Tcl commands issued by the batch interface.

Following is the entire sequence of scripts:

```

tb_top_activehdl.do:

set SIM_WORKING_FOLDER .

do -tcl tb_top.fado

tb_top.fado:

# NOTE: Do not edit this file.

# Auto generated by VHDL Functional Simulation Models

# design create work ./work

design open work/work

do -tcl compare.vfd

```

```

vcom tb_top.vhd

vsim TB_TOP -L pmi_work

do tb_top_vhdf.udo TB_TOP

# End

compare.vfd:

# NOTE: Do not edit this file.

# Auto-generated by All VHDL Functional Simulation Models

source {C:/ispTOOLS7_1/ispcpld/bin/chipsim_cmd.tcl}

set sty_file compare.sty

if {![info exists HasProc(LS_Vcom)]} { source {chipsim_cmd.tcl}

set vcom_opt ""

set src_files {comp_eq.v lt.vhd gt.vhd top.vhd}

LS_Vcom sty_file src_files vcom_opt

# End

tb_top_vhdlf.udo:

-- ispLEVER VHDL Functional Simulation Template:

tb_top_vhdf.udo.

-- You may edit this file to control your simulation.

-- You may specify your design unit. - 1

-- You may specify your waveforms.

add wave *

-- You may specify your simulation run time.

run 1000 ns

```

The details of all the scripts are not important to understand; however, the tb\_top\_vhdlf.udo script provides a means to specify the signals to be traced in the waveform window and default simulation run time. This is a popular file to modify for your project.

## Task 4: Browsing the Design

Many of the debugging and analysis tasks you will perform in the simulator are based on the simulation objects that you select from the Design Browser. Simulation objects refer to elements such as component instances, signals, ports, and variables of the model.

The Structure tab of the Design Browser provides a browser that presents the hierarchical organization of the model. Different icons are used to indicate component instances, signal drivers, and processes. Icons are color-coded to indicate the source format as VHDL or Verilog HDL. As you select objects of the structure, a list of ports, signals, and variable appears below the tree.

Selections that you make in the Design Browser are used to populate a variety of visualization features, such as the Waveform, Watch, and List displays.

To browse the design:

From the Design Browser, click the [+] symbol next to tb\_top (tb), then click the [+] symbol next to UUT: top\_schematic (imp\_top\_schematic) branch.

The details of the instance appear, and the port and signal contents appear in the list below, as shown in Figure 9.

The VHDL objects of the model are colored blue, and the Verilog objects are colored green.

Figure 9: Design Browser

## Task 5: Source-Level Debugging

The source-level debugging features of the simulator enable you to stop the simulation run if certain signal conditions are met or when certain lines of a source file are executed. Stopping the simulation enables you to the examine states of the model as it executes to help detect bugs that lead to incorrect function.

Active-HDL LE provides two breakpoint types: code and signal. A code breakpoint suspends the simulation run when the simulator encounters an executable code statement where a breakpoint is set. A signal breakpoint suspends the simulation run when a model's signal matches a user-defined value.

# Controlling the Simulation with a Code Breakpoint

You will insert a breakpoint into the code to suspend the simulation.

To control the simulation run with a code breakpoint:

- Choose Simulation > Restart Simulation.

The simulation is initialized to time zero (0 ps).

- Select the **Structure** tab of the Design Browser window, if it is not already selected.

- 3. Double-click the test bench module, tb\_top (tb).

The tb\_top.vhd file appears in the HDL editor window.

4. Double-click the top-level HDL module instance, **UUT: top\_schematic** (imp\_top\_schematic).

The top.vhd file appears in the HDL editor window.

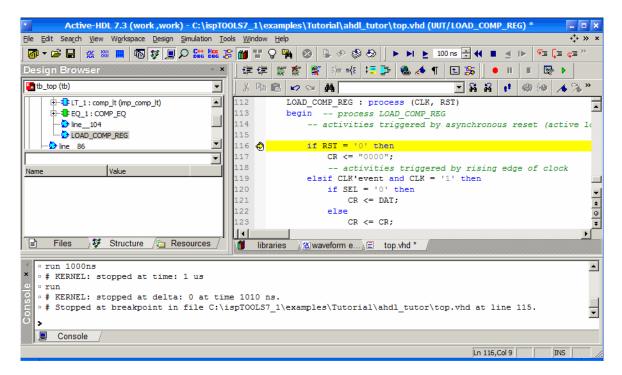

- Scroll to the LOAD\_COMP\_REG process and reset expression (if RST = '0' then) near line 115.

- 6. Press **F9** or click the right mouse button on the reset expression and choose **Toggle Breakpoint**.

A breakpoint icon appears in the left column of the HDL editor.

7. Press Alt+F5 or choose Simulation > Run.

The simulator executes the model until the reset expression is examined. The line of source with the active breakpoint is highlighted, as shown in Figure 10.

Figure 10: Simulation Stopped at Breakpoint

Once the simulator pauses at a breakpoint, you can advance the simulator by using one of four trace options. The trace option that you use depends on what language constructs you wish to examine.

- Trace Into Executes a single statement. If a subprogram call is encountered, the execution descends into the subprogram body.

- Trace Over Executes a single statement. If a subprogram call is encountered, the statements of the subprogram body are executed in a single step.

- Trace Out Executes as many statements as required to complete the execution of a subprogram.

- Trace Over Transition Executes as many statements as are required to perform a transition between states (state machines only).

- 8. Press **F7** (Trace Into) to step the simulator.

This step continues simulation execution, tracing coding line by line. A yellow highlight steps through the source as the model executes.

In some cases, your breakpoint may not be triggered as you expect and the simulator will run indefinitely, as long as events are generated by your model. To interrupt the simulator, press the **Break** button of the toolbar.

Note the difference between Break (toolbar) and End Simulation (Simulation toolbar) features:

- The Break feature interrupts the execution of a run. A signal history recorded in the Waveform or List views is available to you for analysis, and you can continue simulating from the time you requested the break.

- The End Simulation feature both interrupts the simulator and clears the memory. After End Simulation, you must reinitialize the simulator and rerun to establish the in-memory model.

- 9. Select various branches of the Design Browser window.

Port and signal states appear in the lower panel of the window. This feature allows you to examine the state of a port or signal anywhere in the model, even if you did not initially trace it in the waveform window.

- 10. Choose Simulation > Breakpoints.

- 11. In the Breakpoints dialog box, disable the code breakpoint by clearing the check box in the leftmost column. Keep the dialog box open.

# Controlling the Simulation with a Signal Breakpoint

Now you will add a signal breakpoint to suspend the simulation run.

To control the simulation run with a signal breakpoint:

- 1. Click the **Signal Breakpoints** tab in the Breakpoints dialog box.

- 2. Click the Add Signals button.

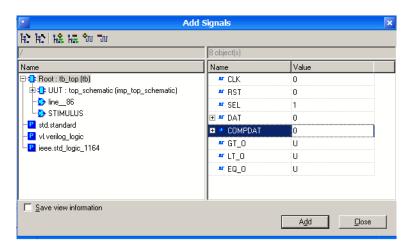

The Add Signals dialog box appears. A display similar to the Design Browser appears. On the left is a tree of the model hierarchy. On the right is a display of ports and signals at the current level of hierarchy.

3. Choose **Root**: **tb\_top (tb)** from the hierarchy browser, then select the **COMPDAT** signal, as shown in Figure 11.

Figure 11: Choosing the COMPDAT Signal in the Add Signals Dialog Box

- 4. Click the Add button.

- COMPDAT is added to the Signal Breakpoints list in the Breakpoints dialog box.

- 5. Click the **Close** button in the Add Signals dialog box.

- 6. Click Edit Condition.

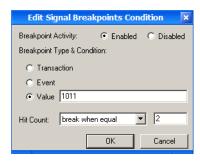

- 7. In the Edit Signal Breakpoints Condition dialog box, select the following options.

- a. In the Value box, enter 1011.

- In the Hit Count box, choose break when equal from the drop-down menu, as shown in Figure 12. In the box to the right of Hit Count, enter 2.

Figure 12: Setting the Breakpoint in the Edit Signal Breakpoints Condition Dialog box

This breakpoint condition triggers the second time COMPDAT reaches the state 1011b (Bh).

- c. Click OK.

- 8. Click **OK** in the Breakpoints dialog box.

- 9. Choose **Simulation > Restart Simulation** to re-initialize the simulator.

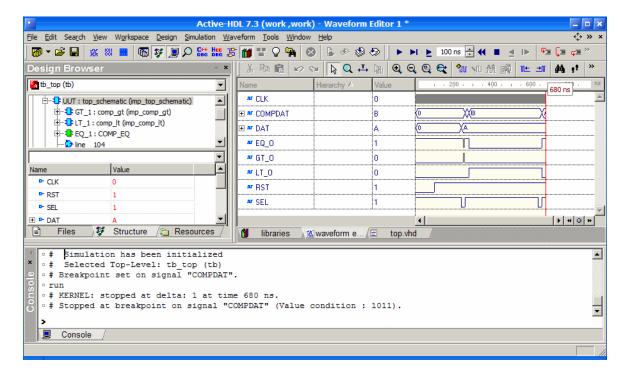

- 10. Press Alt+F5 or the Run button on the toolbar.

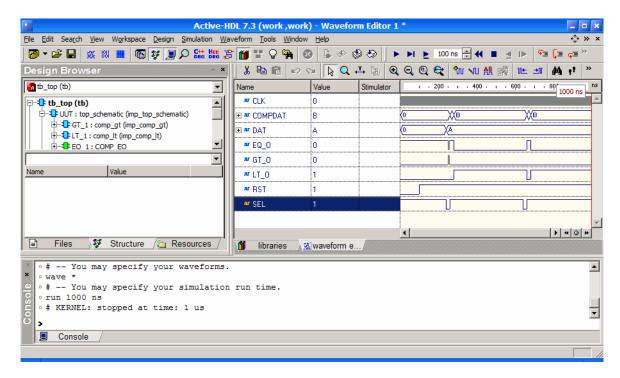

The simulator runs until the COMPDAT signal breakpoint occurs around time 680 ns, as shown in Figure 13 (you may need to click on the Waveform Editor 1 tab to view it).

Figure 13: Reaching the COMPDAT Signal Breakpoint

### **Viewing Instantaneous States**

Once the execution of the simulation has stopped, you can view the instantaneous states of a variable, port, or signal of the model to detect factors causing malfunction.

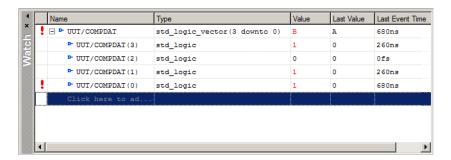

To view the instantaneous states of a variable, port, or signal:

- 1. Choose View > Watch.

- The Watch window appears.

- 2. From the Design Browser window, select **UUT**: top\_schematic (imp top schematic).

- 3. From the Name/Value list of the Design Browser, select **COMPDAT**, then drag and drop it to the Watch window.

Details about the object and current value appear in the display, as shown in Figure 14.

Figure 14: Information on COMPDAT Signal Displayed in Watch Window

# **Task 6: Waveform Analysis**

The waveform display is the most popular means of examining the history of signal and port objects in the simulation model. Several visualization and measurement features are provided to help you better understand the operation of the model and the relationship between signals.

### **Adding Port and Signal Objects**

You can add port and signal objects to the Waveform Editor.

To add port and signal objects to the Waveform Editor:

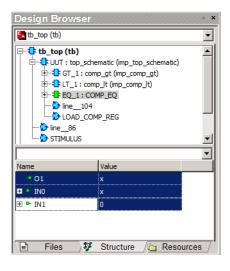

- In the Design Browser, select EQ\_1: COMP\_EQ.

The EQ\_1 ports appear in the list below.

- 2. Select ports **O1**, **IN0**, and **IN1**, as shown in Figure 15, right-click, then select **Add to Waveform**.

Figure 15: Ports Selected in Design Browser

The ports are added to the Waveform Editor. You can also drag and drop simulation objects between many other windows and panes.

3. Right-click the **Name** column header of the waveform view and select **Columns > Hierarchy**.

A new column appears to indicate the hierarchical path (UUT/EQ\_1) to the new ports.

In the Design Browser, select the LT\_1 instance, then drag and drop it onto the waveform window.

Three LT\_1 ports appear in the waveform window.

In the following final steps, you will add signals using an Active-HDL Tcl command.

5. In the Design Browser, select instance UUT.

The UUT signals and ports appear in the list below the hierarchy.

In the Console window, type wave \* at the command prompt and press Enter.

All UUT ports and signals appear in the waveform window.

7. In the Console window, type **run** and press **Enter**.

The simulator advances, and the waveform display shows the state history of all ports and signals traced, as shown in Figure 16.

Hierarchy / . 200 . 600 Name 722 ns • GT\_0 UUT/ LT\_0 HHTZ ► RST UUT/ SEL UUT/ ± M\_CR UUT/ • 01 UUT/EQ\_1/ UUT/EQ\_1/ UUT/EQ\_1/ • 01 UUT/LT\_1/ ± ► INO UUT/LT\_1/ UUT/LT\_1/ 🛣 waveform e.

Figure 16: State History of Traced Ports and Signals

### **Adjusting the Waveform View**

You can adjust the scale of the waveforms in the Waveform Editor.

To adjust the waveform view:

Click the >> icon of the menu bar to detach Waveform Editor 1.

The waveform appears in a stand-alone window.

2. Click the **Zoom To Fit** button on the Waveform Editor toolbar.

The waveform scale changes to fill the window.

3. Right-click on the waveform and choose **Zoom Mode** from the pop-up menu.

The cursor shape changes from Select Mode to a magnifying-glass shape.

4. Select a portion of the waveform by pressing down the left mouse button, dragging the mouse over the period approximately 100 ns-400 ns, and releasing the button. Refer to the Waveform Viewer time scale to select the period.

The waveform scale changes to fill the view with the selected period, as shown in Figure 17.

Figure 17: Changing the Waveform Scale

5. Click the **Zoom To Fit** button (a) on the Waveform Editor toolbar.

The waveform scale changes to fill the window.

## **Measuring the Time Between Waveform Events**

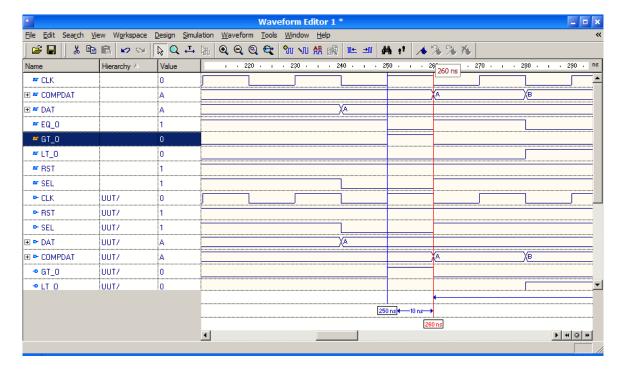

The next procedure demonstrates how to measure the active period of the GT\_O output port. You can do this by positioning cursors or by using Measurement Mode.

# **Positioning Cursors to Measure Time Between Waveform Events**

To measure the time between waveform events by positioning cursors:

- 1. Right-click on the waveform, and choose Select Mode.

- The Zoom Mode is deactivated.

- 2. Right-click on the waveform, and choose Add Cursor.

- A red cursor appears on the display and the time delta between it and the end of the simulation.

- 3. Select the GT\_O signal.

- 4. Select the cursor and drag it to any point in the time line before 250 ns.

- Press the F12 or the Next Event button → of the Waveform Editor toolbar.

- The cursor snaps to the first rising transition of GT\_O.

- Right-click on the waveform and choose Add Cursor.Another cursor appears on the display.

- 7. Select the new cursor and drag it to any point in the time line after 300 ns.

- 8. Press the **Previous Event** button **t** of the waveform view toolbar.

The second cursor snaps to the falling transition of GT\_O. The pulse period is displayed as 10 ns, as shown in Figure 18.

Figure 18: Pulse Period

# **Using Measurement Mode to Measure Time Between Waveform Events**

An alternative to positioning cursors to determine a time delta is to use the Measurement Mode feature to annotate delta and markers between signal events.

To measure the time between waveform events by using Measurement Mode:

- From the waveform display, right-click and choose Measurement Mode.

The cursor changes to the measurement icon.

- 2. Click and hold the left mouse button at the transition from A to B of the COMPDAT signal, then drag the cursor to the right. Release the mouse at an edge of the CLK signal.

A measurement tag is annotated onto the waveform.

You can also create a temporary tag by holding down the Ctrl key when you measure between events. Click on the display to clear the period measurement.

3. Click the << icon of the menu bar.

The Waveform Editor is reattached to the Active-HDL LE frame.

The simulation is initialized.

# **Task 7: Scripting a Simulation**

In many cases, command scripts are faster to execute than the equivalent sequence of actions in the graphical user interface. Active-HDL LE supports batch operation through macro files that you can run from the Console window of the Active-HDL user interface.

For more information on macro commands, see the *Active-HDL Macro Language* section of the Active-HDL LE online help.

#### Note

Advanced versions of Active-HDL provide a stand-alone simulation environment, VSimSA, that is designed for long simulation runs and batch processing from the Windows command line. The Lattice Design Edition Lite license does not support VSimSA.

To create and run an Active-HDL macro file:

1. Choose File > New > Macro.

A new text editor tab appears.

2. Create the following macro script:

```

# Macrol.do

# Create a library

alib work

# Compile the simulation file list

vlog -v2k comp_eq.v

vcom -2002 lt.vhd gt.vhd top.vhd tb_top.vhd

# Initialize

vsim TB_TOP -L pmi_work

# Save simulation data to a VCD text file

vcd file wave.vcd

vcd add -r TB_TOP *

# List all signals in decimal format

list *

wave *

# Advance the simulator 700 ns

run 700 ns

# Quit the simulation

endsim

# End

```

- Save the file as macro1.do.

- 4. At the Console window command prompt, enter the following:

do macrol.do

5. Press Enter.

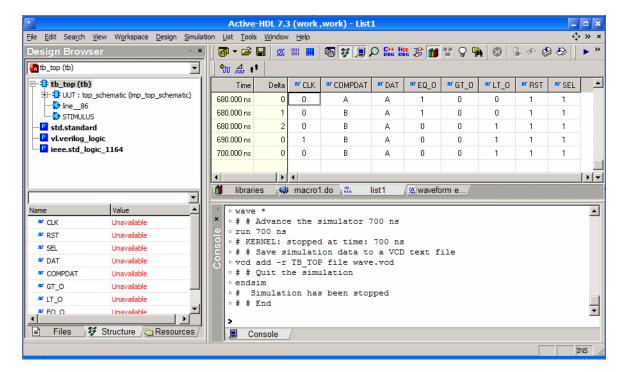

The Active-HDL macro commands are executed. Details appear in the session log. Two new windows appear with list and waveform results of the run, as shown in Figure 19.

Figure 19: Active HDL Windows Showing Run Results

The Verilog value change dump (.vcd) file is stored in the .\ahdl\_tutor\work\work directory. You can open this file to inspect the results or import to other software tools like the ispLEVER Power Calculator for analysis.

- 6. Choose File > Exit.

- 7. Choose **No** in the any Save File? dialog boxes.

The application closes.

### **Task 8: Interactive Simulation**

So far, the tutorial tasks have used the simulator in batch mode. In Task 3, you examined the script created by ispLEVER Project Navigator to compile source files, establish a waveform display, and run for a default period. The batch interface is ideal for rapidly verifying submodules of the design; however, to apply simulator options that will persist between sessions, you must create an Active-HDL Workspace to save environment options and a simulation file list that can be restored.

### **Running Active-HDL LE in Interactive Mode**

In this task, you will use Active-HDL in an interactive style to manage the simulation file list and apply custom HDL compiler options.

To run Active-HDL LE in interactive mode:

From the ispLEVER Project Navigator, choose Tools > Active-HDL Simulator or click the Active-HDL button of the toolbar.

Active-HDL opens, and the Getting Started dialog box appears.

The following steps create an Active-HDL Workspace (.aws) "container" to group designs and resource files related to the simulation. A workspace "design" refers a collection of source files, such as the RTL model and test bench of your project, the compiled library of the simulation, and output results. The Active-HDL LE license supports a single design per workspace.

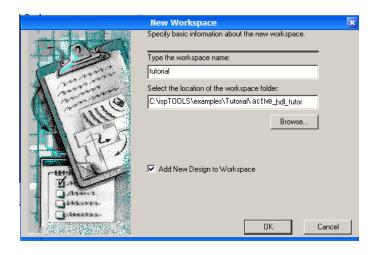

- 2. Choose Create new workspace and click OK.

- In the New Workspace dialog box, type the workspace name, tutorial, and click the Browse button.

- In the Browse for Folder dialog box, select the ispTOOLS

version>\examples\Tutorial\active\_hdl\_tutor folder, as shown in Figure 20, and click **OK**.

Figure 20: Selecting the Workspace Folder in the New Workspace Dialog Box

5. In the New Design Wizard dialog box, select **Create an Empty Design**, as shown in Figure 21, and click the **Next** button.

Figure 21: Creating an Empty Design in the New Design Wizard Dialog Box

The Property Page dialog box appears.

The Create an Empty Design option configures Active-HDL LE to be used primarily for simulation tasks. The Create an Empty Design with Design Flow option enables the Design Flow Manager feature, which is an alternative to the ispLEVER Project Navigator, and provides process flow automation and controls for synthesis, simulation, and place-and-route tools. For more information on using Active-HDL as the primary "frontend" for your FPGA design work, see the Active-HDL online help and tutorials.

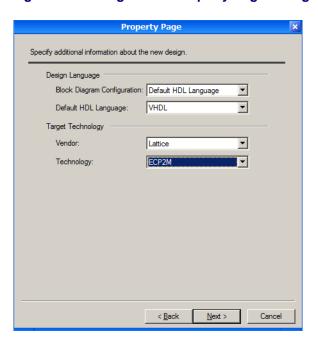

- 6. In the Property Page dialog box, select the following options:

- a. In the Block Diagram Configuration box, choose **Default HDL** Language.

- b. In the Default HDL Language box, choose VHDL.

- c. In the Vendor box, choose **Lattice**.

- d. In the Technology box, choose ECP2M.

The Property Page dialog box should now resemble the illustration in Figure 22.

Figure 22: Settings in the Property Page Dialog Box

e. Click the Next button.

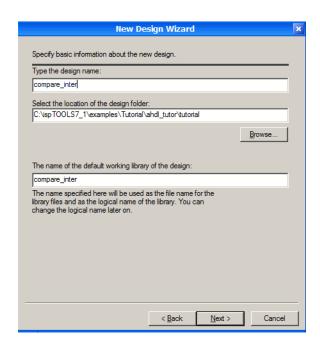

7. In the New Design Wizard dialog box, enter **compare\_inter** as the design name, as shown in Figure 23.

Figure 23: Entering the Design Name in the New Design Wizard Dialog Box

- 8. Click the Next button.

- 9. In the final New Design Wizard dialog box, click the **Finish** button.

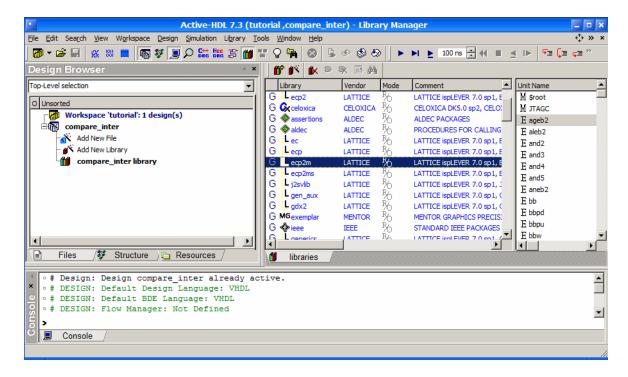

The Design Browser appears with the new Workspace compare\_inter and Library Manager tab libraries.

The Lattice Edition license of Active-HDL provides pre-compiled Verilog and VHDL libraries of gate-level models for all Lattice Semiconductor CPLD and FPGA device families. VHDL libraries are organized by family, typically using the suffix of the device family. For example, the LatticeECP2M family appears as "ecp2" in the list. Verilog library names are preceded by "ovi".

See the Active-HDL LE installation program options for details on library installation.

10. Select ecp2m in the Library list.

The design units compiled into ecp2 appear in the list panel to the right, as shown in Figure 24.

Figure 24: Design Units in the LatticeECP2M Family

To add files to the design:

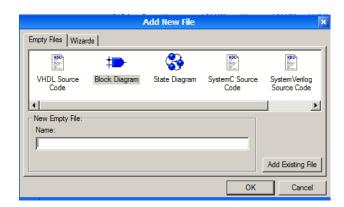

- 1. From the Design Browser, double-click on Add New File.

- 2. In the Add New File dialog box, shown in Figure 25, click the **Add Existing File** button.

Figure 25: Add New File Dialog Box

3. In the Add Files dialog box, browse to the \ispTOOLS<\version>\examples\tutorial\active\_hdl\_tutor folder, and select the following source files:

- comp\_eq.v

- gt.vhd

- It.vhd

- tb top.vhd

- top.vhd

### 4. Click Add.

The files are listed below the compare inter design in the Design Browser.

The numbers in the left-hand margin of the file list indicate the order in which the files will be compiled by the simulator (1 first, 2 second, and so on.). The file list order is important to ensure that objects referenced by one model are defined before they are used. For this project, top.vhd must be in position 4, and to top.vhd must be in position 5.

5. Organize the file list by dragging and dropping to put top.vhd in position 4 and tb\_top.vhd in position 5.

## **Examining HDL Compiler Options**

In this task, you look at the compilation options available for Verilog and VHDL.

To examine HDL compiler options for the active design:

- 1. Choose **Design > Settings**.

- 2. From the Category list in the Design Settings dialog box, choose **Compilation > Verilog**.

Verilog settings for the Active-HDL compiler appear. Compiler settings apply to any subsequent runs of the Verilog compiler.

3. From the Category list, choose VHDL.

VHDL settings for the Active-HDL compiler appear. For example, the Standard Version option allows you to indicate against which version of the VHDL standard source the code should be compiled.

4. Disable the Enable Debug option and click **OK**.

The Design Setting dialog box closes.

The Enable Debug option adds information to the simulation database that supports source-level debugging features like single-stepping source code. With large gate-level designs where source-level debugging is less important, disabling this option can improve the simulator's compilation and run-time performance.

#### **Note**

Options in the Design Setting dialog boxes apply to the current workspace or design only. If you want to apply default settings for future workspaces, see the Tools > Preferences dialog boxes.

### **Compiling Design Source Files**

Now you will compile the source files.

To compile design source files:

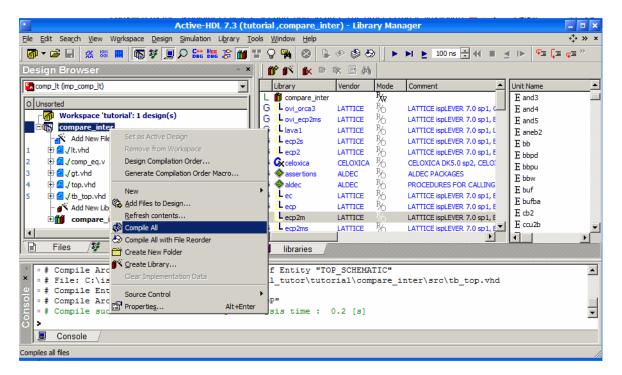

- 1. Choose the **compare\_inter** design from the Design Browser.

- Right-click and choose Compile All, as shown in Figure 26.

The simulator performs a syntax check, then compiles the source files into the compare inter library.

Figure 26: Compiling the Source Files

Information about the compilation appears in the session log of the Console window.

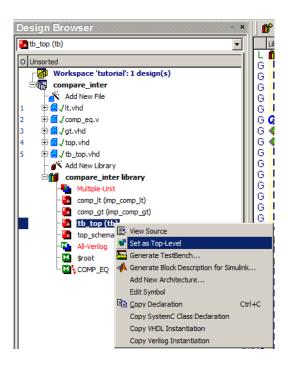

- From the Design Browser, expand the compare\_inter library.

All modules of the project appear in the list. Icons are used to differentiate between VHDL and Verilog objects.

- Select tb\_top (tb) from the list, right-click, and choose Set as Top-Level, as shown in Figure 27.

The library entry appears in bold font.

5. From the Design Browser, select the **Structure** tab.

The design hierarchy appears with tb\_top as the root of the simulation.

6. Choose File > New > Waveform.

A waveform editor appears.

7. Choose Simulation > Initialize.

The simulator engine elaborates the database and initializes all signal and variable states of the model on the basis of the top-level selection made earlier.

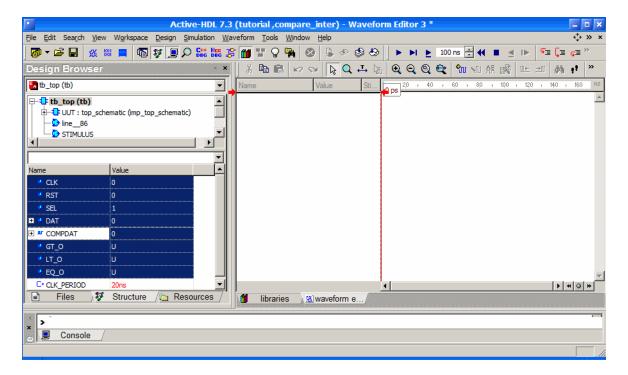

- 8. From the Design View, select **tb\_top (tb)**.

- Signals and constants of the test bench appear in the list.

- 9. Select all the signals, then drag and drop them to the Waveform Editor.

Active-HDL LE Tutorial Summary

The signals appear in the Name list of the Waveform Editor, as shown in Figure 28.

Figure 28: Selecting the Test Bench Signals

- 10. Choose **Simulation > Run Until**.

- 11. In the Run Until dialog box, enter 700 ns and click OK.

The simulator advances to time 700 ns.

- 12. Click the **Zoom to Fit** button (a) of the Waveform Editor toolbar.

- 13. Choose Simulation > End Simulation.

The simulator is initialized and clears memory.

You can now choose to simulate with a new top level or adjust the project to add more files.

14. Choose File > Exit.

Active-HDL LE closes.

## **Summary**

You have completed the Active-HDL Lattice Edition Tutorial. In this tutorial, you have learned how to do the following:

- Set up Project Navigator to launch Active-HDL LE as the default simulator.

- Examine interface scripts issued by Project Navigator.

Active-HDL LE Tutorial Glossary

- Browse simulation objects like signals, ports, component instances, and processes.

- Set source and signal state breakpoints to isolate behavior of the model.

- Create custom waveform displays.

- Measure the time between waveform events.

- Create a macro script to automate several simulator commands.

- Set up an Active-HDL workspace to save the simulation file list and compiler options.

## **Glossary**

Following are the terms and concepts that you should understand to use this tutorial effectively.

**Active-HDL LE** Active-HDL LE is an abbreviation of Active-HDL Lattice Edition.

**HDL** An HDL is a hardware description language, which describes the structure and function of integrated circuits.

**simulation** Simulation is a technology to help verify the behavior of an FPGA design to confirm functional correctness and performance.

**synthesis** Synthesis is the process of translating a high-level design (RTL) description consisting of state machines, truth tables, Boolean equations, or all three into a process-specific, gate-level logic implementation.

**Verilog** Verilog is a language for describing the structure and function of integrated circuits.

**VHDL** VHDL (or VHSIC (Very High-Speed Integrated Circuits) Hardware Description Language) is a language for describing the structure and function of integrated circuits.

### **Recommended References**

You can find additional information on the subjects covered by this tutorial from the following recommended sources:

- Active-HDL Lattice Edition online documentation and tutorials

- support.aldec.com

- ispLEVER online documentation