# 奋斗的小孩之 altera 系列

## 第二十三篇 分频器

对于每一个的小实验，我们都把它看作是一个小项目，逐步的去分析，设计，调试，最后完成功能。下面我们就开始我们的“小项目”。

**项目名称：**分频器

**具体要求：**将本地晶振分频成一定的频率。

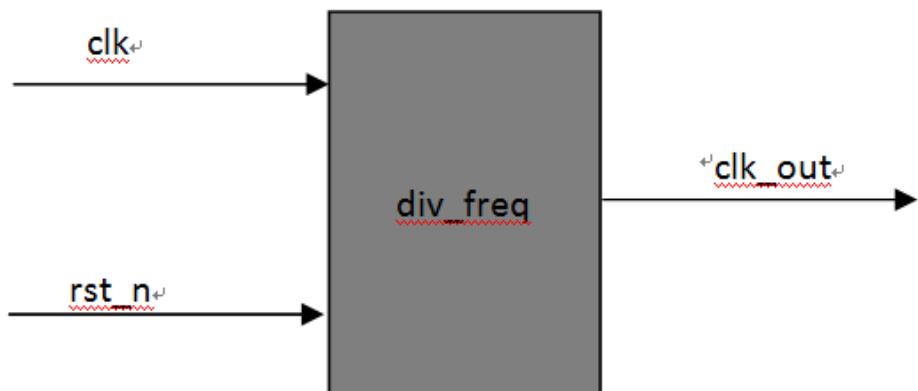

架构图如下：

**系统设计：**

1. 工程的名称：div\_freq。

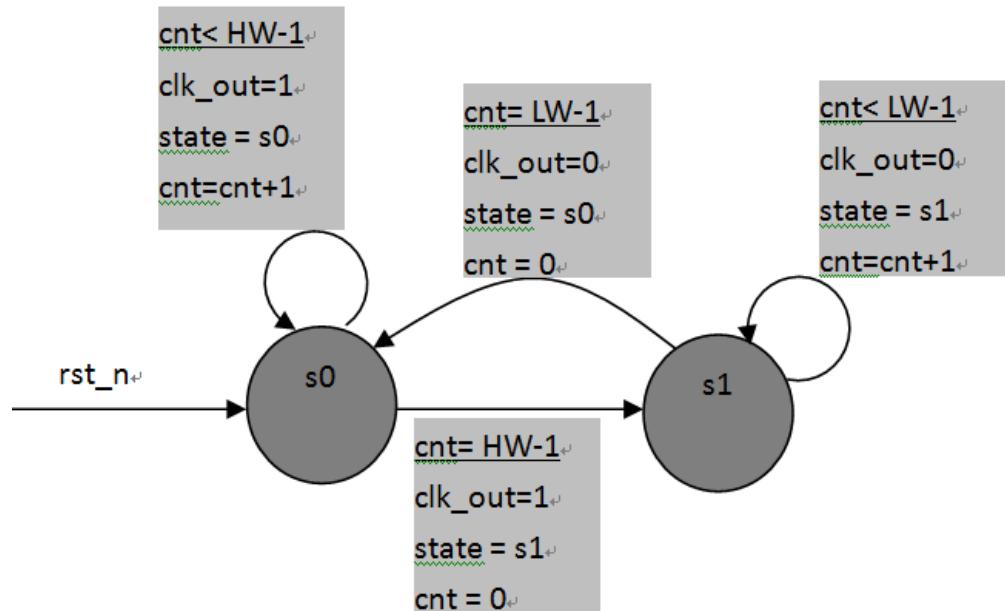

2. 状态转移图如下：

HW: 高电平所占的周期数

LW: 低电平所占的周期数

设计代码如下：

/\*

模块名称: div\_freq

模块功能: 将本地晶振分频成一定的频率且占空比可调

编写时间: 2016-08-22

作者: 至芯科技----奋斗的小孩

邮箱: zxopenhxs@126. com

\*/

```

module div_freq (clk, rst_n, clk_out);

```

```

input clk;

input rst_n;

output reg clk_out;

parameter HW = 50;//高电平的周期数

parameter LW = 50;//低电平的周期数

reg state;

localparam s0 = 1' b0;

localparam s1 = 1' b1;

reg [25:0] cnt;//计数器

always @ (posedge clk or negedge rst_n)

begin

if (!rst_n)

begin

clk_out <= 1' b1;

end

end

```

```

state <= s0;

cnt <= 0;

end

else

begin

case (state)

s0 : begin//高电平

if (cnt < HW - 1)

begin

cnt <= cnt + 1;

state <= s0;

clk_out <= 1'b1;

end

else

begin

cnt <= 0;

state <= s1;

clk_out <= 1'b1;

end

end

```

```

s1 : begin//低电平

if (cnt < LW - 1)

begin

cnt <= cnt + 1;

state <= s1;

clk_out <= 1'b0;

end

else

begin

cnt <= 0;

state <= s0;

clk_out <= 1'b0;

end

end

default : state <= s0;

endcase

end

end

```

endmodule

解析：

笔者想把本地晶振（50MHz）分频到 1Hz，故而将计数器（cnt）的位宽设置为 26 位。本设计中占空比可以通过改变高电平周期数和低电平的周期数来调节，但是并不是所有的占空比都可以实现。

激励代码如下：

/\*

模块名称：div\_freq\_tb

模块功能：为 div\_freq 模块提供激励信号

编写时间：2016-08-22

作者：至芯科技----奋斗的小孩

邮箱：zxopenhxs@126. com

\*/

`timescale 1ns/1ps

module div\_freq\_tb;

reg clk;

reg rst\_n;

```

wire clk_out;

```

```

parameter HW = 3; //仿真时，高电平的周期数

```

```

parameter LW = 2; //仿真时，低电平的周期数

```

```

initial begin

```

```

clk = 1'b1;

```

```

rst_n = 1'b0;

```

```

# 200.1

```

```

rst_n = 1'b1;

```

```

# 2000

```

```

$stop;

```

```

end

```

```

always # 10 clk = ~clk; //本地晶振 50MHz

```

```

div_freq #( .HW(HW), //传递参数

```

```

.LW(LW)

```

```

)

```

```

div_freq_dut(

```

```

.clk(clk),

```

```

.rst_n(rst_n),

.clk_out(clk_out)

);

endmodule

```

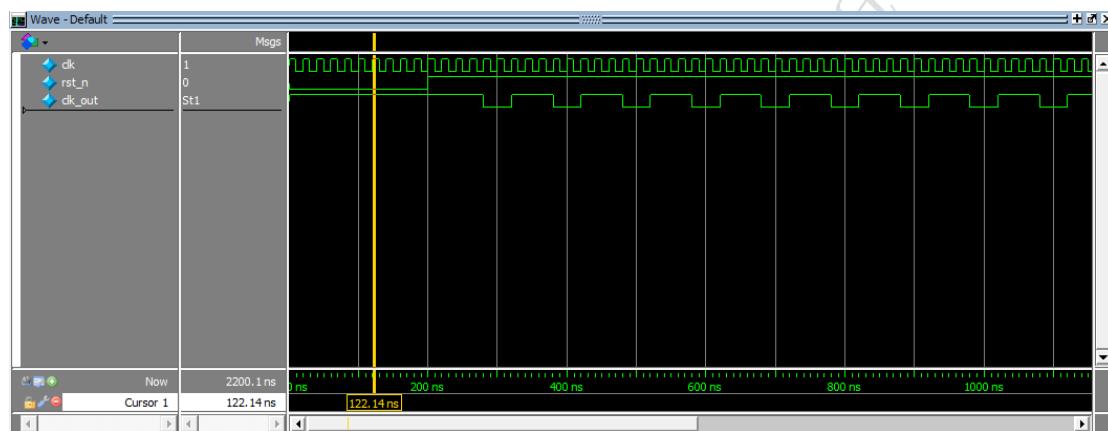

仿真波形如下：

高电平为3个周期，低电平为2个周期。本地晶振是50MHz, 我们分频出来的时钟为10MHz，并且占空比为60%。

如果本地晶振或者输出的时钟和笔者的设计不同，请自行更改设计，以保证设计的正确性。如果还是有不明白的读者可以发邮件到我邮箱或者加群询问。

制作人:奋斗的小孩

fpga 交流群:282124839

至芯科技论坛 [www.fpgaw.com](http://www.fpgaw.com)