# 奋斗的小孩之 altera 系列

## 第十三篇 时序仿真

时序仿真使用布局布线后器件给出的模块和连线的延时信息，在最坏的情况下对电路的行为作出实际地估价。时序仿真使用的仿真器和功能仿真使用的仿真器是相同的，所需的流程和激励也是相同的；惟一的差别是为时序仿真加载到仿真器的设计包括基于实际布局布线设计的最坏情况的布局布线延时，并且在仿真结果波形图中，时序仿真后的信号加载了时延，而功能仿真没有。

那么下面我们就来实现和分析时序仿真：

1. 全编译。

点击：

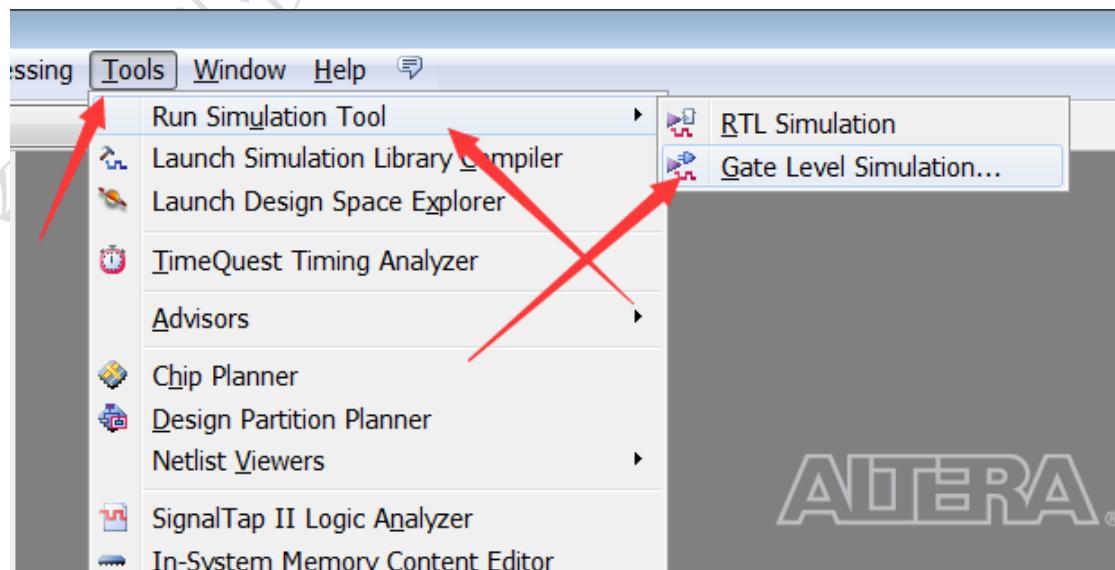

2. 运行仿真工具。

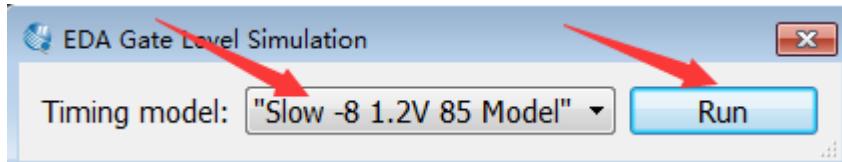

3. 选择模型（保持默认就可以），点击 Run。

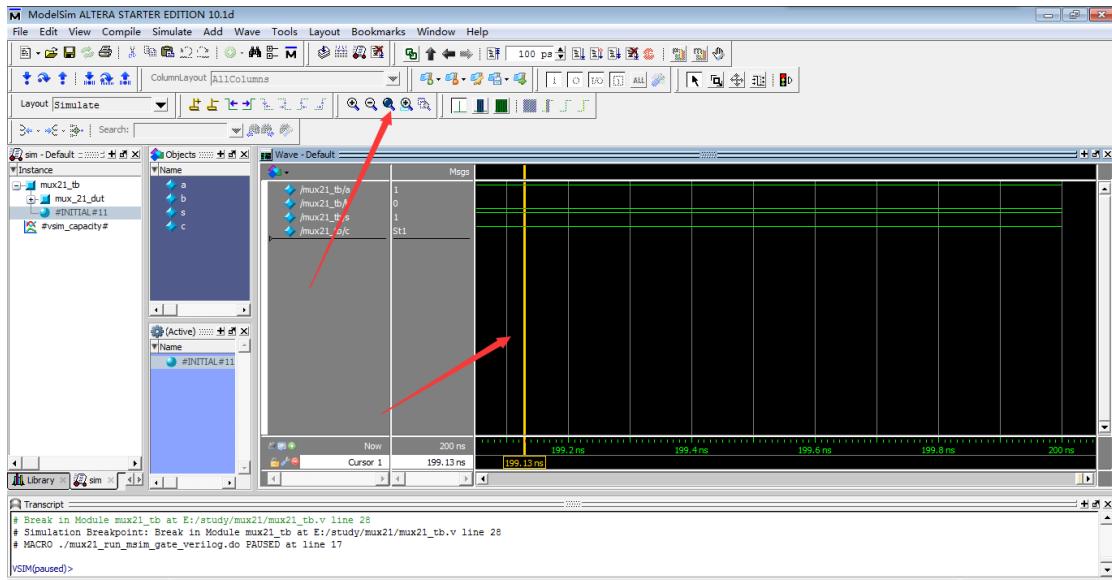

4. 等待 modelsim 出波形。

5. 点击出光标，然后全局缩放。

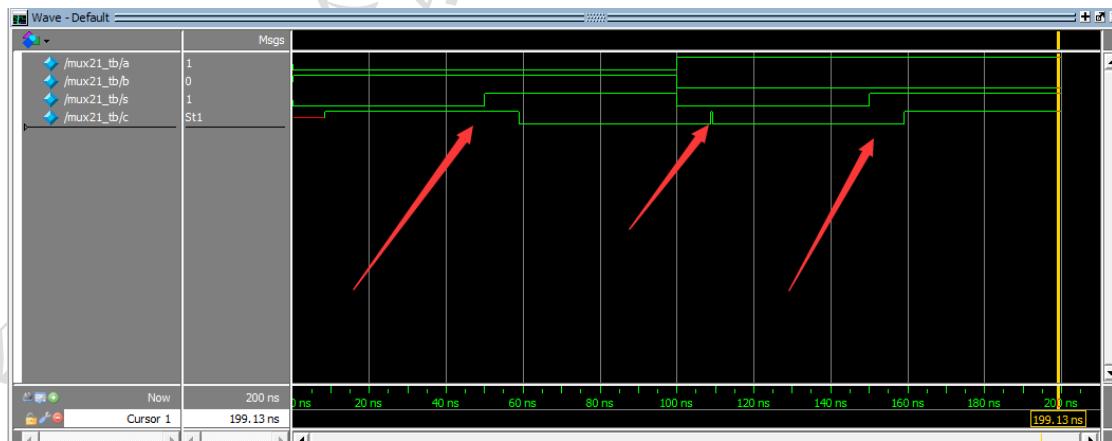

经过查看波形，发现延时输出，并且还有一个小的毛刺。时钟端口、清零和置位端口对毛刺信号十分敏感，任何一点毛刺都可能会使系统出错，因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题。

毛刺并不是对所有的输入都有危害，例如 D 触发器的 D 输入端，只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间，就不会对系统造成危害，我们可以说 D 触发器的 D 输入端对毛刺不敏感。根据这个特性，我们应当在系统中尽可能采用同步电路，这是因为同步电路信号的变化都发生在时钟沿，只要毛刺不出现在时钟的沿口并且不满足数据的建立和保持时间，就不会对系统造成危害（由于毛刺很短，多为几纳秒，基本上都不可能满足数据的建立和保持时间）。

在 fpga 设计当中，尽可能的去用时序逻辑输出。

制作人:奋斗的小孩

fpga 交流群:282124839