## 奋斗的小孩之 altera 系列

### 第十二篇 功能仿真

功能仿真也被称作 RTL 级行为仿真，前仿真，目的是分析设计电路逻辑关系的正确性。缺点：不带有任何的门延时、线延时等等，只是理想情况下的仿真。优点：仿真速度快，可以根据需要观察电路输入输出端口和电路内部任一信号和寄存器的波形；

当添加完激励，我们就可以去调用 modelsim 来进行前仿。在查看波形之前，我们必须知道什么样的波形是正确的，否则，即使仿真出波形也是徒劳的。

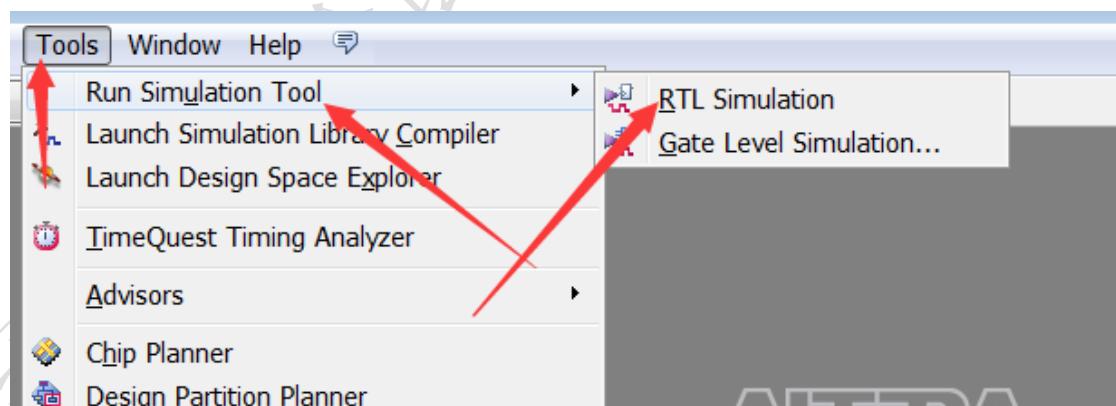

1. 点击前仿真。

2. 等待出波形就可以了。

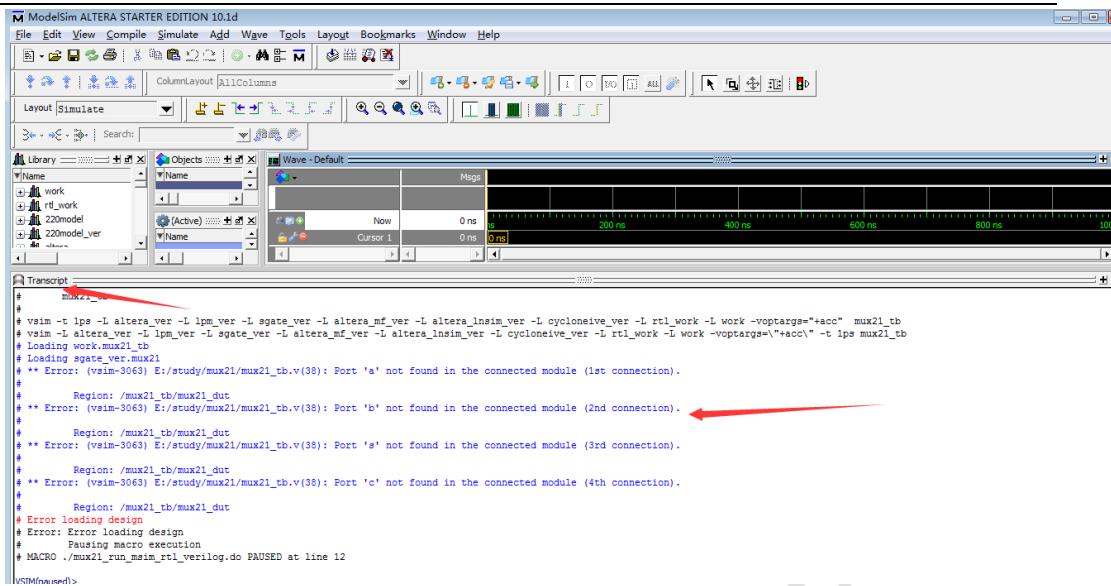

在等待出波形的时候，modelsim 报错，无法仿真。界面如下：

在命令的窗口里面，就报出了错误，说是找不到端口。我们都是按照“规矩”做的呀，那到底那里错了呢？

具体的原因是：我们的代码并没有任何的错误，操作也没有任何的错误，而是我们的工程的名字和 quartus ii 中的二选一多路选择器名称一样，modelsim 在调用的时候，调用了 quartus ii 内部的二选一多路选择器，所以导致找不到端口（笔者提醒大家：再给工程或者设计文件“起名字”时，要注意一些特殊的名字，例如：and、nand、xor、mux21 等等）。

那么怎么就可以用了呢？具体步骤如下：

1. 关闭 modelsim 。

2. 修改顶层实体和激励。

1) 打开 mux21 设计文件，然后点击 file->save as，命名为：

“mux\_21”。

```

abc mux_21.v abc mux2

1 module mux21 (a, b, s, c);

2

3     input a;

4     input b;

5     input s;

6

7     output reg c;

8

9     always @ (*)

10    begin

11        if (s)

12            begin

13                c = a;

14            end

15        else

16            begin

17                c = b;

18            end

19    end

```

2) 将模块名称改成：“mux\_21”。

```

abc mux_21.v abc mux21_tb.v

1 module mux_21 (a, b, s, c);

2

3     input a;

4     input b;

5     input s;

6

7     output reg c;

8

9     always @ (*)

10    begin

```

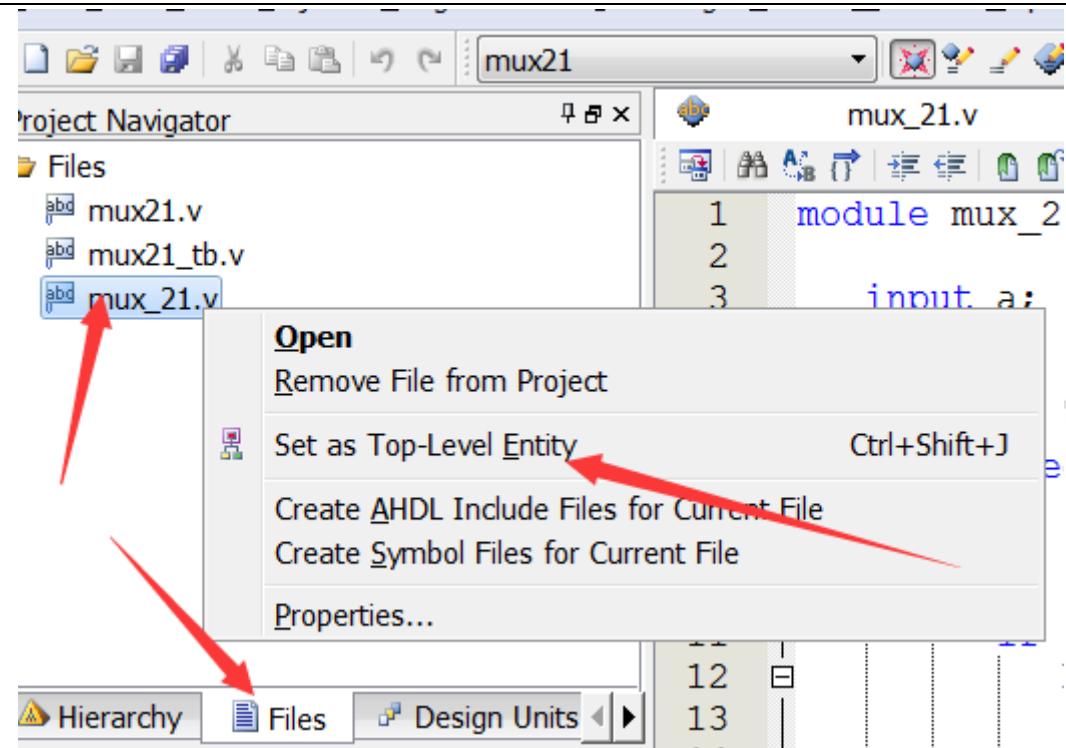

3) 将“mux\_21”设置成为顶层实体。

4) 综合和分析，快捷键“Ctrl + K”。

5) 将激励文件中的例化改成如下：

```

mux_21 mux_21_dut (

.a(a),

.b(b),

.s(s),

.c(c)

);

```

6) 综合和分析，快捷键“Ctrl + K”。

7) 再一次去功能仿真，就可以了（因为我们添加过一次了，

我们只是去修改了代码，所以不用重新添加激励）。

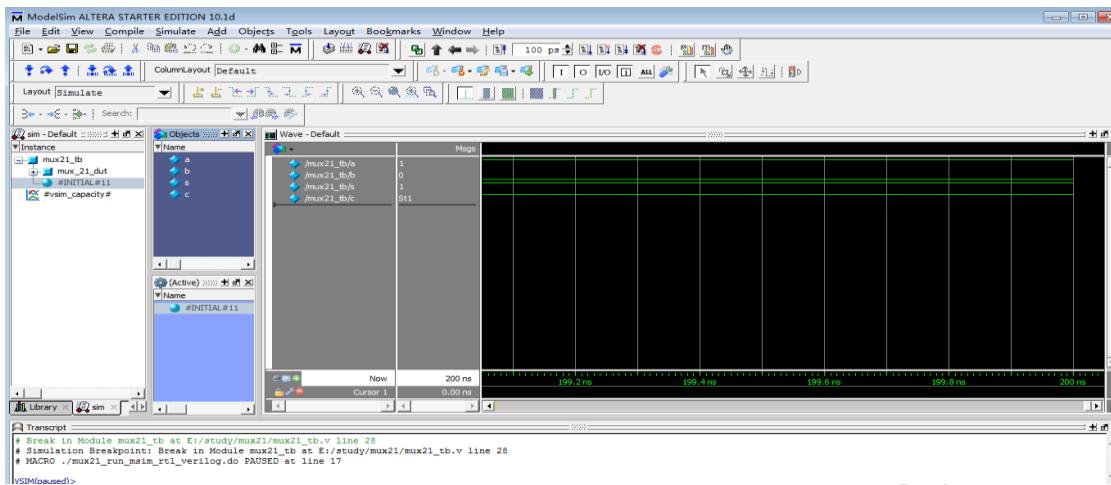

界面如下：

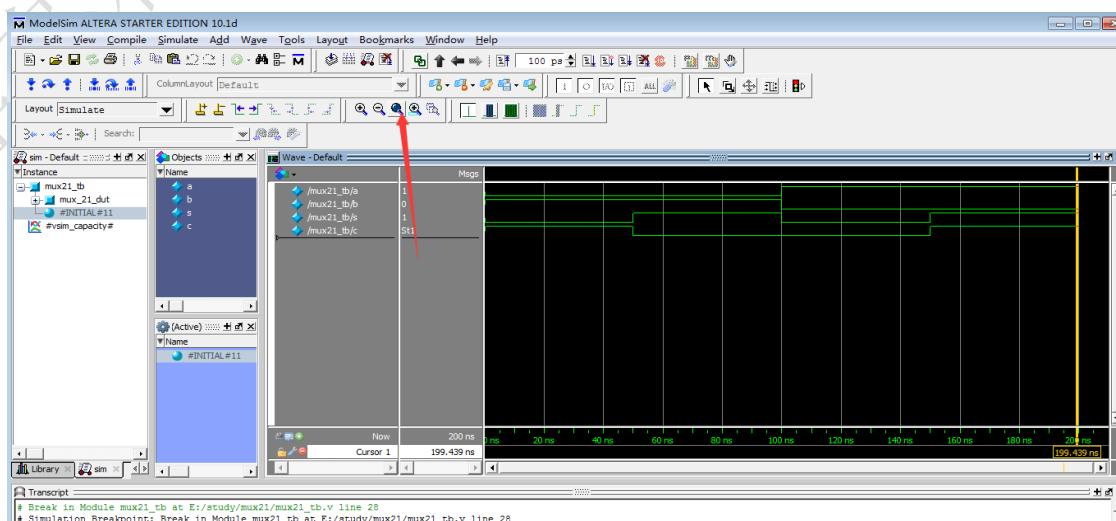

下面我们开始分析仿真波形：

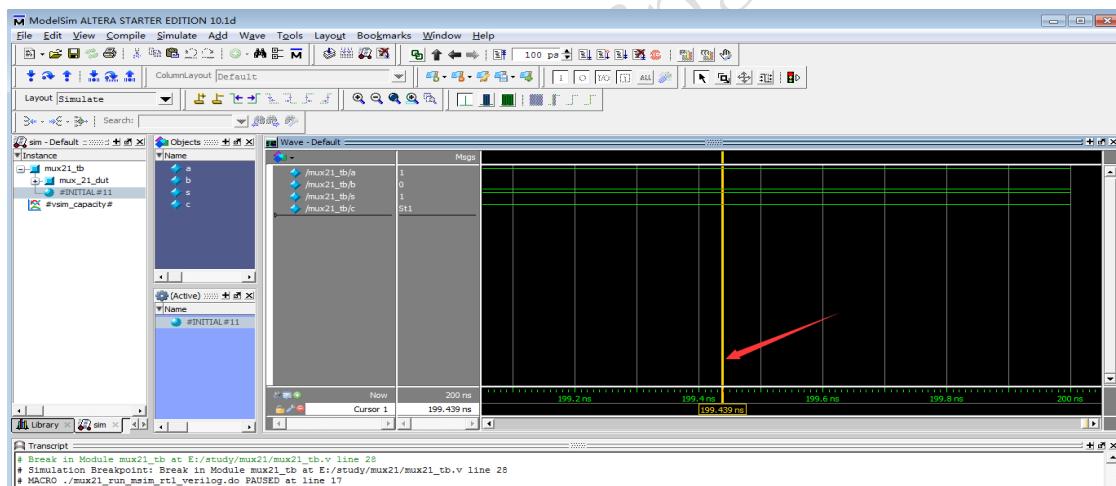

1. 在波形界面点击一下。

2. 点击全局缩放。

### 3. 分析波形。

当“s”为高电平时，“c”等于“a”；当“s”为低电平时，“c”等于“b”；证明我们的设计正确。

具体的 modelsim 的使用方法，请参考后续的章节。如果有不明白的小伙伴可以发邮件到我邮箱或者加群询问。

制作人：奋斗的小孩

fpga 交流群：282124839