# 奋斗的小孩之 altera 系列

## 第九篇 二选一多路选择器的设计

在数字电路中，二选一多路选择器具备组合逻辑电路的简单性和经典性的特征，我们的第一个设计就从“它”开始。

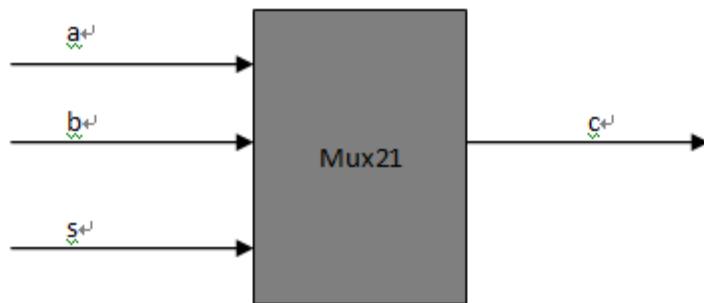

工程名称为“mux21”，架构图如下：

端口描述：

输入： a、 b、 s。

输出： c。

功能描述：

当“s”为高电平时，“c”等于“a”；当“s”为低电平时，“c”等于“b”；

Verilog 代码实现：

```

/*

模块名称: mux21

模块功能: 当“s”为高电平时，“c”等于“a”；当“s”为低电平时，“c”等于“b”；

```

编写时间: 2016-08-01

作者: 至芯科技----奋斗的小孩

邮箱: [zxopenhxs@126.com](mailto:zxopenhxs@126.com)

\*/

```

module mux21 (a, b, s, c);

input a;

input b;

input s;

output reg c;

always @ (*)

begin

if (s)

begin

c = a;

end

else

begin

c = b;

end

end

endmodule

```

这段代码很简单，相信小伙伴们自己能理解。如果有问题的话，

可以发邮件到我的邮箱或者在“fpga 交流群”里面询问，我会及时

回复大家。

制作人:奋斗的小孩

fpga 交流群:282124839