# 奋斗的小孩之 altera 系列

## 第七篇 新建 verilog 文件

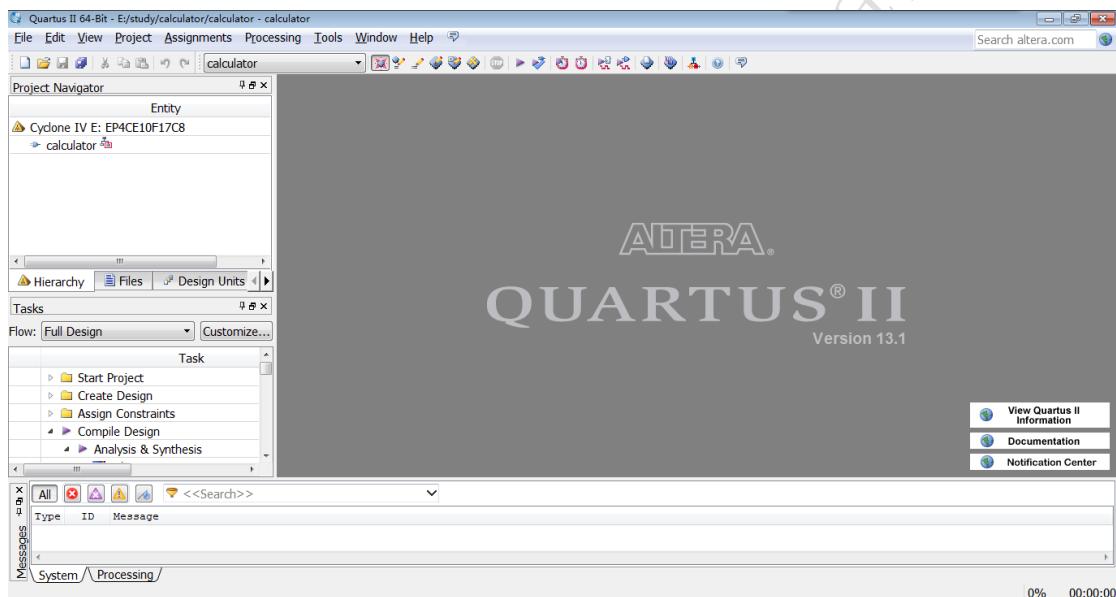

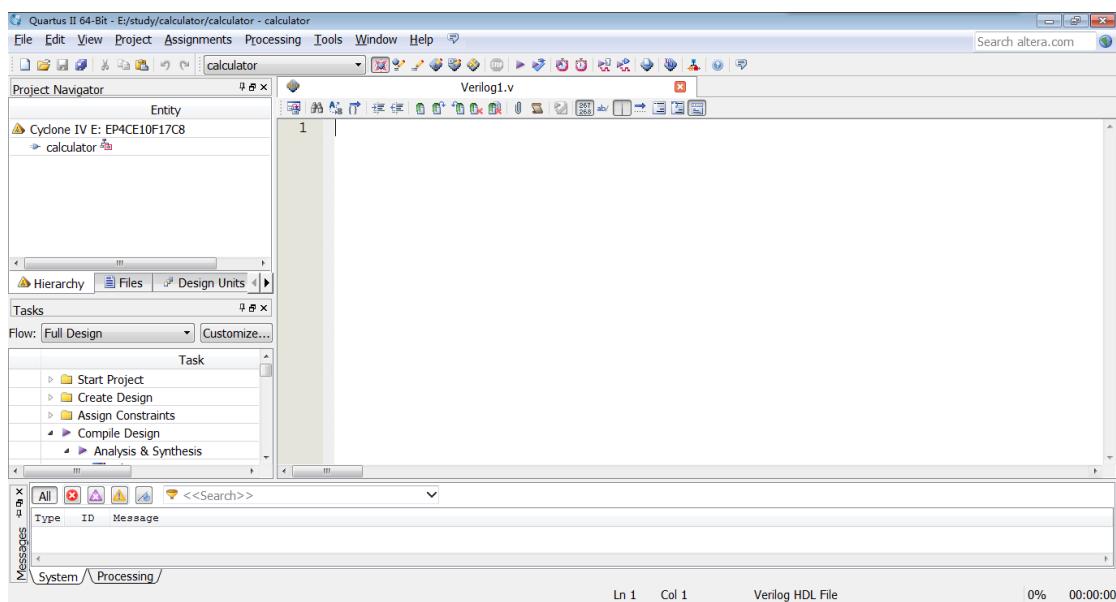

新建完工程或者打开之前建好的工程后，我们就可以去设计 fpga 电路了。可是，对于眼前的界面，我们好像找不到可以编写代码的区域。界面如下：

quartus ii 软件是 altera 公司的编译软件，支持所有的 altera 公司的芯片。同时，quartus ii 软件也是 fpga 的设计软件，所以也支持任何一种硬件描述语言 (HDL)，例如：AHDL、VDHL、Verilog HDL 等等。

在《奋斗的小孩之 altera 系列》中，笔者选择的硬件描述语言为：Verilog HDL，Verilog 的一些语法请参考《奋斗的小孩之 altera 系列 第八篇 Verilog 基础语法》。

Quartus II 软件支持很多的硬件描述语言，那么各种语言是不是用同一种文件呢？答案是否定的，下面我们来新建用来写 verilog 语言的文件。

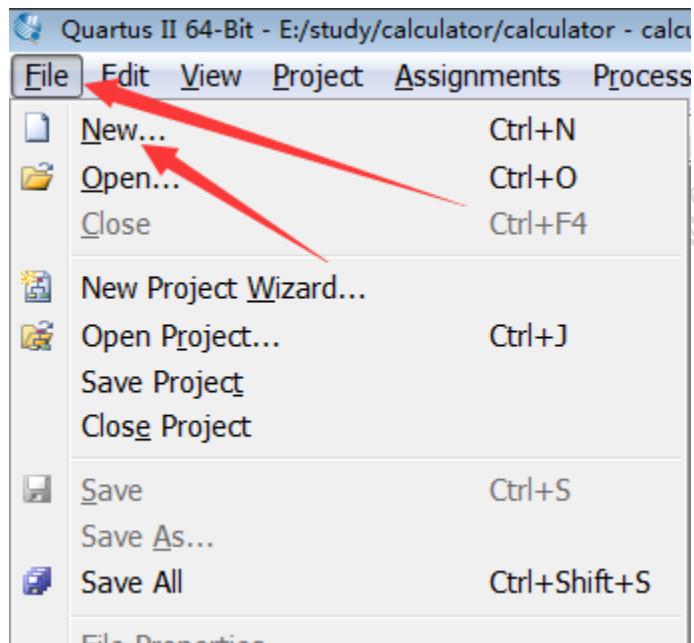

点击 file - new 打开新建界面。

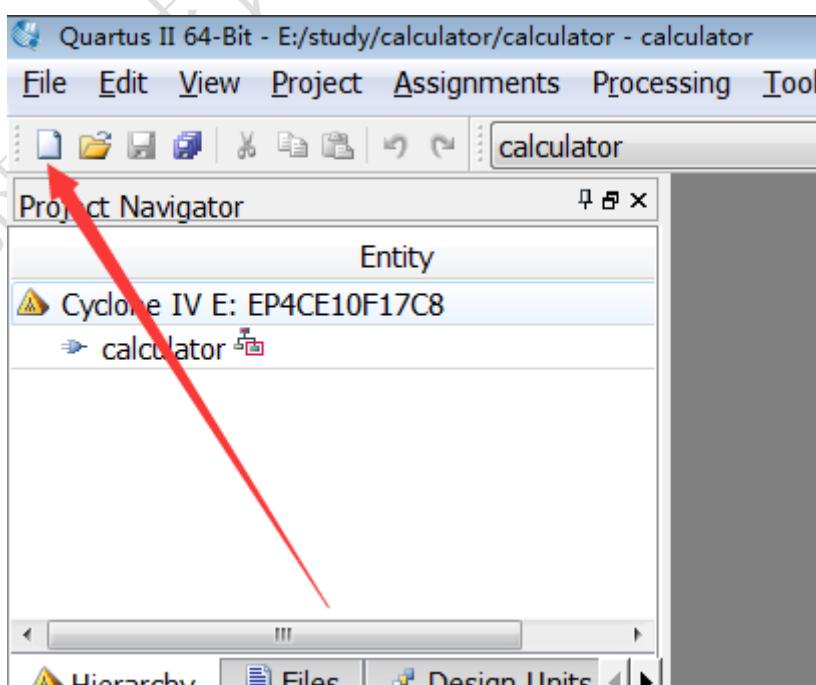

或者直接点击：

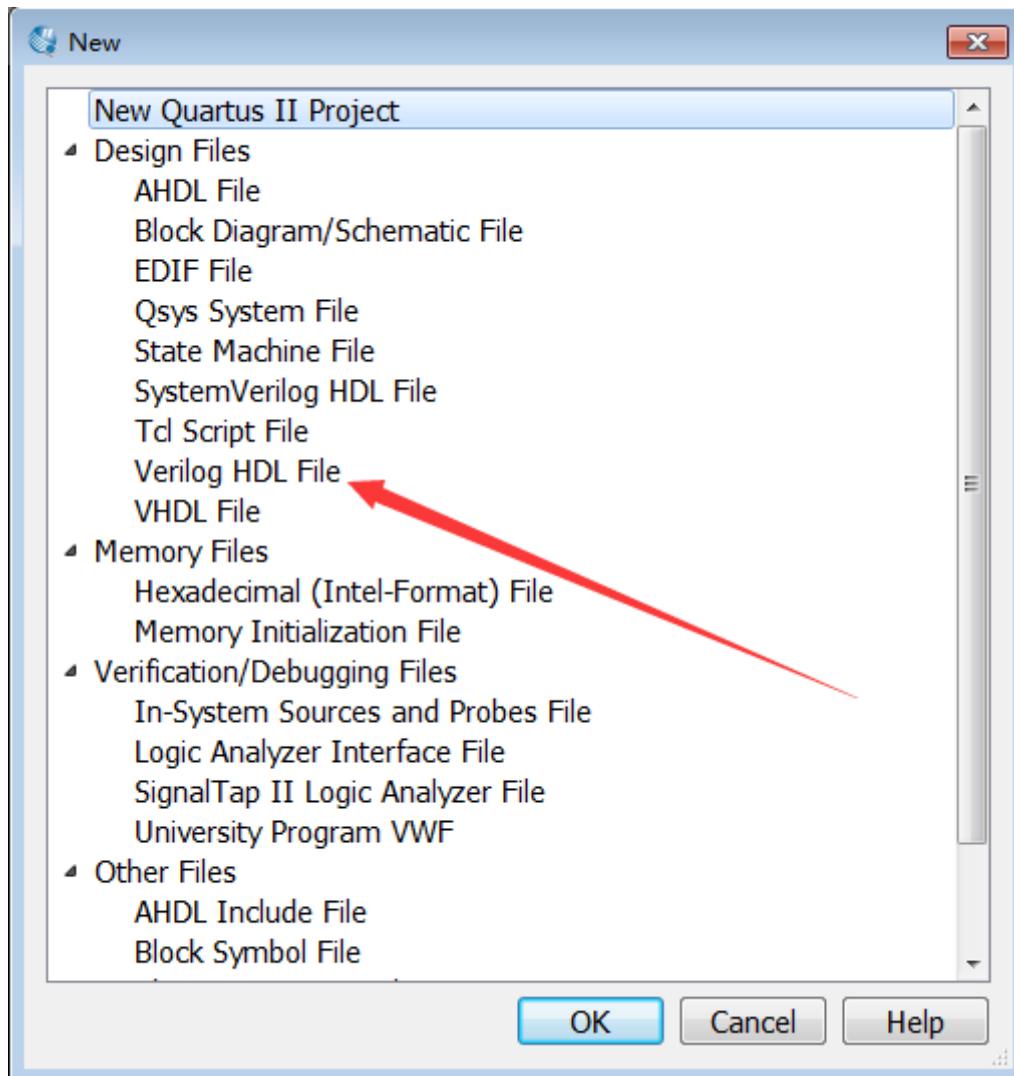

上述两种方法都可以直接打开新建界面如下：

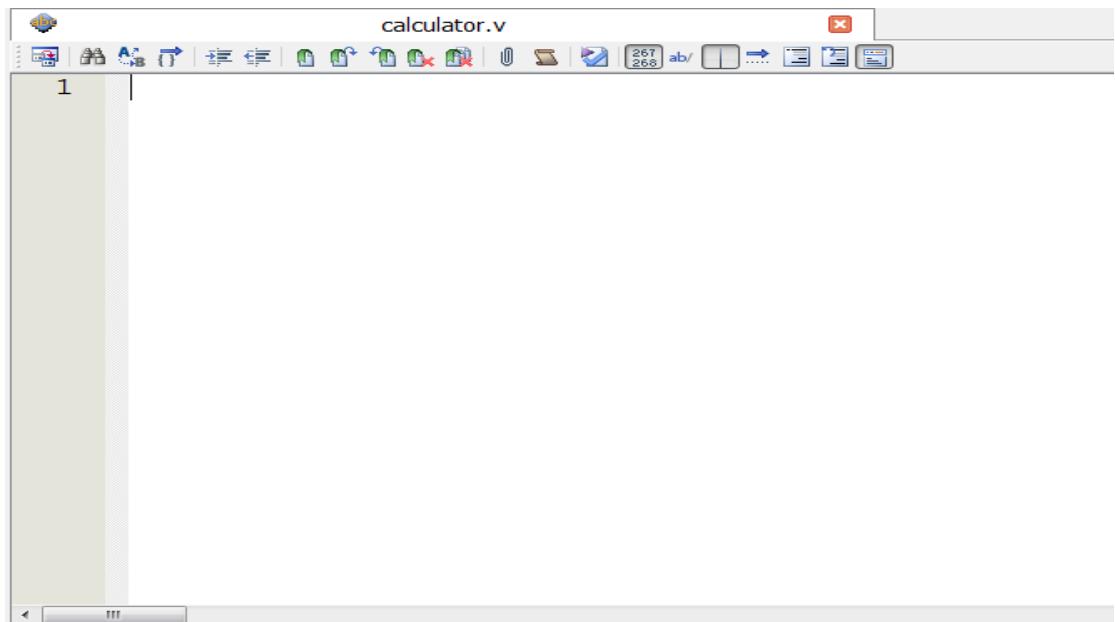

在这个界面里，我们了解到，quartus ii 可以新建很多类型的文件，例如：AHDL 文件、VHDL 文件、Verilog HDL 文件等等。我们选择 verilog HDL File，然后点击 OK。界面如下：

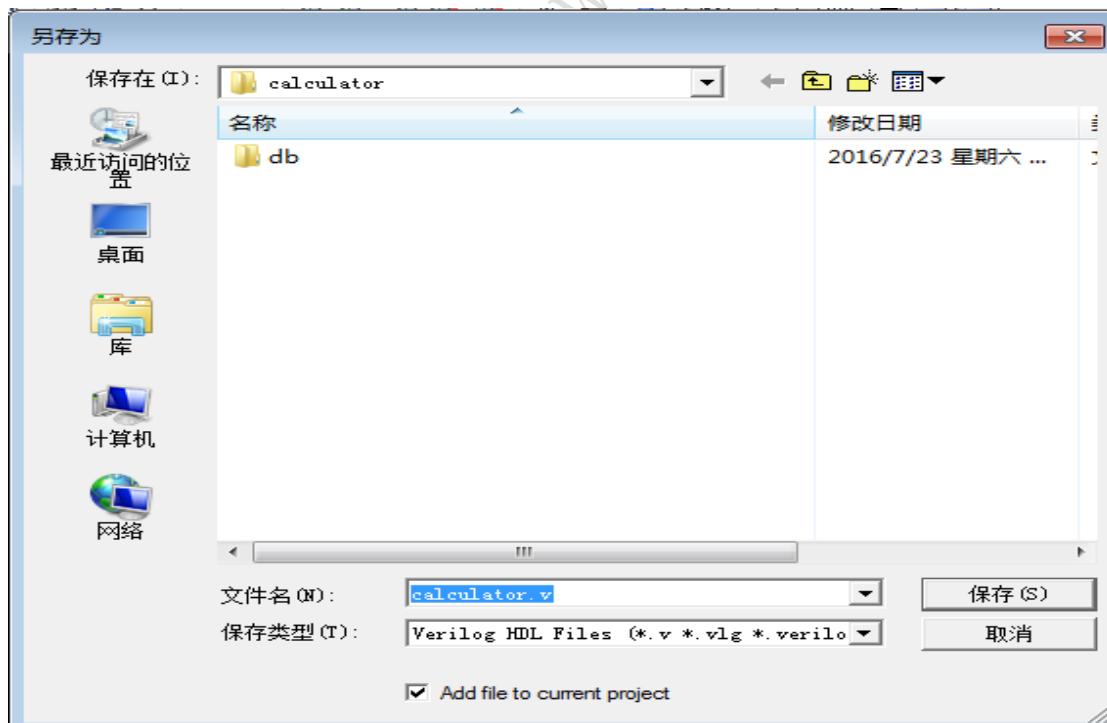

找到了编辑区，我们终于可以去编写代码了。但是，笔者不建议直接去编写代码，而是应该先去保存文件。点击 file--save as，界面如下：

笔者建议要把设计文件放到工程的文件夹下，否则容易找不到设计文件被放到那里（以后的篇幅，都是将设计文件放到了工程的文件

夹里)。

找到工程的文件夹，点击“保存”。界面如下：

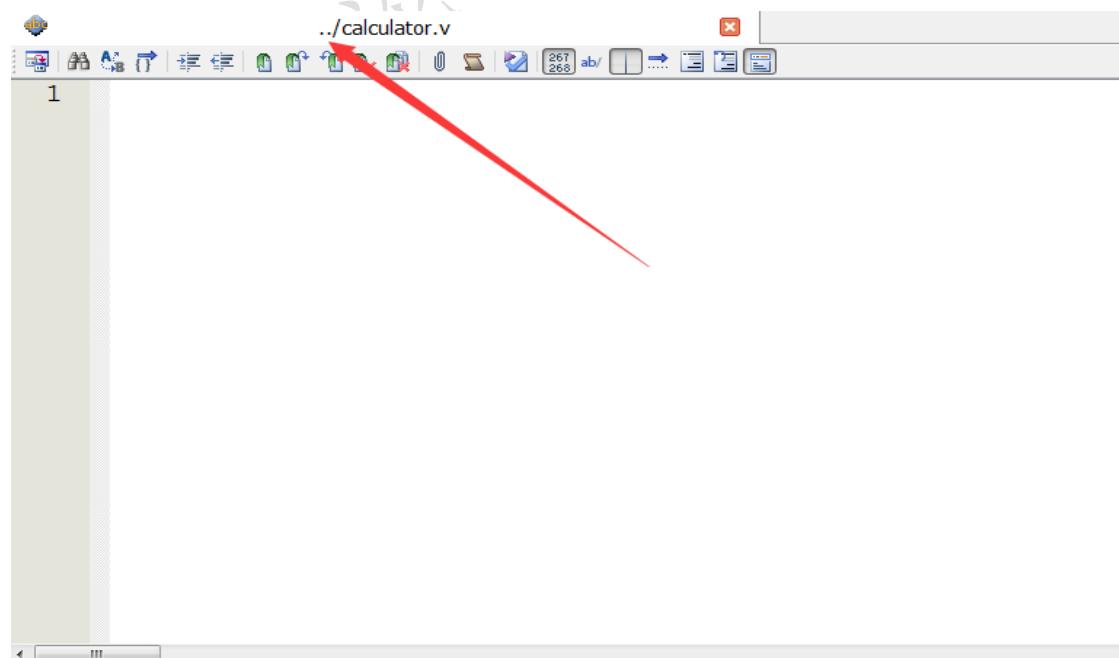

如果公司或者个人习惯不愿意将设计文件和工程放到一起，那么

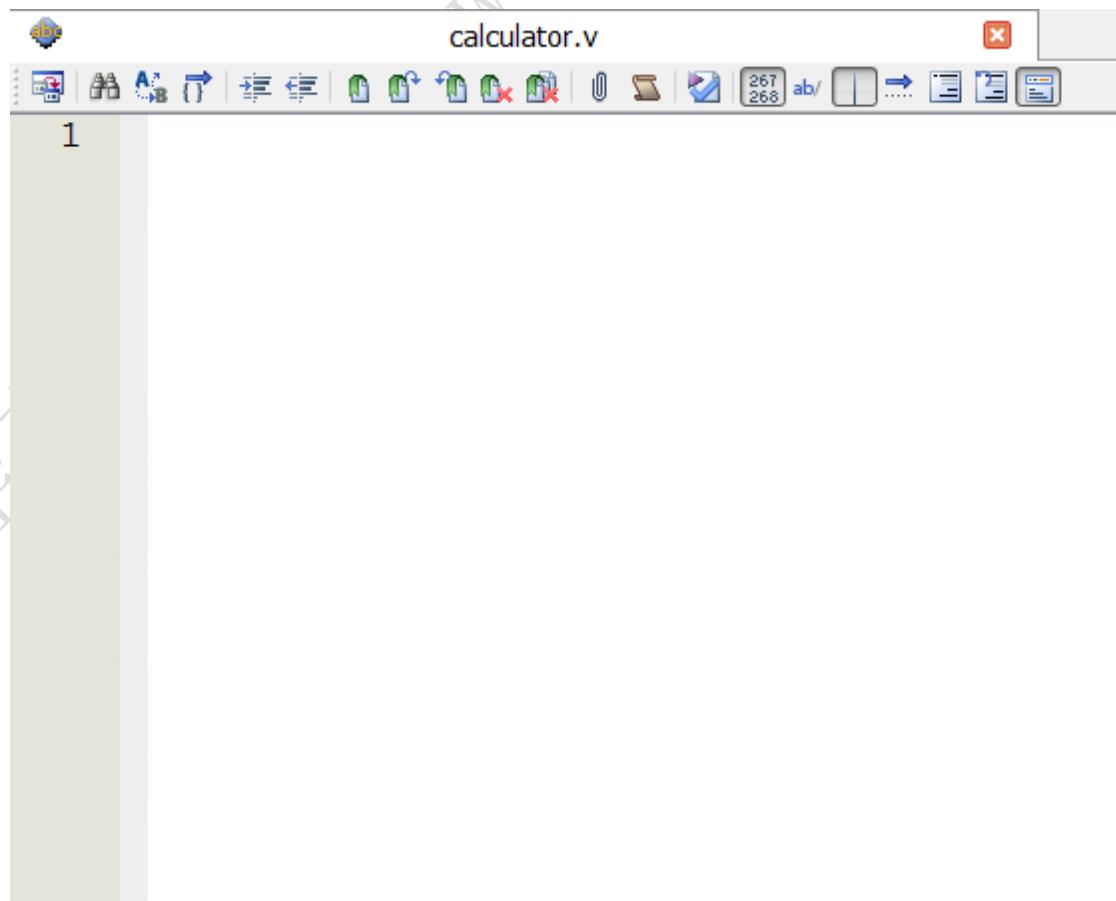

点击保存后，界面如下：

在文件名字的前面会有一定的路径。但是，这种做法不会影响后

续的任何操作，小伙伴可以放心使用。

**注：**如果有已经按照笔者的第一种方式保存了文件，然后又用第二种方式保存了文件，那么需要大家移除一个设计文件，否则将会在后续的操作中出错，步骤如下：

1. 关闭所有设计文件。

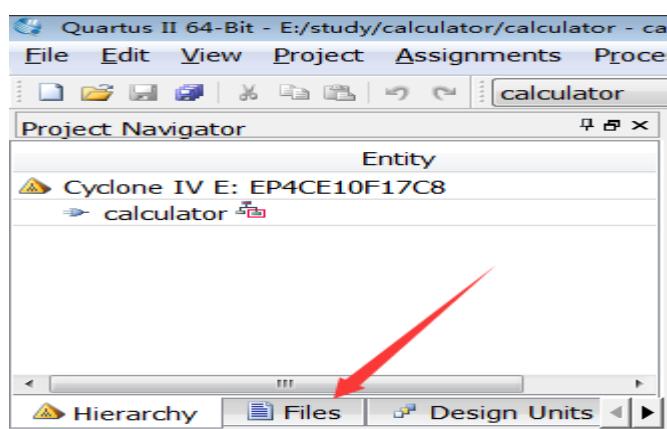

2. 点击 files。

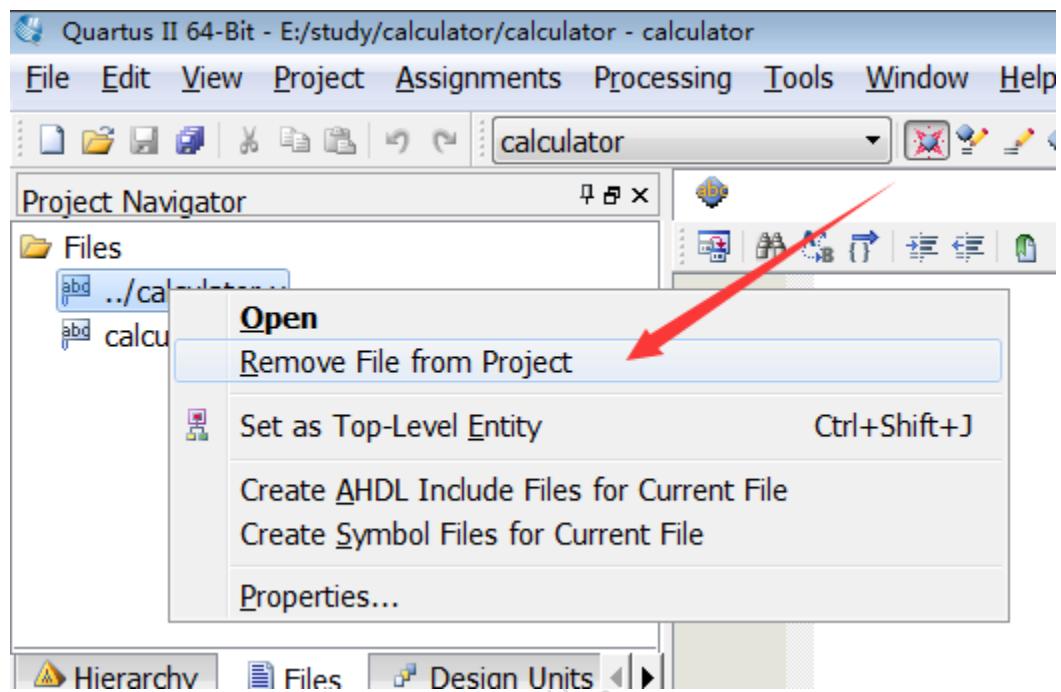

3. 选中想要移除的文件，左键移除。

4. 然后双击打开设计文件进行设计。

有了代码的编辑区，我们就可以按照自己的设计思路来设计硬件电路了。

制作人:奋斗的小孩

fpga 交流群:282124839