# PCB 经典设计资料(上)

Wang1jin 收集.

交流论坛: <http://bbs.cepark.com/>

推荐网站: [www.cepark.com](http://www.cepark.com)

本文汇集国外厂商的设计数据，分成（上）、（中）、（下）三集、六个单元，详细介绍电路基板导线 Layout 技巧，包括：微电脑周边电基板路导线设计、模拟电路基板导线设计、宽带与高频电路基板导线设计、电源与功率电路基板导线设计、数字电路基板导线设计，以及 Video 应用电路基板导线设计。本篇先将介绍计算机周边、模拟电路基板，及宽带与高频电路基板的导线设计技巧。

## 微电脑周边电基板路导线设计

### a. LED 电流导线的设计

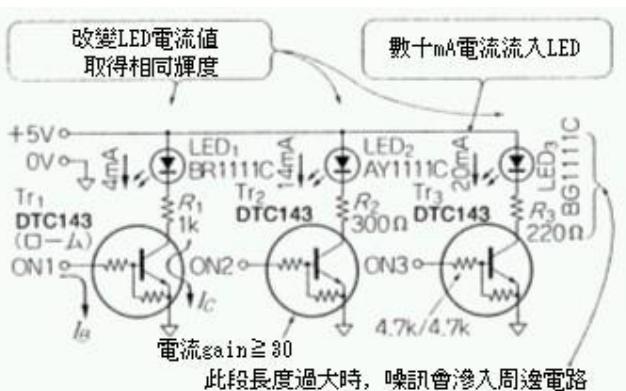

LED 组件广泛应用在微电脑接口设备，不过大部份的 LED 封装位置，距离计算机本身相当远。LED 只要维持适当亮度即可的同时，某些情况要求在明亮环境下能够轻易判别 LED 的辉度，然而即使相同的驱动电流 IF，LED 的辉度随着发光色出现差异(表 1)。如图 1 所示 LED 的电流高达数十 mA，随着 LED 电流导线长度与路径的延伸，LED 的 ON/OFF 经常成为周边电路发生切换噪讯(switching noise)的诱因。

| 型號      | 材質     | 發光輝度<br>(mcd) | 順電流 $I_F$<br>(mA) | 設計值<br>(mA) | 發光色 |

|---------|--------|---------------|-------------------|-------------|-----|

| BR1111C | GaAlAs | 11.7          | 20                | 4           | 紅色  |

| AY1111C | GaA,P  | 3.4           | 20                | 14          | 黃色  |

| BG1111C | GaP    | 2.4           | 20                | 20          | 綠色  |

表 1 LED 的发光色与辉度关系

图 1 典型 LED 驱动电路

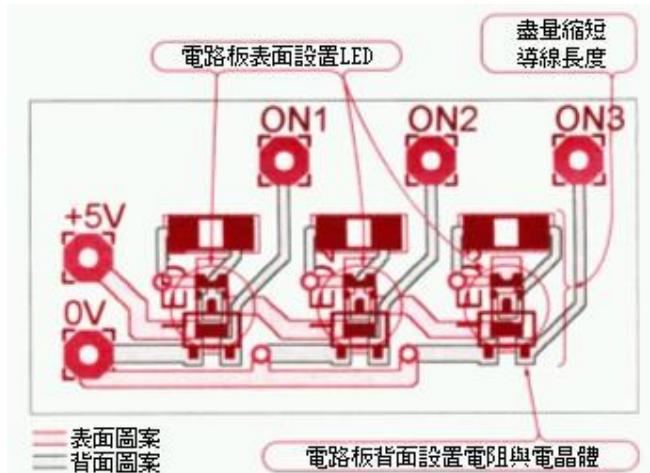

因此封装时驱动晶体管必需尽量靠近 LED，藉此缩减 LED 电流 IC 的流动路径。LED 的辉度与驱动电流呈比例，一般设计上是以绿色 LED 作基准，依照表 1 的设定值改变各色的电流值。LED 电路基板图案可依照图 2 的矩阵(matrix)方式排列，如此一来外观上显得非常简洁，驱动晶体管则当作数字晶体管(digital transistor)，串联电阻一般是设在电路基板背面。

图 2 典型 LED 驱动电路板的图案(双面电路板)

### b.7 时段 LED 的 common 端子设计

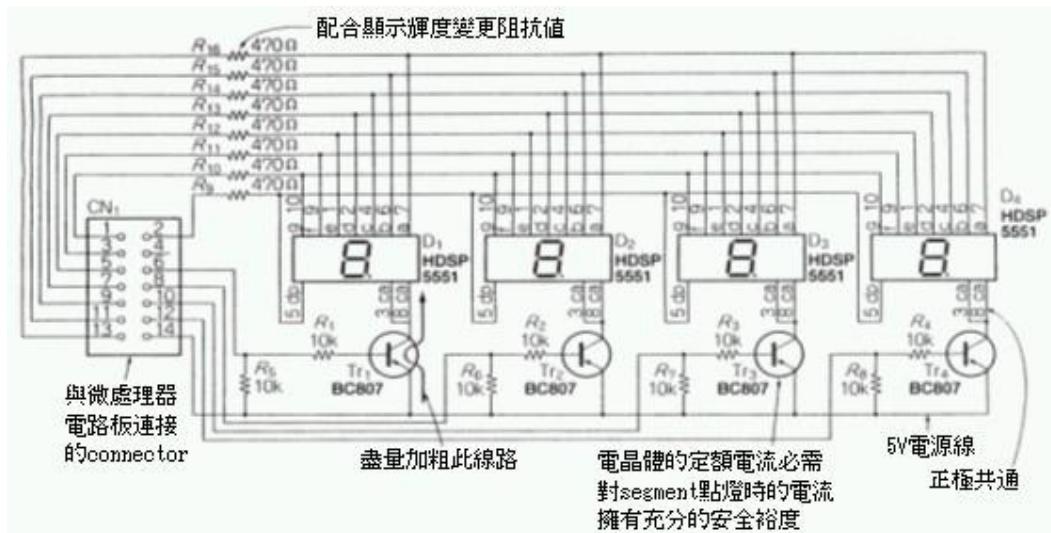

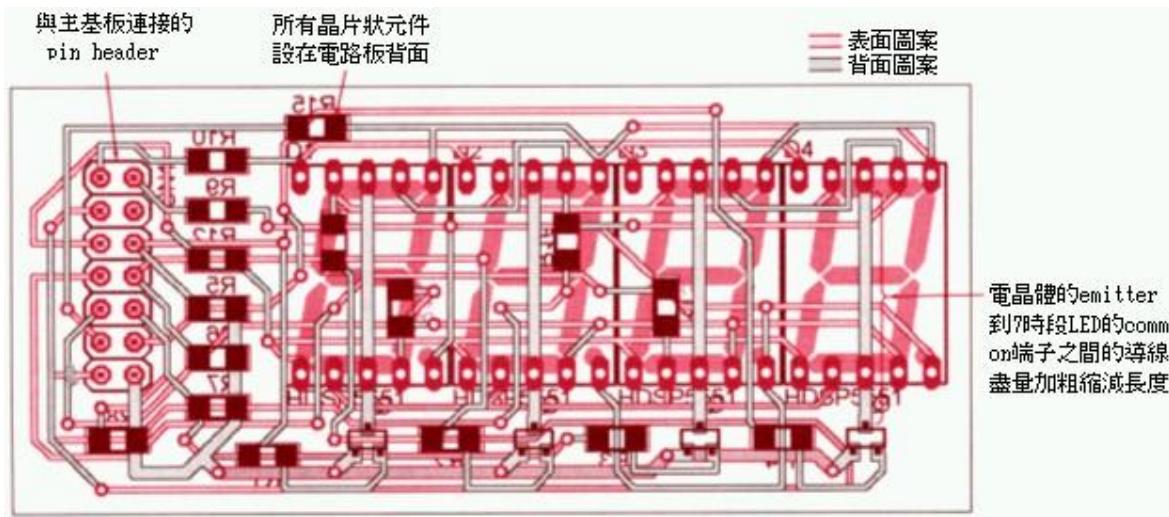

图 3 是利用微处理器控制的 open drain 端子动态驱动阳极(anode)common type 7 时段(segment)LED 电路图，从电源到 7 时段 LED common 端子的导线，基于全时段点灯时电流高达 40~100mA 的考虑，因此设计上尽量加粗电路基板的图案(pattern)导线宽度。使用双面电路基板与 disc lead 的场合，组件必需设在显示器的外侧，如此才能避免影响 7 时段 LED 的封装作业。芯片(chip)组件若设在基板背面时，如图 4 所示可以消除显示器周围的组件，如果加上连接器(connector)cn1，封装后的 LED 模块可以直接固定在微电脑内。

图 4 是利用电路板图案设计 CAD EAGLE 软件自动布线，该软件具备全自动自动 Layout 功能，而且可以不限次数变更设计，此外自动 routing 可透过试算错误寻求各种路径(route)，不过笔者建议初期设定时，基板背面的布线采直交方式，事后比较容易修改，尤其是类似这种电路，若未特定布线方向成功机率非常低。

图 3 7 时段 LED 的动态驱动电路图

图 4 chip 组件构成的 7 时段 LED 电路板图案(双面电路板)

c. 高湿度环境用的基板布线

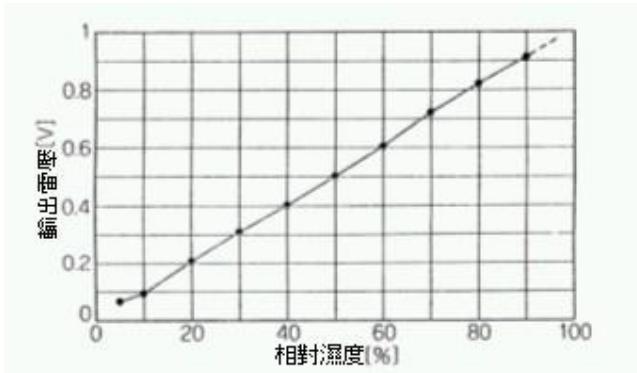

照片 1 是内建周边电路的湿度传感器 CHS-GSS 实际外观，如图 5 所示相对湿度 100%时 CHS-GSS 湿度传感器只有 1V，所以可以当作数字电压计直接读取湿度。如果与微处理器的 A-D converter 连接时，必需转换成 5v 等级(range)。

照片 1 湿度传感器 CHS-GSS 外观

图 5 湿度传感器的相对-输出电压特性

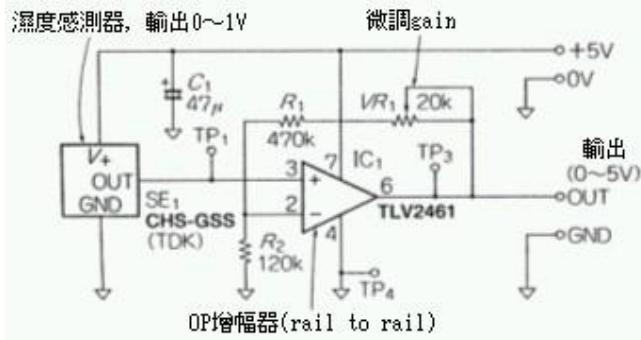

图 6 的电路使用单电源，它是由 rail to rail OP 增幅器构成，可以将湿度传感器的 1V 转换成 5V，此外利用图中的 gain 微调器 VR1，可以使 gain 成为  $(1+480/120)=5$ 。

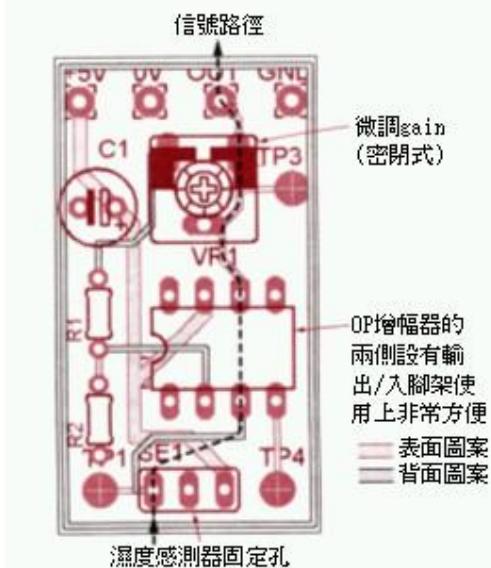

布线设计上为了降低高湿度环境时的漏电(leak)现象，必需避免在 OP 增幅器接地(ground)之间设置图案，同时尽量加大图案之间的间隔缩减图案导线的宽度。图中 R1, R2 使用 1/4W

±1%金属薄膜电阻；图 7 是 auto router 绘制的双面电路基板图案，焊接面为全接地(full ground)，本电路基板封装测试后用树脂包覆防湿。

图 6 扩大湿度传感器输出范围的电路

图 7 湿度传感器周边电路的 pattern

(双面电路板, 未标示背面接地)

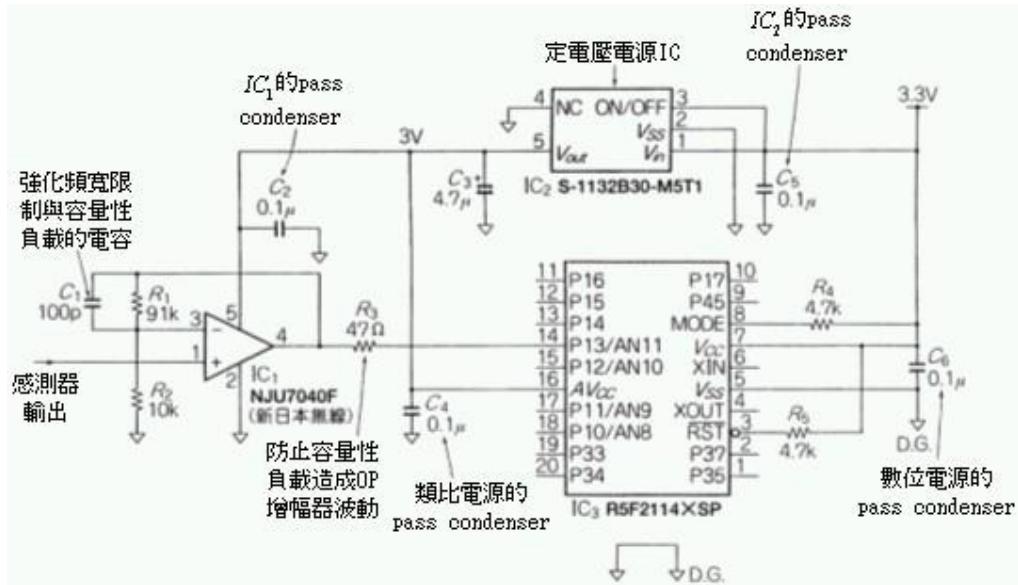

d. 微处理器内建 A-D converter 时, 前置增幅器周边的模拟/数字分离技巧

最近几年单片微机大多内嵌 A-D Converter(以下简称为 ADC), 封装这类微处理器时, 必需防止模拟 ADC 受到数字电路噪讯的影响。图 8 是小型单片微机与 ADC 用置增幅器(pre-amplifier)的电路图, 图中的 IC1 为输出入 rail to rail 的 OP 增幅器, 它是 ADC 前置增幅器的 10 倍电压 gain 非反相增幅电路; IC2 是 dropout 定电压电源, 它可以产生 3.3V 数字与模拟电路的电源; IC2 使用 Renasas 公司开发的 R8C/Tiny 系列小型微处理器, 该芯片内建 10 位循序比较型 ADC, 第 14 号脚架(pin)除了可以输入模拟信号之外, 同时也是 ADC 用模拟输入埠(port)。接着介绍 除外的表面封装组件, 封装在双面印刷电路基板的技巧。

图 8 内嵌 A-D converter 的微处理器与前置增幅周边电路

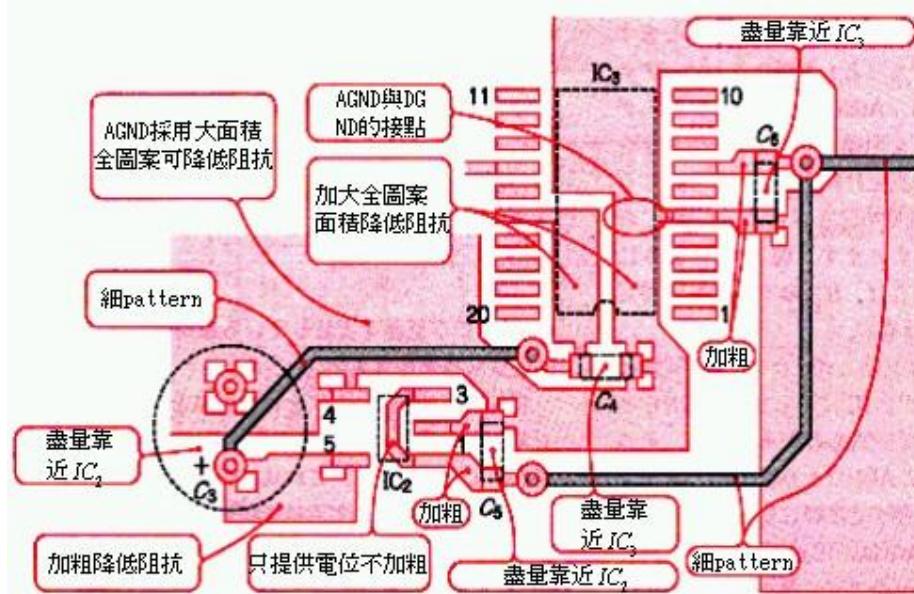

图 9 是接地与电源电路的基板图案。接地图案设计上的重点，必需明确分离模拟接地(以下简称 AGND)与数字接地(以下简称 DGND)，此处为配合电位因此采取单接点设计，如此设计可以防止数字电路的噪讯，造成 ADC 的转换精度降低等问题，因此图 9 的 AGND 与 DGND 连接点设在 IC3 的 Vss 端子(5号脚架)附近。

图 9 IC3 周边电路的 pattern 说明

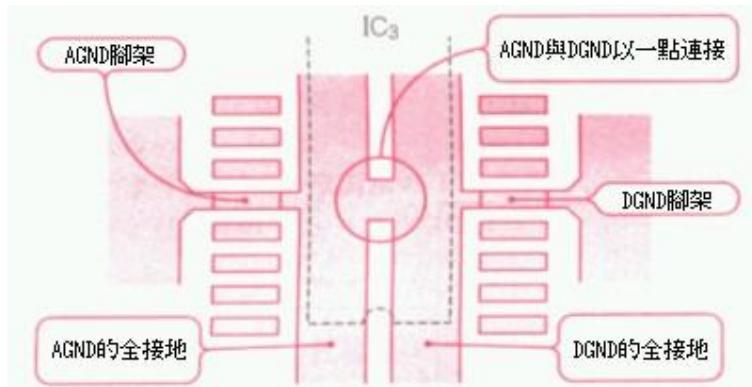

本电路使用的微处理器接地端 Vss 只有一条，不过其它型号的 IC 则将 AGND 与 DGND 端子分离，因此必需将 AGND 与 DGND 的 pattern 作明确的分离与单点连接(图 11)。电源电路需注意的是与 IC2 输出入连接的 C3, C5 两电容的设置，因为未降低输出入端子的高频阻抗时，低 dropout 电压的电源 IC 会有波动之虞，所以 C3, C5 尽量靠近 IC2 设置，同时还需要缩减导线长度加粗导线宽度。

图 10 AGND 与 DGND 明确分离作单点连接

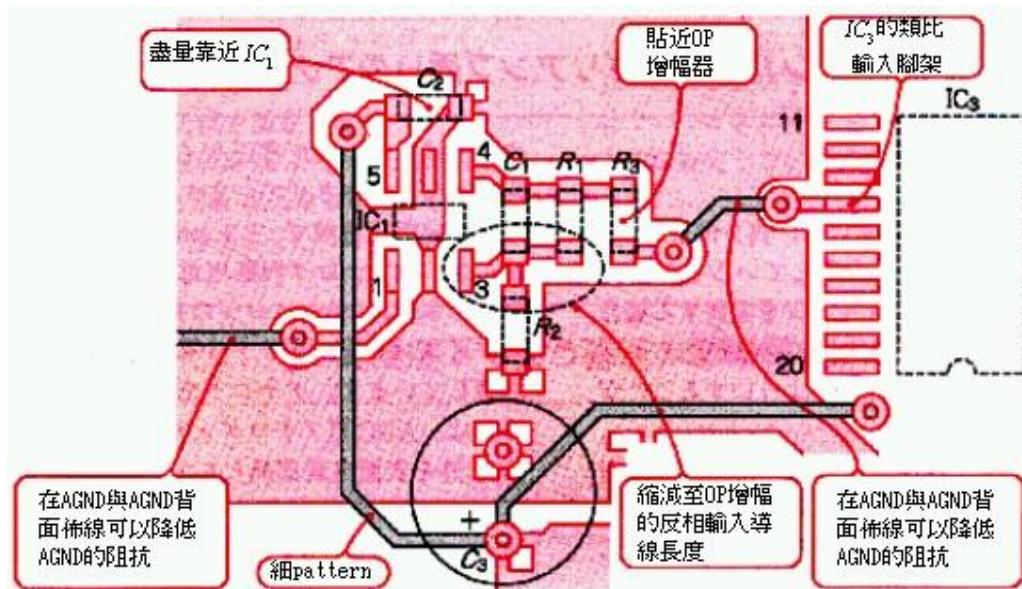

图 11 是前置增幅周边电路的电路基板 pattern, 如图所示 C2 设置在 IC1 附近, 由于电压复归型 OP 增幅器反相输入端子的输入阻抗很高, 极易受到外部噪讯的影响, 所以图 11 的电路基板图案, 刻意缩短至反相输入端子(IC1 的 3 号脚架)的导线长度, 图中 R3 是分割容量性负载与 OP 增幅器输出端子的电阻, OP 增幅器与微处理器之间的导线很长时, 该电阻必需尽量设置在 OP 增幅器附近。

图 11 前置增幅器周边电路的 pattern

描绘 AGND 时必需尽量降低 AGND 本身阻抗, 实际布线图除了采用 full pattern 之外, 前置增幅器的输出导线应用贯穿孔(through hole)设计, 使导线绕到 AGND 背面藉此降低 AGND 的阻抗。此外包含前置增幅器在内封装模拟电路的基板背面, 不可有任何数字信号(包含 DGND)流通, 主要目的是要防止容量结合, 造成数字电路的信号变成噪讯影响模拟电路的动作。

#### 模拟电路基板导线设计

##### a. OP 增幅器构成的全波形整流电路 patterning

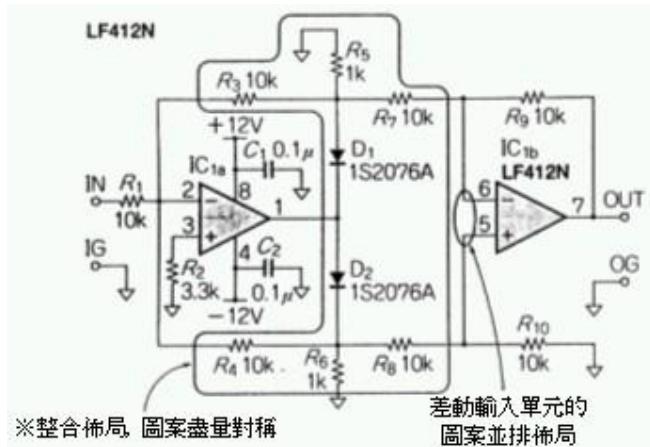

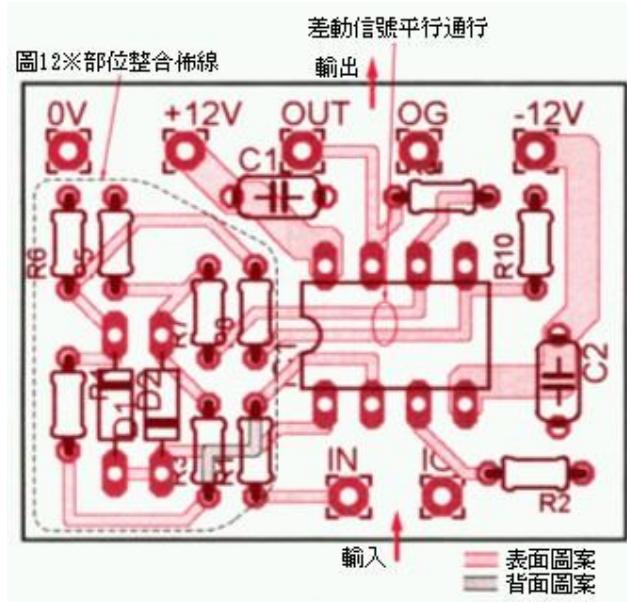

图 12 的全波形整流电路, 经常因正端(plus side)与负端(minus)gain 的未整合, 导致波形不均衡, 所以决定 gain 值的电阻使用误差为±1% 的金属皮膜电阻。本电路可以使 IC1b 作差动动作, 因此能够减缓高频时波形不均衡现象。虽然 OP 增幅器采用 LF412, 不过可以根据设计需求, 改用与 OP 增幅器脚架相容的 LM358

图 12 利用 OP 差动增幅器作全波整流的电路

IC1 的 1、2 号脚架至 5、6 号脚架路径(route)是本电路基板主要设计重点，如图 13 所示如果导线绕过 IC 的外侧，路径会变长所以采取 IC 下方布线设计，正、负电源的图案导线宽度完全相同，信号则沿着箭头方向流动，二极管(diode)等整流电路则整合在基板左侧，电源导线加粗的同时接地采取 full ground 设计，如此一来双面电路基板就可以满足以上所有的要求。

图 13 利用 OP 差动增幅器作全波整流的电路基板图案

#### b. 光学耦合器的基本周边导线

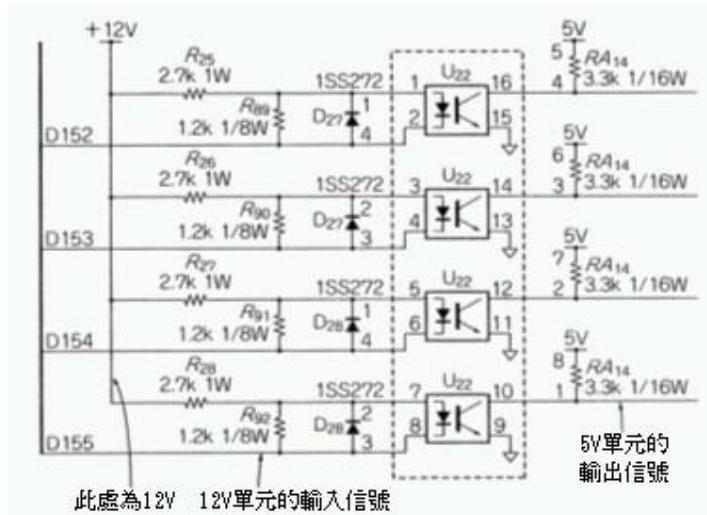

接着介绍封装光学耦合器(photo coupler)的电路基板分离图案设计技巧。光学耦合器主要功能是将 board 或是设备之间绝缘，主要原因是为了保障各组件保证的绝缘耐压特性，因此电路基板出现所谓的分离图案设计。图 14 的电路 12V 的输入单元与 5V 的输出单元就是采用分离图案设计，它使用四个编号为的 PS2801-4 光学耦合器。

图 14 使用 photo coupler 的电压转换电路

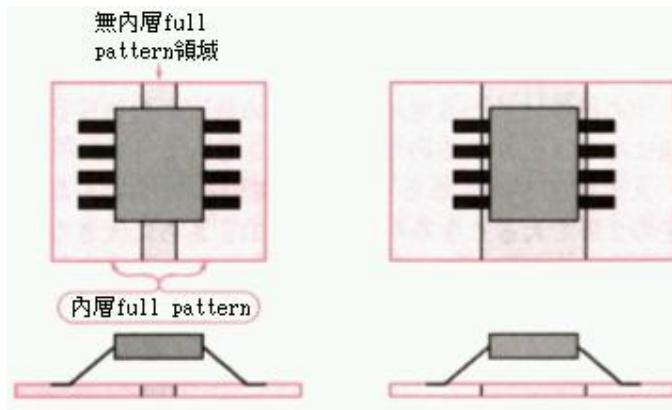

如图 15 所示为确保 1 次端(发光侧)与 2 次端(收光侧)的沿面距离，所以设计上分成表层图案与内层图案，内层图案若是 full pattern 时，与一般 full pattern 一样需作除料设计。所谓沿面距离是线导体之间的指导，沿着绝缘物通行时最短距离而言，有关耐压与沿面距离，UL、VDE 等各国的安全规范都有严谨的规定与说明。

(a)pattern 的间隔过窄设计例

(b)pattern 的间隔适当设计例

图 15 photo coupler 正下方的 1 次端与 2 次端图案必需确实分离

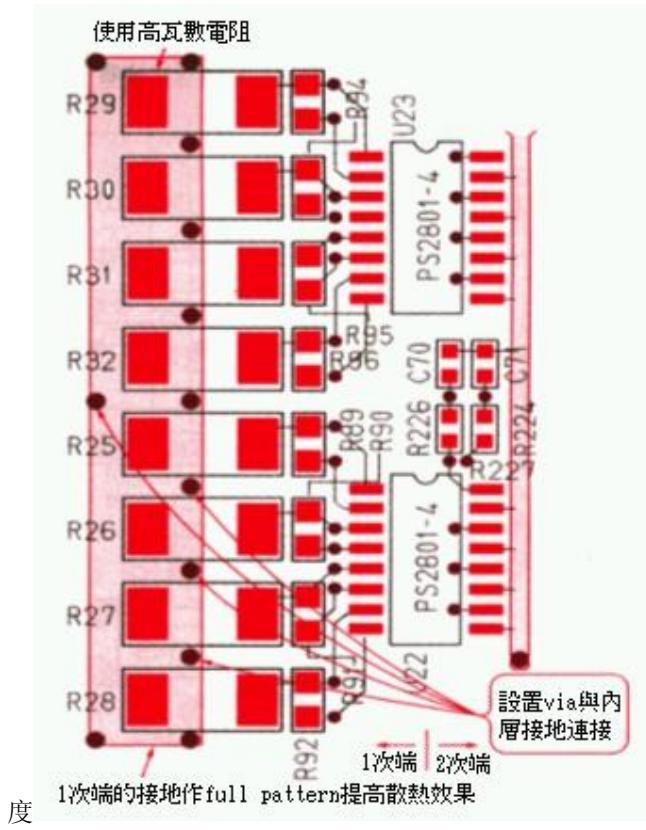

I/O 点数很多而且使用复数个光学耦合器的场合，必需将散热问题一并列入考虑。图 16 是根据以上需求，兼具散热效果的 pattern 设计范例，由图可知 1 次端与 2 次端的接地共通时，利用 full pattern 连接可以提高散热效果；内层有接地时可以在 full pattern 设置数个 via 与内层接地连接。

如上所述根据 1 次端与 2 次端的电流值与散热要求，最后才能决定电阻的定额与 pattern 宽

图 16 兼具散热效果的 pattern 设计

### c. 100V 以上商用电源线的图案

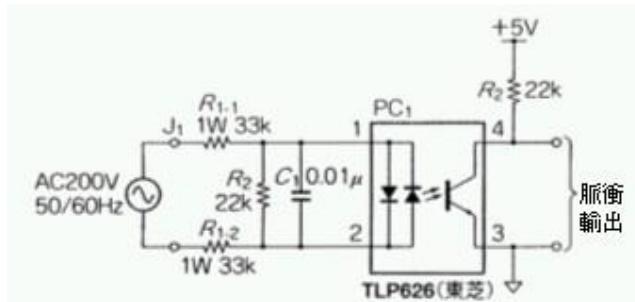

图 17 是已经绝缘可输出脉冲的商用交流 zero cross point 电路。TLP626 LED 两者未点灯时，光学耦合器的光学晶体管(photo transistor)成为 OFF，输出正极性的脉冲。

图 17 商用交流 zero cross point 检测电路

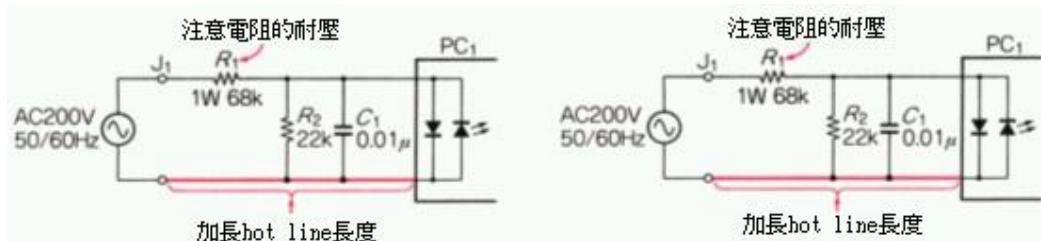

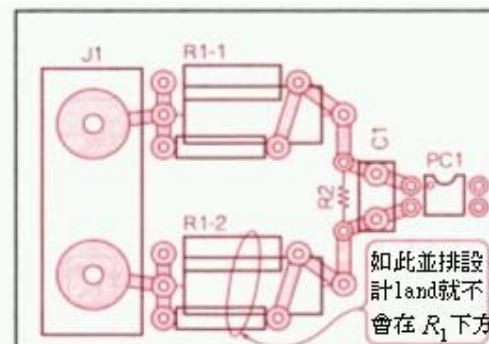

由于商用交流的输入线相当危险，因此设计电路基板图案时必需充分考虑绝缘与安全性。图 18 所示虽然 R1 单独一个电阻电气上动作完全相同，不过与商用交流的输入直接连接的图案变长，或是流入电阻的电压变高时，电阻的耐电压特性会出现问题，因此建议读者最好分成数个电阻。

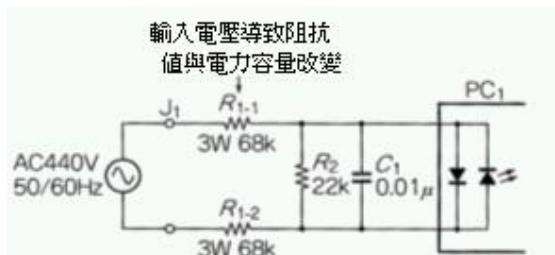

图 19 的输入电压变高时，R1 电力损失会以电压的二次方增加，此时必需改佣可以封装更大阻抗的电路基板图案。

图 18 以 R1 取代图 17 的 R1-1 R1-2

图 18 以 R1 取代图 17 的 R1-1 R1-2

图 19 加大图 17 的 R1-1 R1-2 容许电力可支持大电压范围

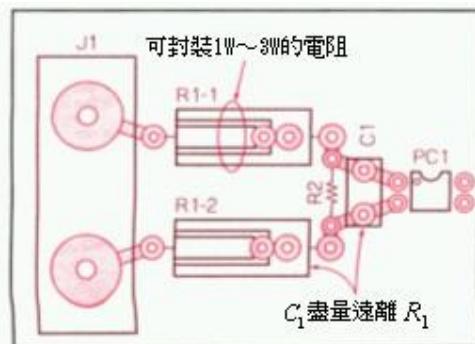

设计图 20 的电路基板图案，必需考虑下列事项：

- ①采用 full pattern 设计，组件尽量紧凑封装。

- ②R1 等发热组件附近设置低高度 R1，同时尽量远离 C1。

- ③R1 设置复数个可以封装 1W, 2W, 3W 电力阻抗的 land。

图 20 电路基板图案最大缺点是封装 2W, 3W 电阻时，会因为实际电阻封装情况，造成未使用的 land 太接近胴体部位；图 21 是设计变更后的电路基板图案，如此一来 R1 封装在任何位置，组件下方不会出现 land

图 20 商用交流 zero cross point 检测电路基板图案

.可发挥 24 位分辨率的 A-D converter 周边电路基板图案

图 21 设计变更后的基板图案

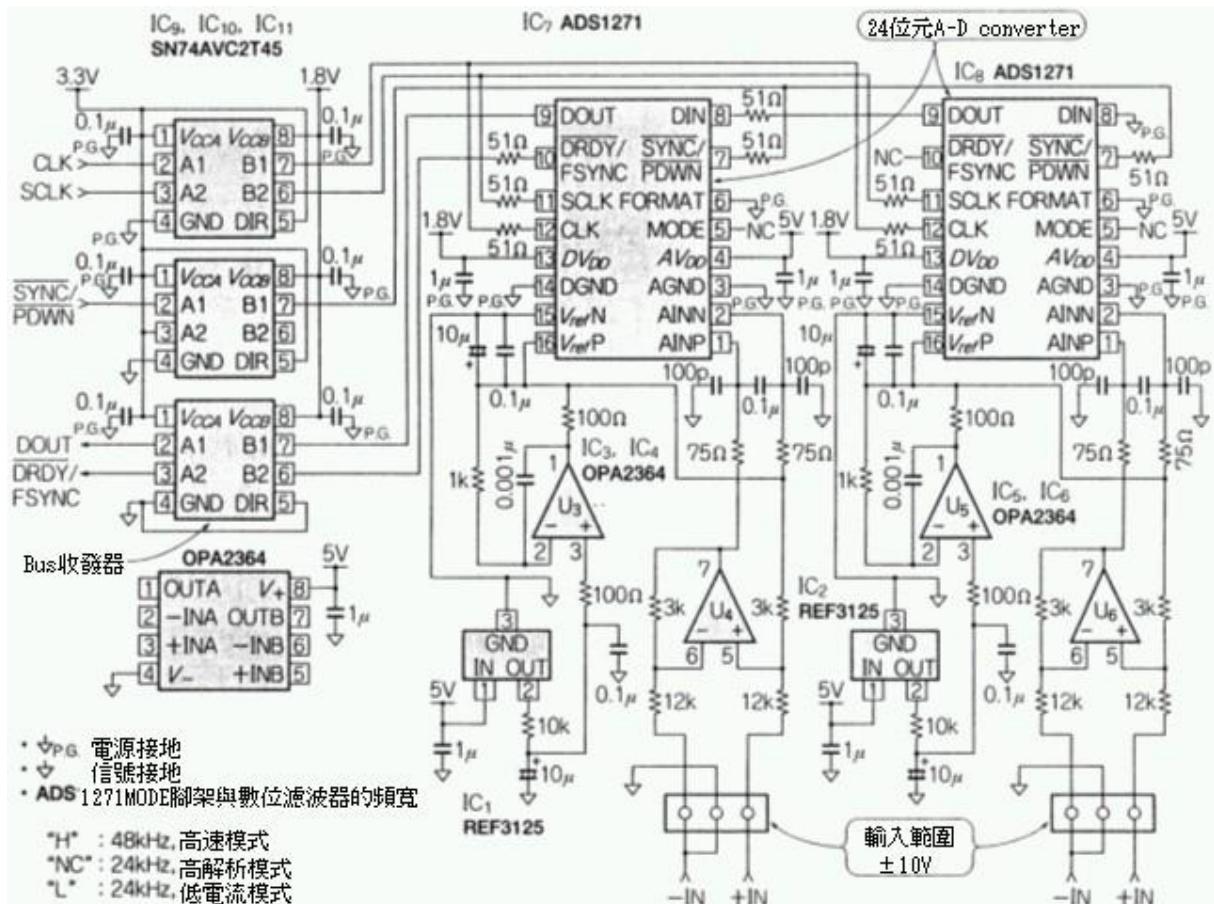

图 22 是由复数个 24 位 A-D converter 构成，具备电压测试精度与 SN 比最佳化，与直流甚至 20kHz 信号的多频道数据记录前置器(multi channel data recorder front end)电路图。本电路亦可应用在 3 频数据记录器，为达成目的因此将成为 ADC 的转换基准的参考(reference)电源 REF3125 IC(以下简称为 REF)当作 ADC 与 pair 使用，虽然如此设计 ADC 频道之间的 gain 误差会增大，不过复数 ADC 使用共通同的 REF，图案的设计自由度提高，而且容易获得理想的基板布线设计。

图 22 复数个 24 位 A-D converter 构成的多频数据记录器电路

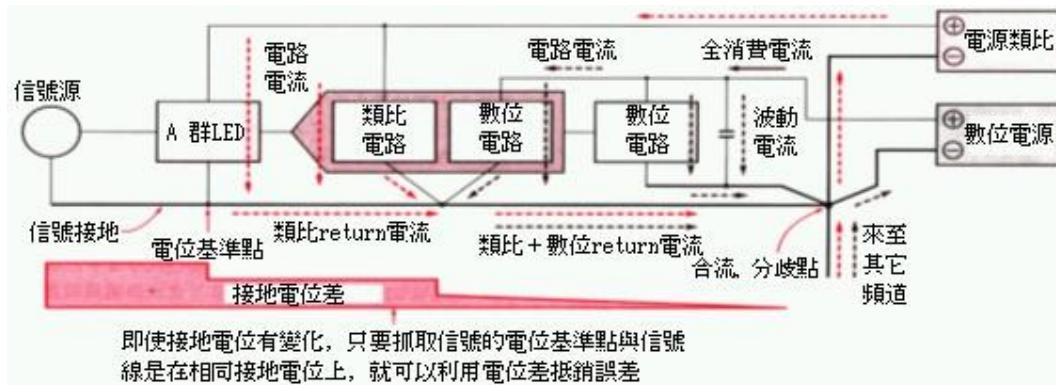

图 23 是从信号源一直到电源的过程中产生的接地电位差统计一览、上述电路为模拟/数字混载电路，因此接地会有模拟/数字电流流动，如果处理错误的话数字电路的 return 电流，会混入模拟接地变成噪讯源。

图 23 接地电流的种类与接地电位差的统计一览

此外各电路的电流是由电源的正极提供，再折返至供给元的负极，因此设计上利用此特性，设置 return 电流合流点与分歧，点使通行路径明确分隔。初段的模拟电路(前置增幅器)根据本身的电位基准点接受信号电压，信号源与该电位基准点若与接地的同电位时，正确信号电压会传递至前置增幅器。

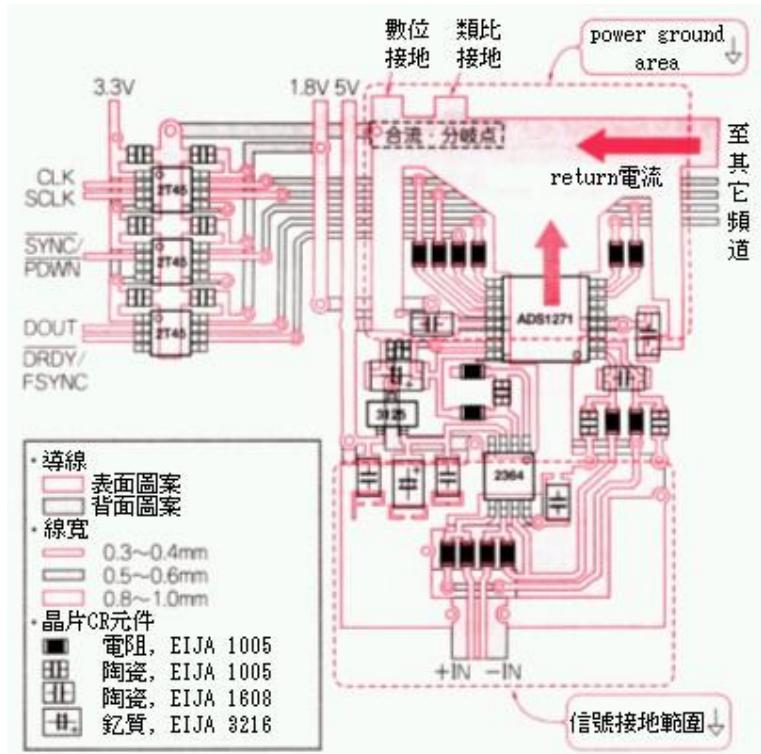

图 23 是表示电流的合流与分歧电位差。此外 ADC 包含模拟/数字两种电路两者的接地之间电位若有动态变化的话，模拟单元会出现耦合(coupling)造成 SN 比恶化现象，所以图 23 的 ADC 直接连接在与地电位上完全相同位置。图 24 是充分反映以上构想的数据记录器电路基板图案，如图所示宽幅的接地图案在 ADC 与 OP 增幅器正下方通行，它除了达成低接地阻抗化之外，还兼具对 IC 芯片的遮蔽(shield)效果，尤其是电路内层或是背面设有可以传输脉冲信号的图案时，通常都可以获得极佳低接地阻抗与遮蔽效果。

图 24 充分反映图 23 的构想的数据记录器电路基板图案

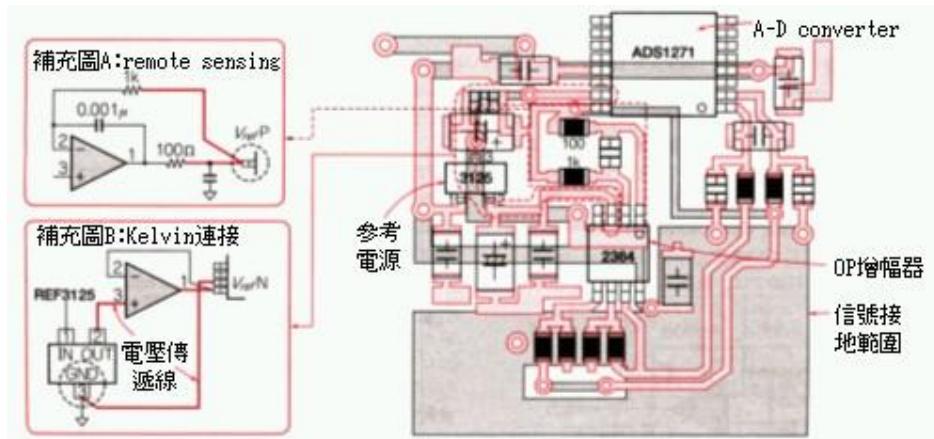

图 25 是基板背面图案，图中的补充图 A 又称为 remote sensing 手法。虽然 OP 增幅器的输出部设置利用电容负载防止波动的电阻，不过只要插入包含该电阻与 VrefP 电位的复归 loop，就能够正确将参考电压传至 VrefP。补充图 B 则称为 Kelvin 连接手法，由于 OPA2346 的第 2 与第 3 脚架之间会产生参考(reference)基准电压，因此直接在 VrefP 至 VrefN 之间铺设电压传输线，如此就可以防止 return 电流波动产生电压误差

图 25 可以提供 A-D converter 良好参考电压的电路基板