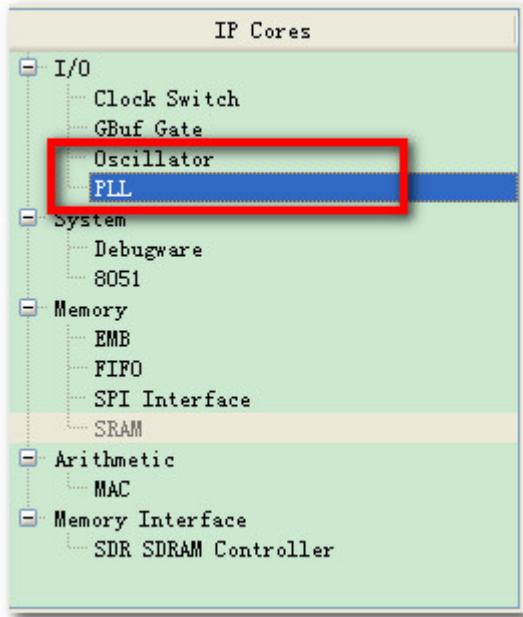

Primace4.1.2 提供一系列的 IP , 如图。

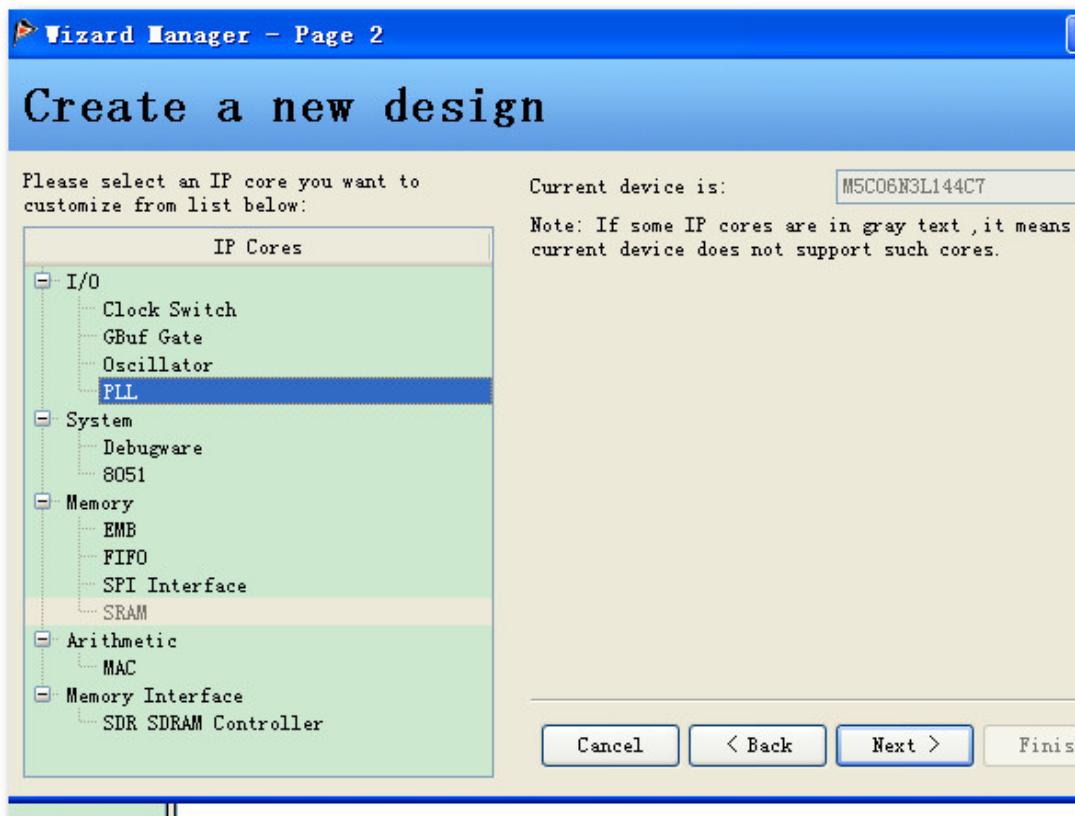

这里提供的是一个关于 PLL 使用的小例子。PLL 可以对输入的时钟脉冲信号进行调频调相的统一整合。时钟信号选择使用 IP Oscillator。

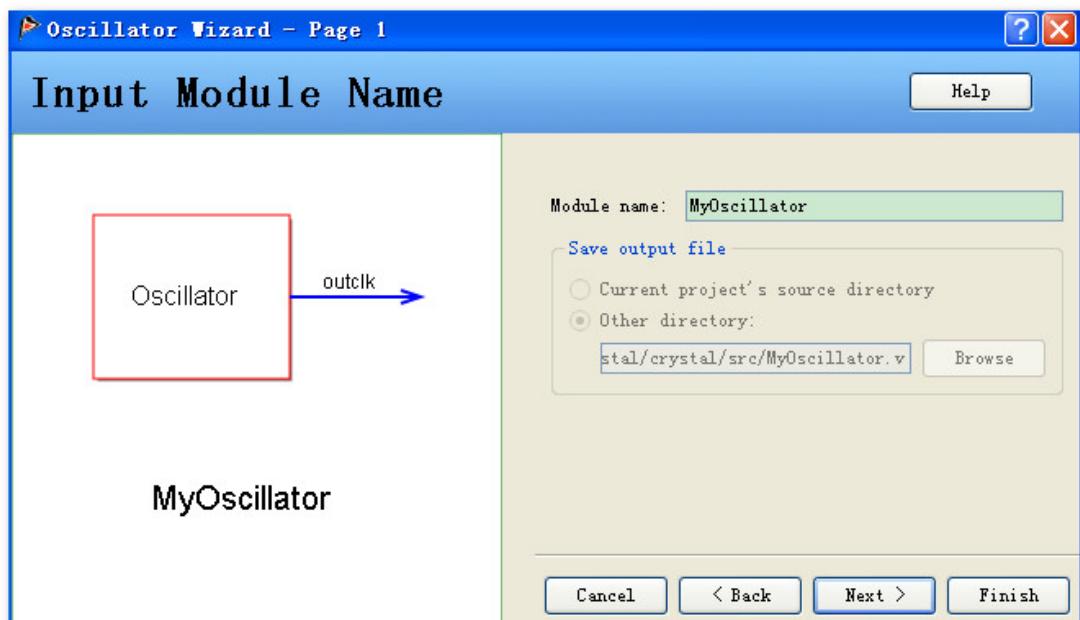

可以用 wizard 分别例化 Oscillator 和 PLL。点击图标

首先添加输入时钟。

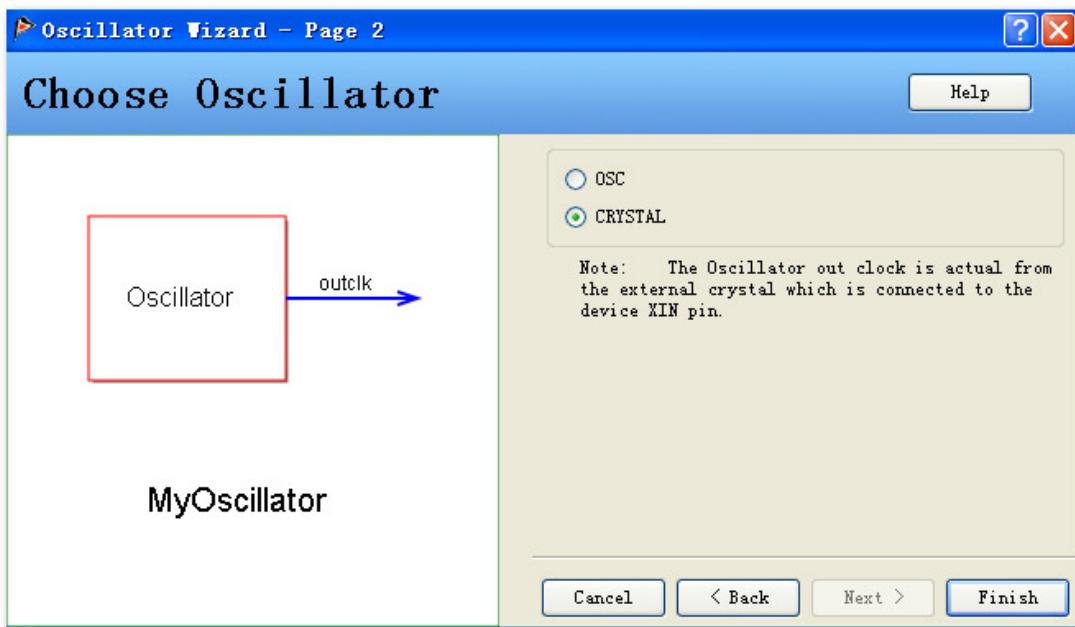

其中，选项 OSC 是芯片内的晶振，CRYSTAL 是外接晶振。这里我们选择外接 PCB 上的外接 20MHz 晶振。

然后在添加 PLL。

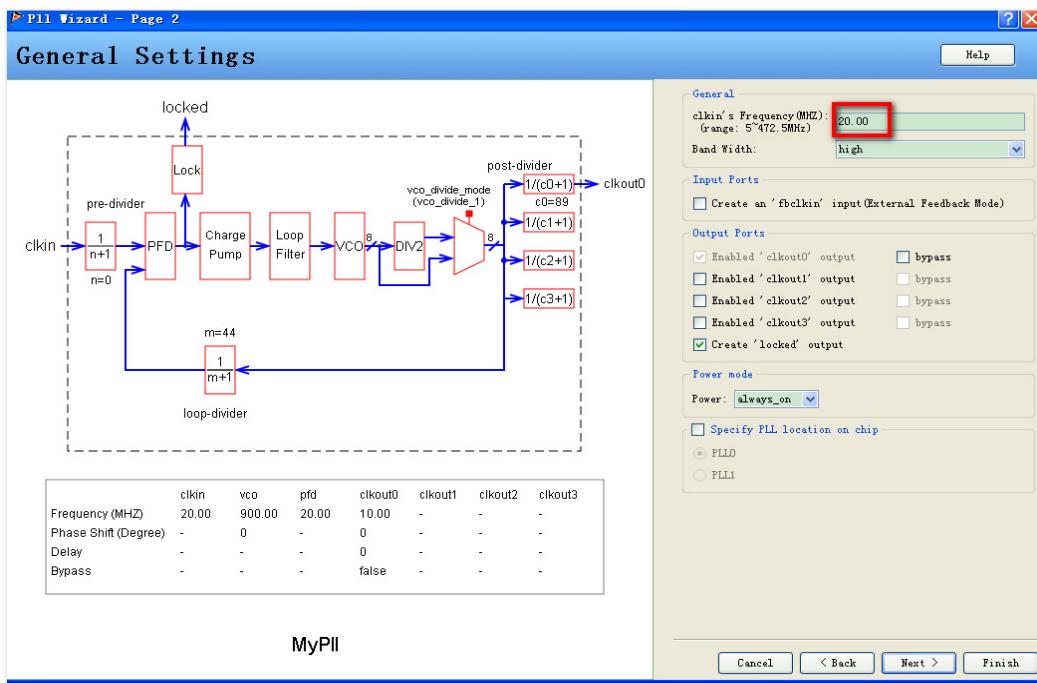

PLL 的输入时钟频率填写数据 20.00Hz.

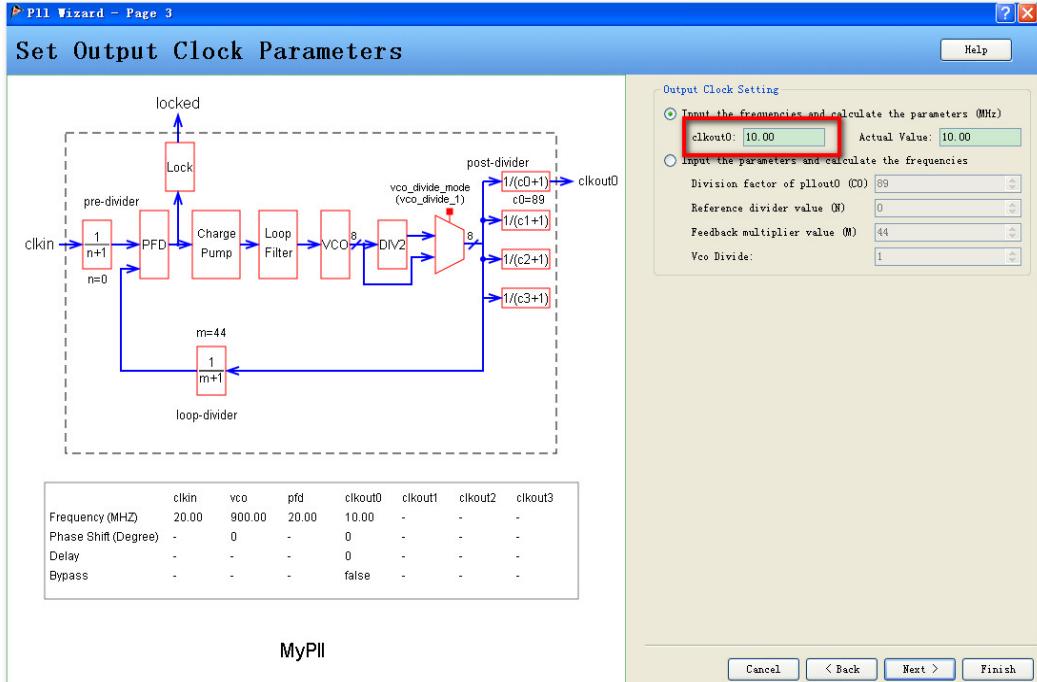

这里输出只改变其输入时钟频率，填为 10MHz。可选范围参考用户手册。

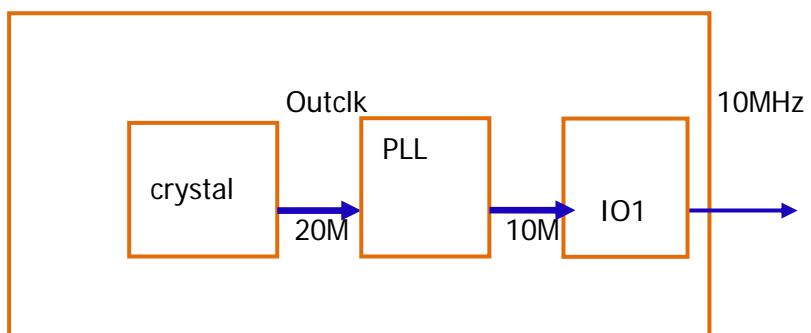

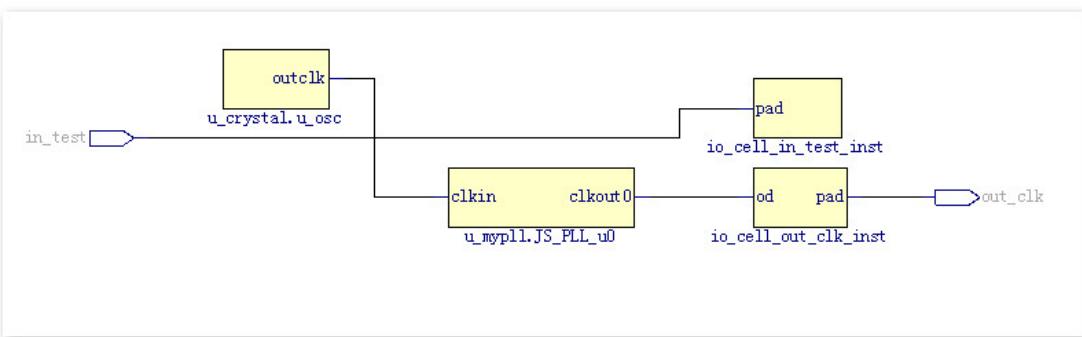

电路连接关系如图：

顶层 verilog 代码如下：

The screenshot shows the Capital Micro Primace software interface. The project structure on the left includes a 'crystal' folder containing 'crystal.v', 'MyOscillato...', and 'MyPll.v'. The main window displays the Verilog code for the 'top' module:

```

1 module top();

2   in_test,

3   out_clk

4 );

5   input in_test;

6   output out_clk;

7

8   wire osc_clk;

9

10  MyOscillator u_crystal(

11    .clkout(osc_clk)

12  );

13

14  MyPll u_mypll(

15    .clkin(osc_clk),

16    .clkout0(out_clk)

17  );

18

19 endmodule

```

一点小提示：目前的 Primace 版本，要求顶层 Verilog 必须有至少一个输入，如果没有会报错。以后版本会改进。所以即使没有使用，也请加上一个。

打开 IoEditor  ,进行引脚分配，如图：

| Assigned Port | Location |           |                |            |             |         |                    |            |           |

|---------------|----------|-----------|----------------|------------|-------------|---------|--------------------|------------|-----------|

| out_clk       | IO1_0    |           |                |            |             |         |                    |            |           |

| Port Name     | Location | Direction | Operation Mode | Fast Input | Fast Output | Fast OE | Drive Strength(mA) | Bus Keeper | Slew Rate |

| in_test       |          | input     | normal         | false      | false       | false   | 4mA                | none       | fastest   |

| out_clk       | IO1_0    | output    | normal         | false      | false       | false   | 4mA                | none       | fastest   |

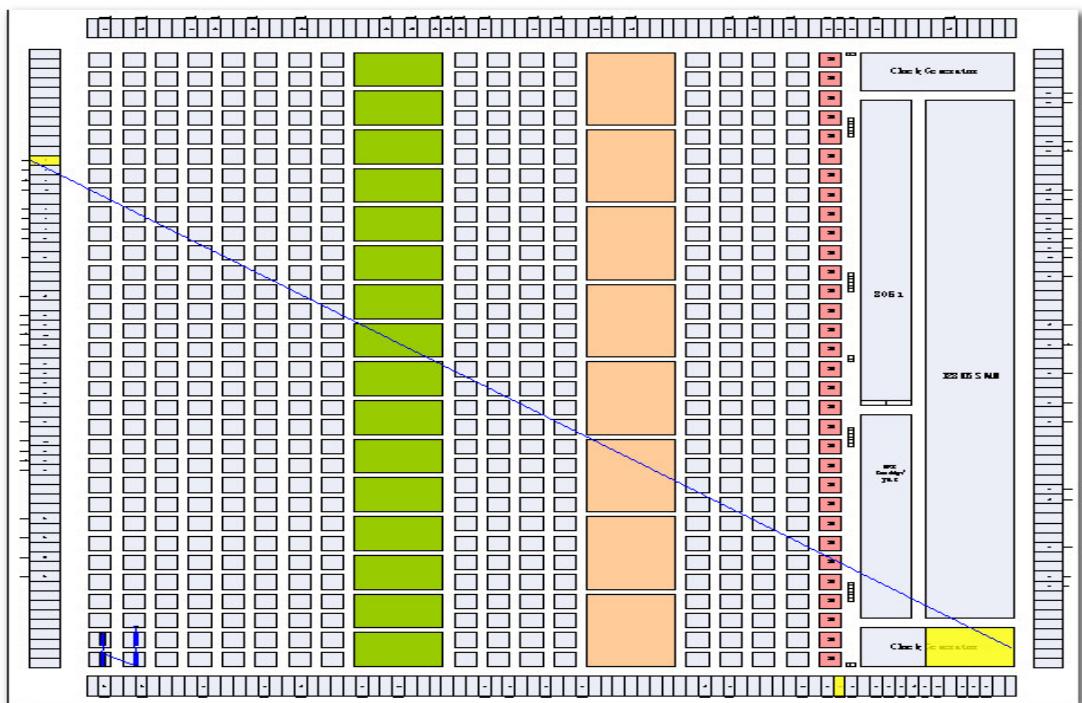

跑完 flow , 可以用 chipeditor 查看资源使用及连线情况 : 右下角黄色方框中为一块 PLL , 左边黄色标识为 IO1.

也可以打开 Tools ->Netlist Viewer->...查看综合后电路示意图 , 如 :

下载到 top\_spi.acf 到芯片 flash 中 , 在管脚 IO1 处 , 用示波器查看输出频率为 10MHz。