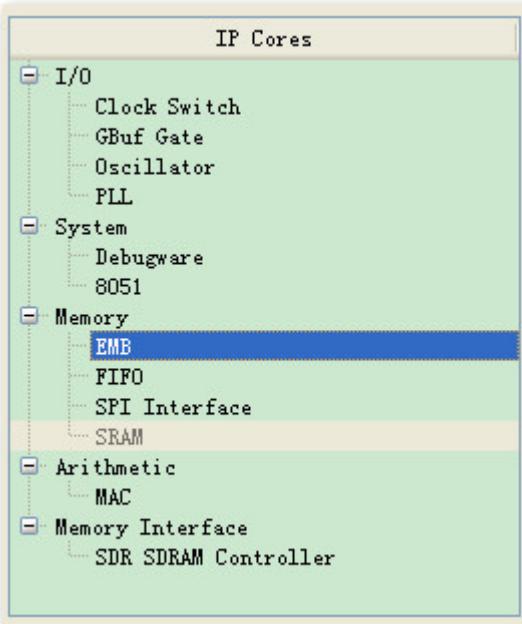

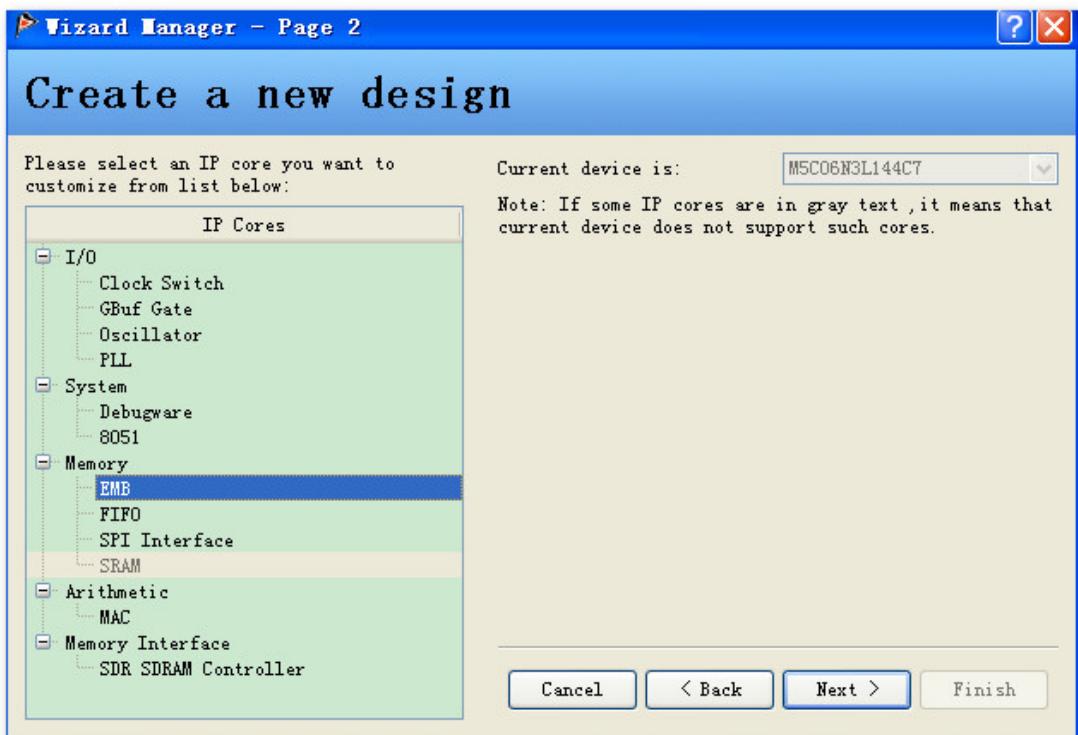

Primace4.1.2 提供一系列的 IP , 如图。

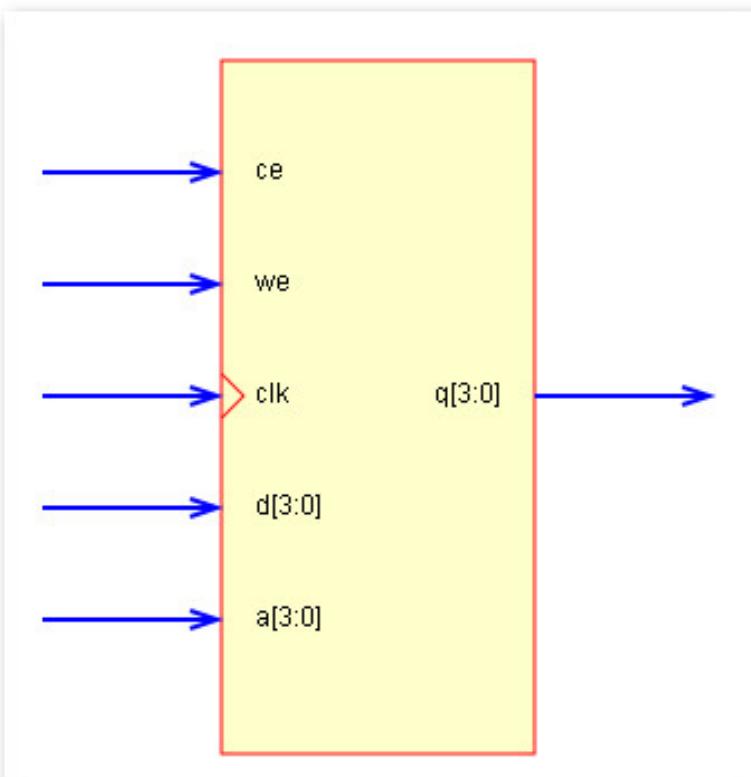

这里提供的是一个关于 EMB 使用的小例子。可以认为 , EMB 是一块存储区。按照一定的时序 , 可以进行数据的读写。

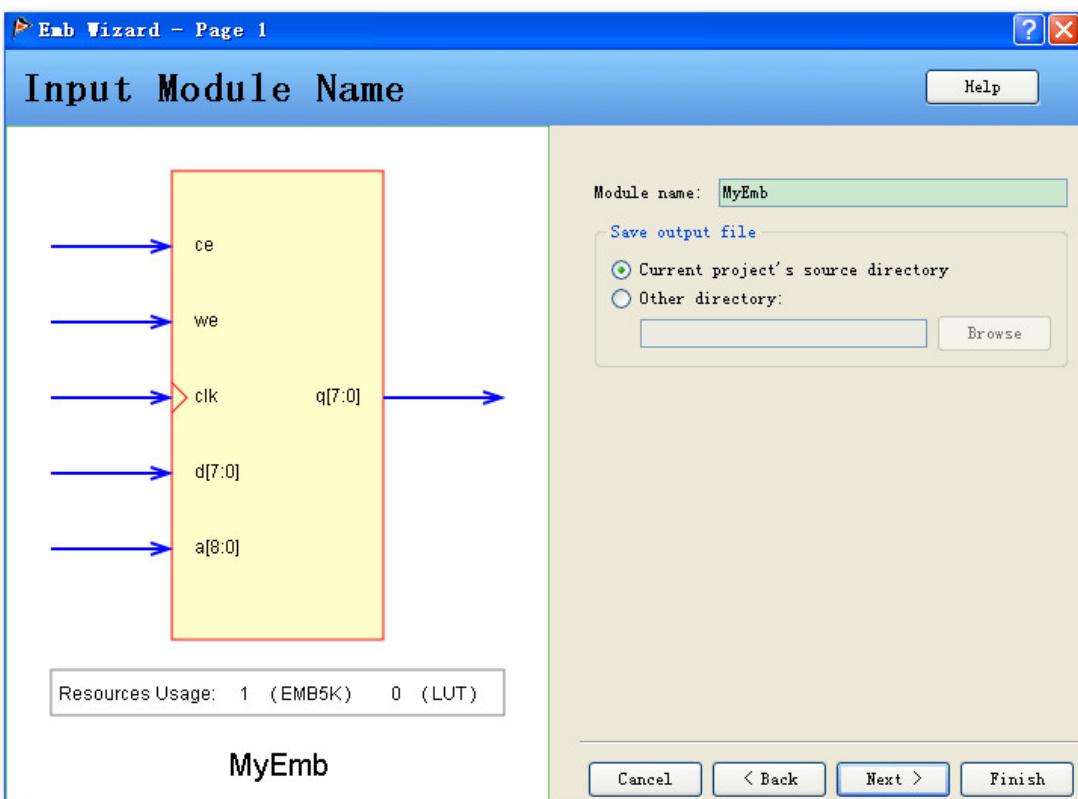

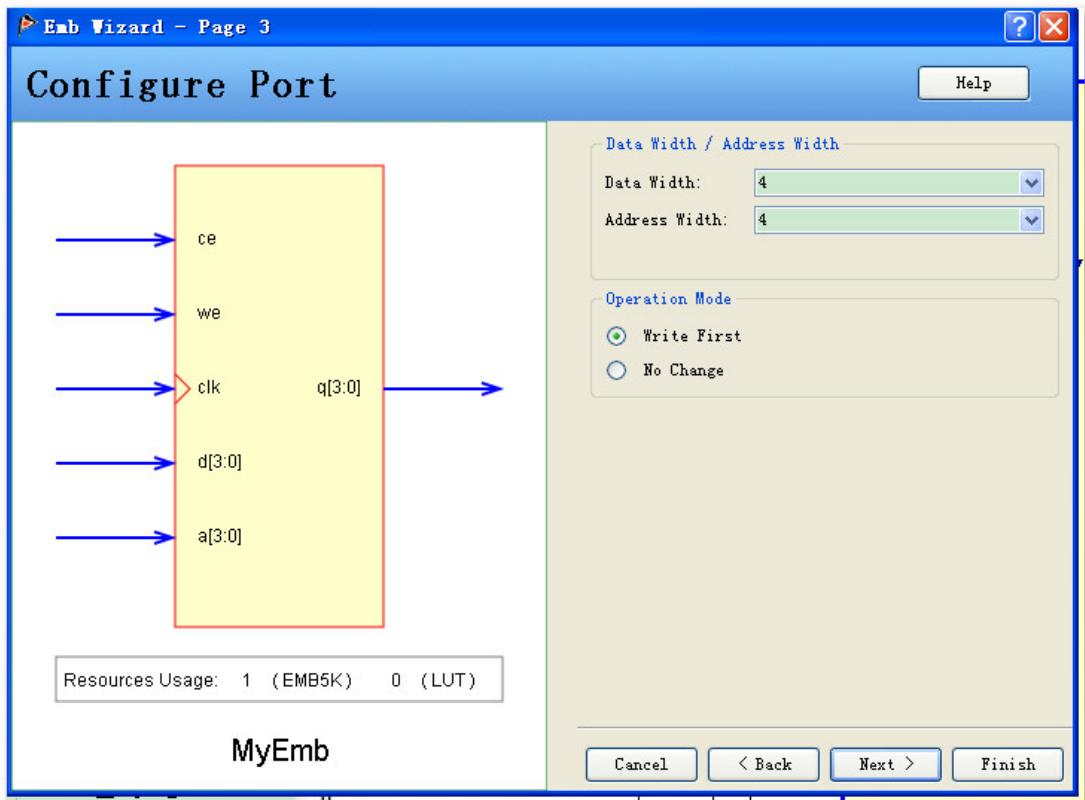

可以用 wizard 例化一块 EMB。点击图标

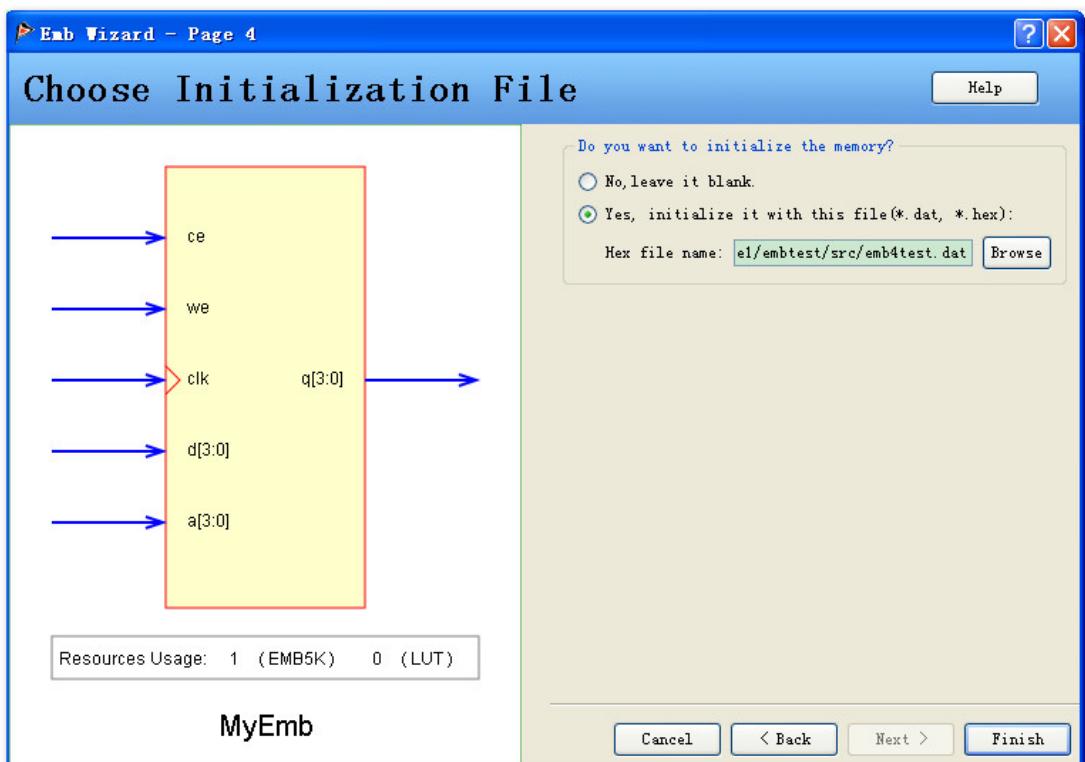

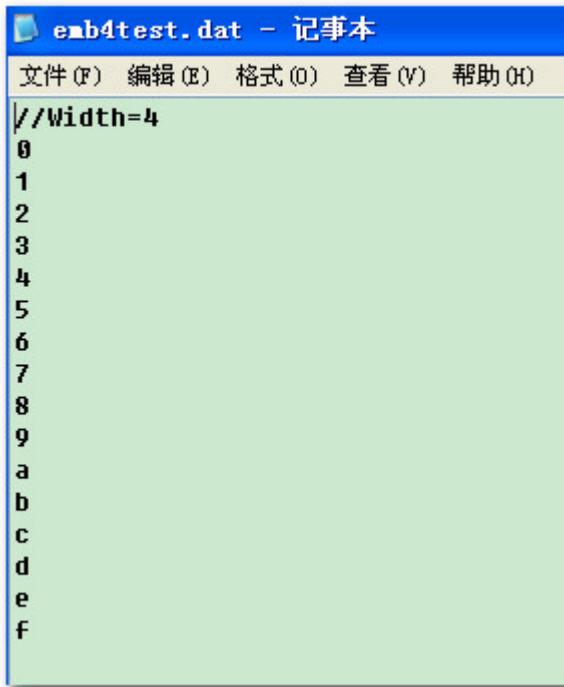

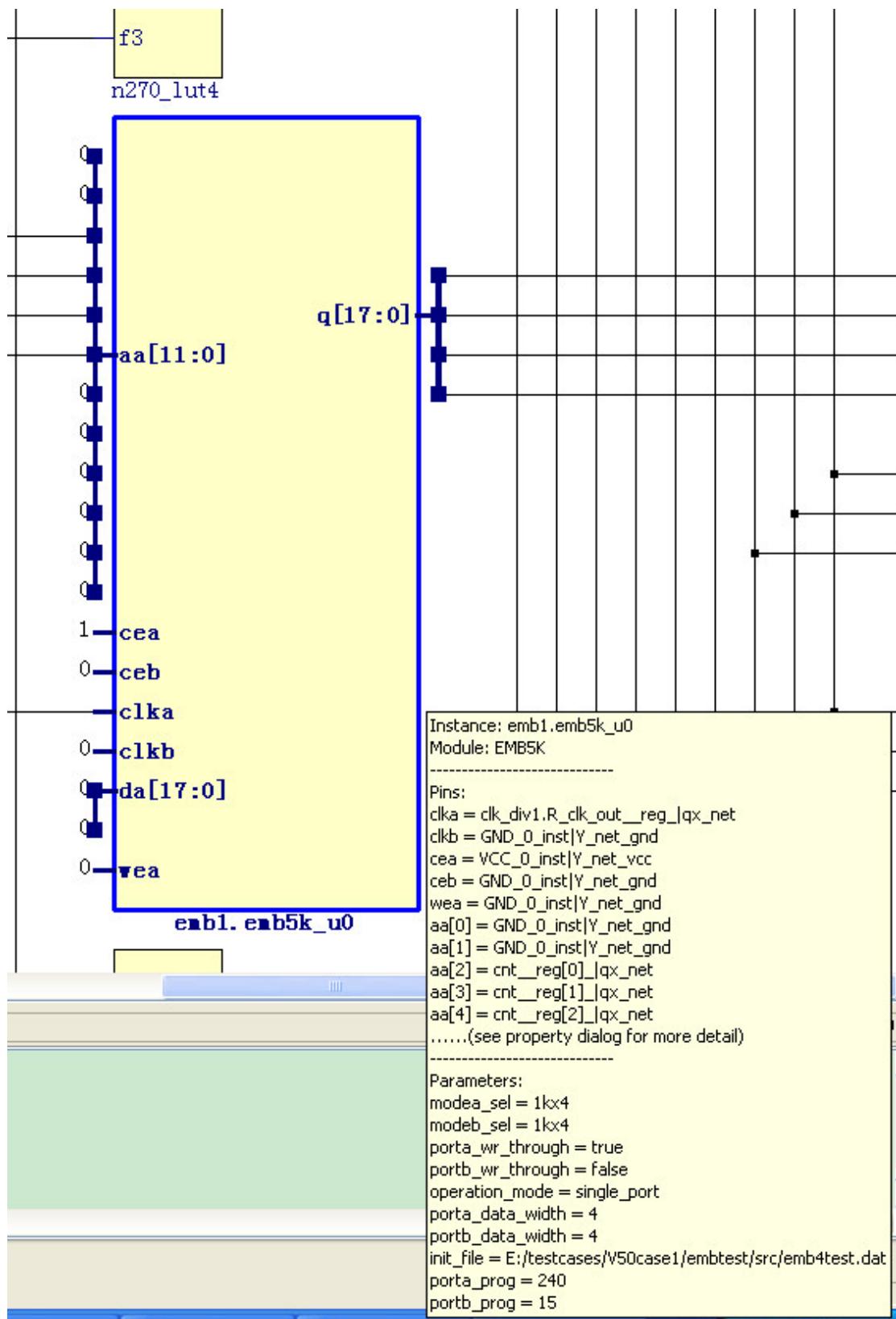

这个例子中，我们用文件 emb4test.dat 初始化 EMB，存入数据 0,1,2.....。

```

//Width=4

0

1

2

3

4

5

6

7

8

9

a

b

c

d

e

f

```

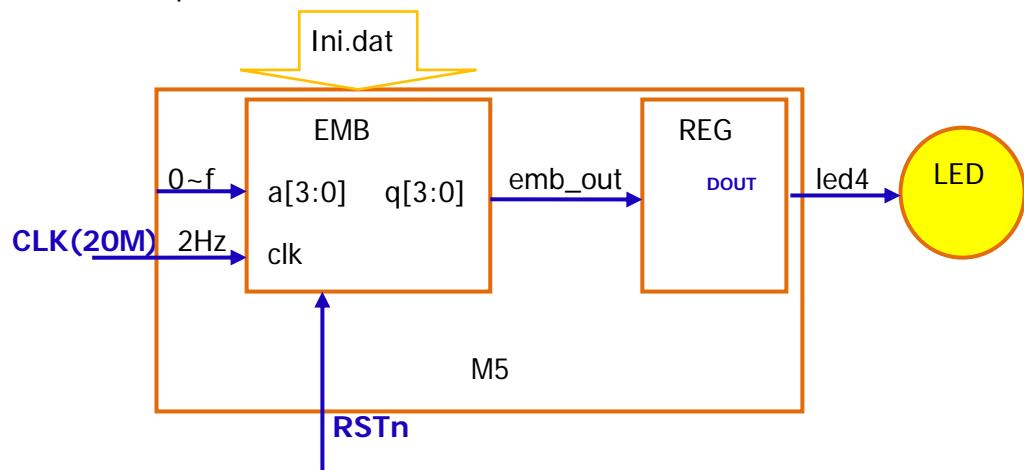

然后按照时钟频率 2Hz ( 20M 的 10000000 分频 ) 在地址 0x0 ->0xf->0x0->0xf...循环取数据 , 从 q 端输出。电路连接关系如图 :

顶层 verilog 代码如下 :

Capital Micro Prime - E:/testcases/V50casel/embtest/embtest.apj - [top]

File Edit View Project Flow Tools Window Help

Project

div.v top.v \* MyEmb.v top.aoc

```

1 module top(CLK, RSTn, DOUT);

2   input CLK, RSTn;

3   output [3:0] DOUT;

4

5   wire [3:0] emb_out;

6   wire [3:0] emb_ad;

7   wire clk_20;

8

9   reg [3:0] led4;

10  reg [3:0] cnt;

11

12  clk_div clk_div1(

13    .clk_in(CLK),

14    .clk_out(clk_20)

15  );

16  MyEmb emb1(

17    .clk(clk_20),

18    .a(emb_ad),//address

19    .d(),

20    .ce(1'b1),

21    .we(1'b0),

22    .q(emb_out)

23  );

24  always @(posedge clk_20 or negedge RSTn)

25  begin

26    if (!RSTn)

27    begin

28      cnt <= 0;

29    end

30    else if (cnt == 15)

31    begin

32      cnt <= 0;

33    end

34    else

35    begin

36      cnt <= cnt + 1;

37    end

38  end

39  always @(posedge clk_20 or negedge RSTn)

40  begin

41    if (!RSTn)

42    begin

43      led4 <= 0;

44    end

45    else

46    begin

47      led4 <= emb_out[3:0];

48    end

49  end

50  assign emb_ad = cnt;

51  assign DOUT = ~led4;

52 endmodule

53

```

Files Design

Progress View

Process Progress

Netlist Viewer: 100%

```

>module clk_div(clk_in, clk_out);

input clk_in;

output clk_out;

reg R_clk_out = 0;

reg [23:0] counter = 0;

always@ ( posedge clk_in )

begin

if(counter <= 9999999)

begin

counter <= counter + 1;

end

else

begin

counter <= 0;

end

end

always@ ( posedge clk_in )

begin

if ( counter <= 4999999 )

begin

R_clk_out <= 1;

end

else

begin

R_clk_out <= 0;

end

end

assign clk_out = R_clk_out ;

endmodule

```

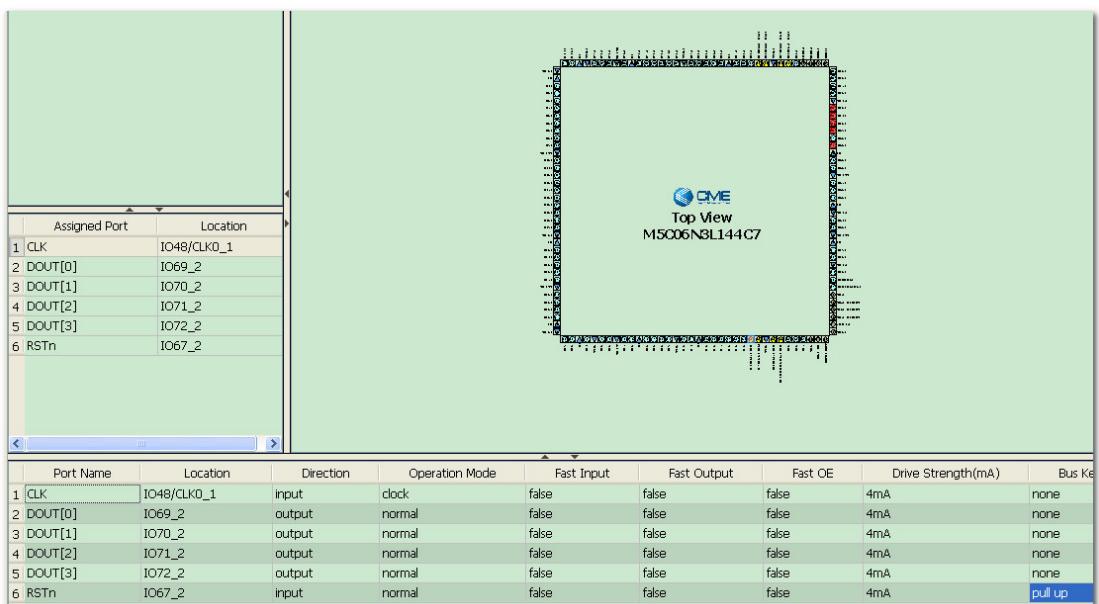

打开 IoEditor  ,进行引脚分配 , 如图 :

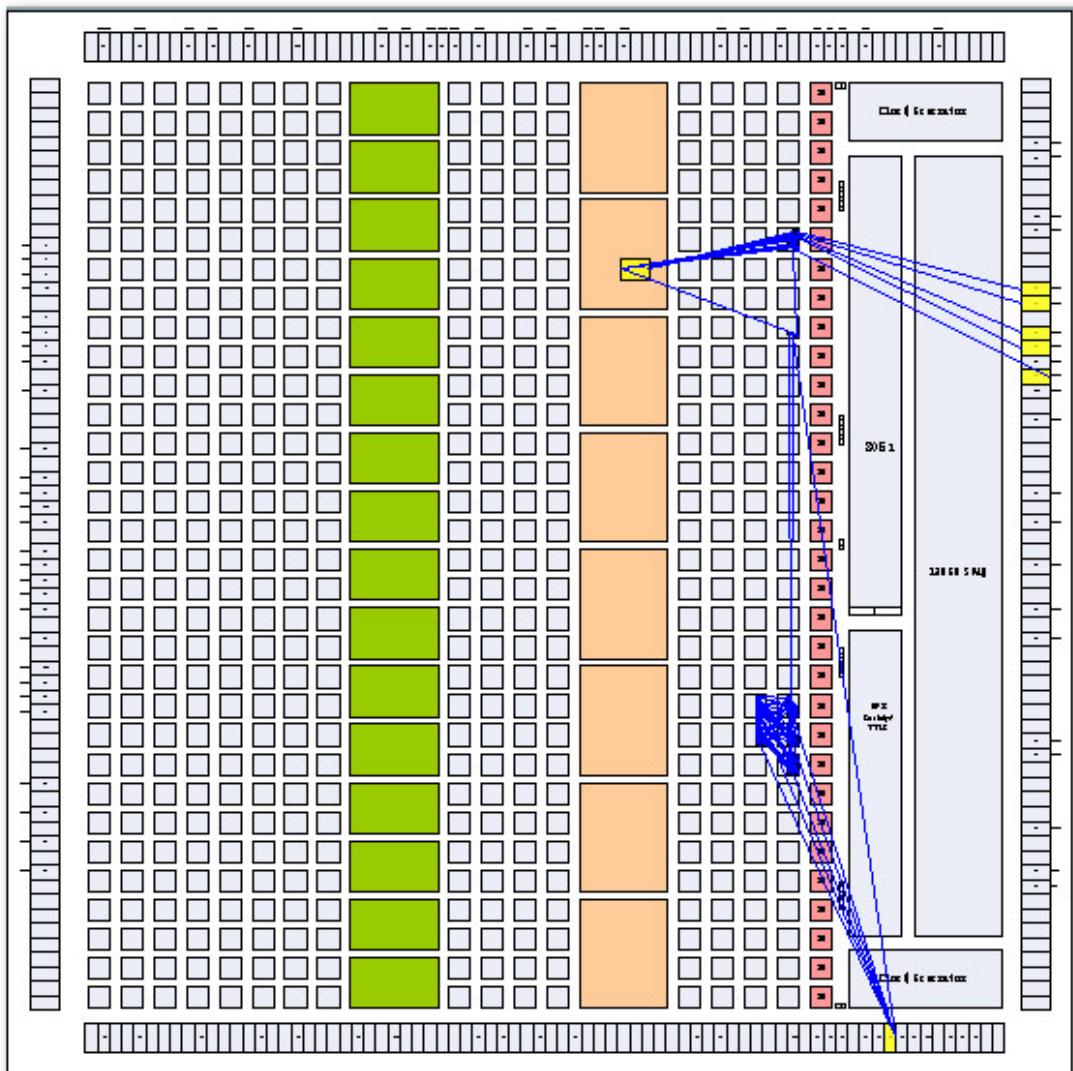

跑完 flow，可以用 chipeditor 查看资源使用及连线情况：橘黄色方框中的黄框为一块 EMB，周边的黄色标识为 IO.

也可以打开 Tools ->Netlist Viewer->...查看综合、绕线后的的示意图，如：

下载到 top\_spi.acf 到芯片 flash 中，发现小灯 D6 D5 D4 D3 按照 0,1,2,3...f 顺序闪烁起来。按 SW9，芯片复位。