# 现代 DAC 和 DAC 缓冲器有助于提升系统性能、简化设计

作者：Padraic O'Reilly 和 Charly El-Khoury

在许多控制系统的核心部分，数模转换器(DAC)在系统的性能和精度方面起着关键作用。本文将考察一款新型精密 16 位 DAC，同时针对性能可与变压器媲美的高速互补电流输出 DAC 的输出缓冲谈一些想法。

## 电压开关式 16 位 DAC 提供低噪声、快速建立时间和更出色的线性度

作者：Padraic O'Reilly

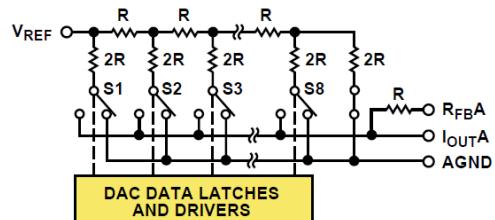

基于突破性 10 位 CMOS AD7520——推出已近 40 年——的电阻梯乘法 DAC 最初用于反相运算放大器，而放大器的求和点( $I_{OUTA}$ )则提供了方便的虚拟地 (图 1)。

图 1. CMOS 乘法 DAC 架构

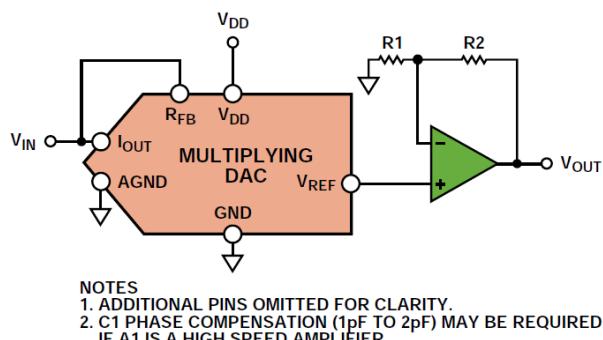

然而，在某些限制条件下，它们也可用于提供同相电压输出的电压开关配置，其中，运算放大器用作电压缓冲器 (图 2)。此处，基准电压  $V_{IN}$  施加于  $I_{OUT}$ ，输出电压  $V_{OUT}$  则由  $V_{REF}$  提供。后来不久即出现了针对这种用途而优化的 12 位版本。

图 2. 电压开关模式下的乘法 DAC

快速推进到现在：随着单电源系统的不断普及，设计师面对一个挑战，即在维持高电压下的性能水平的同时控制功耗。对能用于这种模式的更高分辨率 (最高 16 位) 的器件的需求也日益增加。

在电压开关模式下使用乘法 DAC 的显著优势是不会发生信号反相，因此，正基准电压会导致正输出电压。但当用于该模式时，R-2R 梯形架构也存在一个缺陷。相对于同一 DAC 用于电流导引模式的情况，与 R-2R 梯形电阻串联的 N 沟道开关的非线性电阻将导致积分线性度(INL)下降。

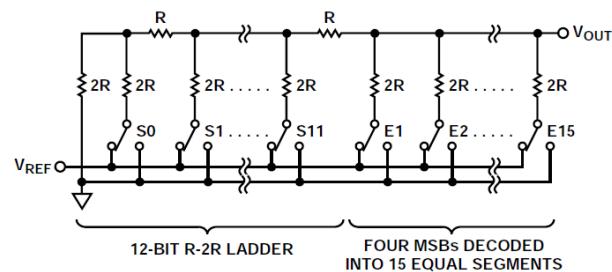

为了克服乘法 DAC 的不足并同时保持电压开关的优势，人们开发出了新型的高分辨率 DAC，比如 AD5541A (如图 3 所示)。AD5541A 采用一个部分分段的 R-2R 梯形网络和互补开关，在 16 位分辨率下可实现  $\pm 1$ -LSB 精度，在  $-40^{\circ}\text{C}$  至  $+125^{\circ}\text{C}$  的整个额定温度范围内均无需调整，其噪声值为  $11.8 \text{ nV}/\sqrt{\text{Hz}}$ ，建立时间为  $1 \mu\text{s}$ 。

图 3. AD5541A 架构

## 性能特点

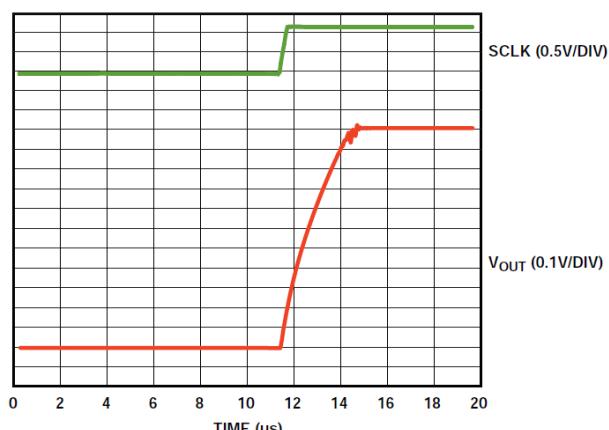

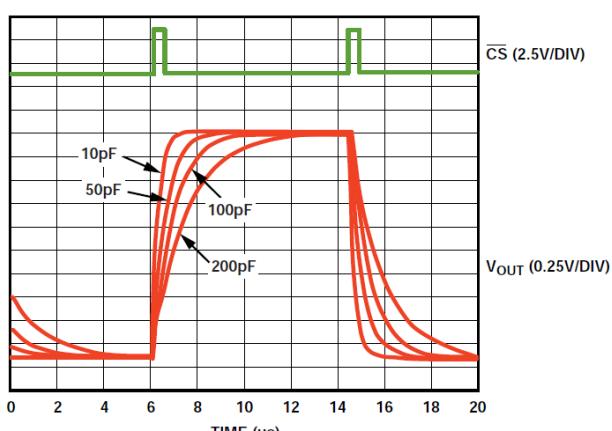

**建立时间：**图 4 和图 5 比较了乘法 DAC 在电压模式下的建立时间以及 AD5541A 的建立时间。当输出上的容性负载最小时，AD5541A 的建立时间约为  $1 \mu\text{s}$ 。

图 4. 乘法 DAC 的建立时间

图 5. AD5541A 的建立时间

**噪声频谱密度:** 表 1 比较 AD5541A 和乘法 DAC 的噪声频谱密度。AD5541A 在 10 kHz 下的性能略占优势, 在 1 kHz 下优势非常明显。

表 1. AD5541A 与乘法 DAC 的噪声频谱密度

| DAC     | 噪声频谱密度<br>(10 kHz (nV/√Hz)) | 噪声频谱密度<br>(1 kHz (nV/√Hz)) |

|---------|-----------------------------|----------------------------|

| AD5541A | 12                          | 12                         |

| MDAC    | 30                          | 140                        |

**积分非线性:** 积分非线性(INL)衡量 DAC 的理想输出与排除增益和失调误差之后的实际输出之间的最大偏差。与 R-2R 网络串联的开关可能会影响 INL。乘法 DAC 一般采用 NMOS 开关。当用于电压开关模式时, NMOS 开关的源极连接至基准电压, 漏极连接至梯形电阻, 栅极由内部逻辑驱动 (图 6)。

图 6. 乘法 DAC 开关

要使电流在 NMOS 器件中流动,  $V_{GS}$  必须大于阈值电压  $V_T$ 。在电压开关模式下,  $V_{GS} = V_{LOGIC} - V_{IN}$  必须大于  $V_T = 0.7$  V。

乘法 DAC 的 R-2R 梯形电阻设计用于将电流平均分配至各个引脚。这就要求总接地电阻 (从各引脚顶部看) 完全相同。这可以通过调节开关来实现, 其中, 各个开关的大小与其导通电阻成比例。如果一个引脚的电阻发生变化, 则流过该引脚的电流将发生变化, 结果导致线性度误差。 $V_{IN}$  不能大到会使开关关闭的程度, 但必须足以使开关电阻保持低位, 因为  $V_{IN}$  的变化会影响  $V_{GS}$ , 从而导致导通电阻发生非线性变化, 如下所示:

$$R_{ON} = \frac{1}{\beta(V_{GS} - V_T)}$$

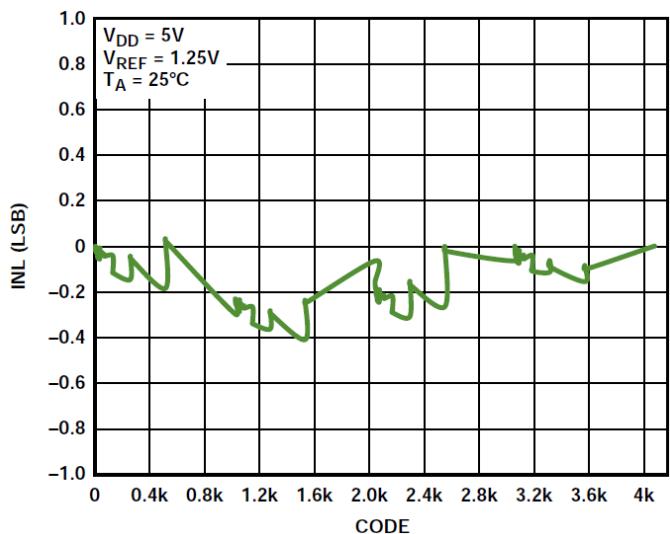

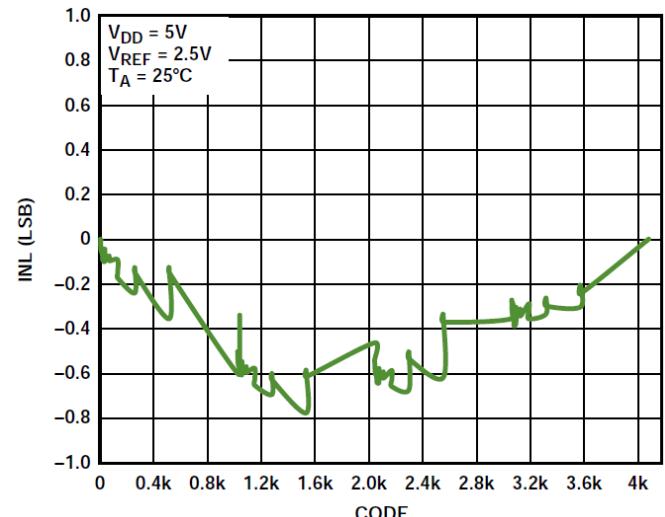

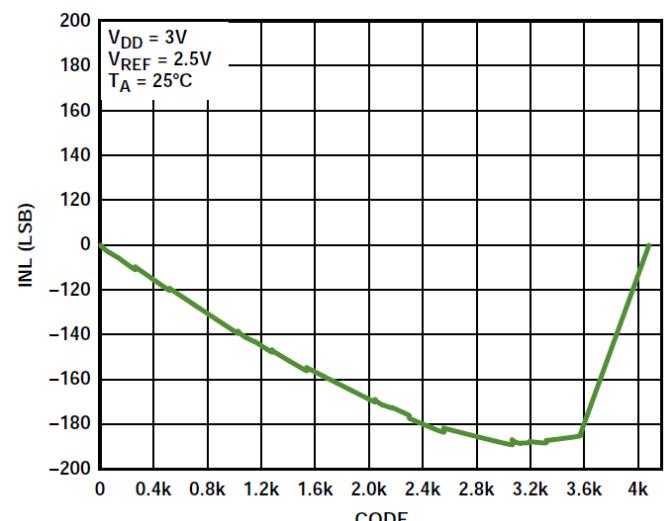

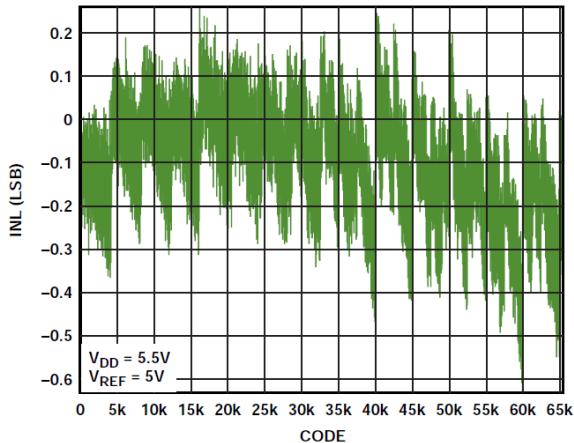

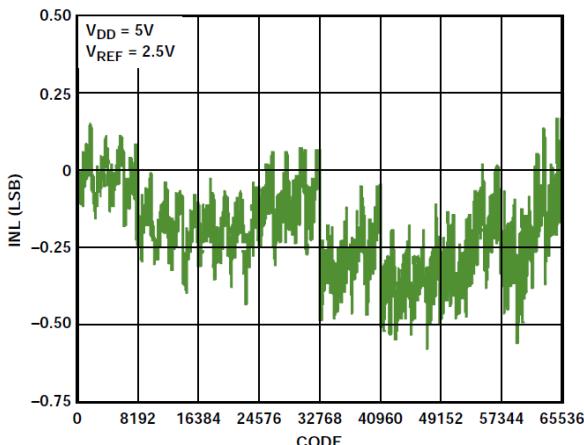

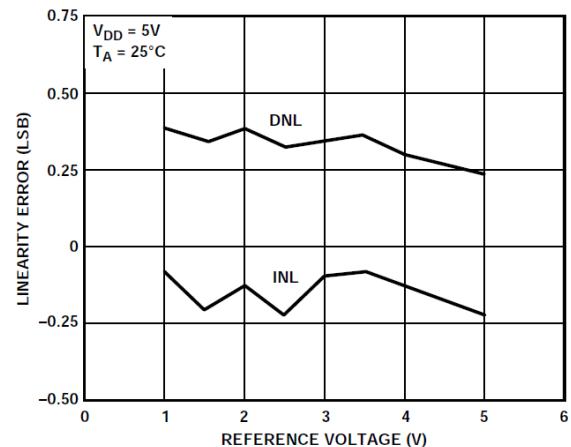

导通电阻的这种变化会使电流失衡, 并使线性度下降。因此, 乘法 DAC 上的电源电压不能减少太多。相反, 基准电压超过 AGND 的值不得高于 1 V, 以维持线性度。对于 5 V 电源, 当从 1.25 V 基准电压变化至 2.5 V 基准电压时, 线性度将开始下降, 如图 7 和图 8 所示。当电源电压降至 3 V 时, 线性度将完全崩溃, 如图 9 所示。

图 7.  $I_{OUT}$  乘法 DAC 在反相模式下的 INL

( $V_{DD} = 5$  V,  $V_{REF} = 1.25$  V)

图 8.  $I_{OUT}$  乘法 DAC 在反相模式下的 INL

( $V_{DD} = 5$  V,  $V_{REF} = 2.5$  V)

图 9. 乘法 DAC 在反相模式下的 INL

( $V_{DD} = 3$  V,  $V_{REF} = 2.5$  V)

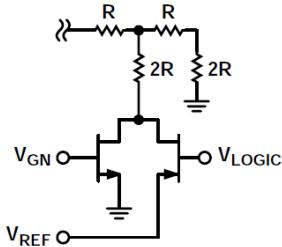

为了减少这种影响，AD5541A 采用互补 NMOS/PMOS 开关，如图 10 所示。现在，开关的总导通电阻来自 NMOS 和 PMOS 开关的共同贡献。如前所示，NMOS 开关的栅极电压由内部逻辑控制。内部产生的电压  $V_{GN}$  设置理想栅极电压，以使 NMOS 的导通电阻与 PMOS 的相平衡。开关的大小通过代码调节，以使导通电阻随代码调节。因此，电流将上下调节，精度将得以维持。由于基准输入的阻抗随代码变化，因此，应通过低阻抗源驱动。

图 10. 互补 NMOS/PMOS 开关

图 11 和图 12 所示为 AD5541A 在 5 V 和 2.5 V 基准电压下的 INL 性能。

图 11. AD5541A 的 INL ( $V_{DD} = 5.5$  V,  $V_{REF} = 5$  V)

图 12. AD5541A 的 INL ( $V_{DD} = 5.5$  V,  $V_{REF} = 2.5$  V)

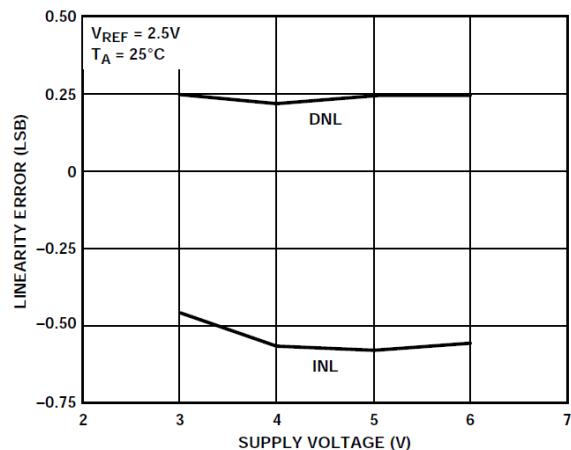

如图 13 和图 14 所示，线性度在较宽的基准电压和电源电压下变化极小。DNL 行为与 INL 类似。AD5541A 线性度的额定范围以温度和电源电压为基础；基准电压可能从 2.5 V 变化至电源电压。

图 13. AD5541A INL 与电源电压

图 14. AD5541A INL 与基准电压

## AD5541A 的更多详情

**AD5541A** 串行输入、单电源、电压输出 nanoDAC+数模转换器提供 16 位分辨率和  $\pm 0.5$  LSB 典型积分/微分非线性特性。特别适合将乘法 DAC 用于电压开关模式的应用。在额定温度范围和电源电压范围内均有优异表现，可实现出色的线性度，并可用于需要精密直流性能和快速建立时间的 3 V 至 5 V 系统。采用 2 V 至电源电压范围内的外部基准电压时，无缓冲电压输出可以将 60 k $\Omega$  负载从 0 V 驱动至  $V_{REF}$ 。该器件可以在 1  $\mu$ s 内建立至  $\frac{1}{2}$  LSB，噪声为 11.8 nV/ $\sqrt{\text{Hz}}$ ，并具有低毛刺特性，非常适合部署在各种医疗、航空航天、通信和工业应用中。其 3 线式低功耗 SPI 串行接口能够以高达 50 MHz 时钟速率工作。AD5541A 采用 2.7 V 至 5.5 V 单电源供电，功耗仅 125  $\mu$ A。它提供 8 引脚和 10 引脚 LFCSP 及 10 引脚 MSOP 封装，额定温度范围为  $-40^{\circ}\text{C}$  至  $+125^{\circ}\text{C}$ ，千片订量报价为 6.25 美元/片。

# 高速电流输出 DAC 缓冲器

作者: Charly El-Khoury

变压器通常被认为是将高速电流输出 DAC 的互补输出转换为单端电压输出的最佳选择, 因为变压器不会增加噪声, 也不会消耗功率。尽管变压器在高频信号下表现良好, 但它们无法处理许多仪表和医疗应用所需要的低频信号。这些应用要求一个低功耗、低失真、低噪声的高速放大器, 以将互补电流转换成单端电压。此处展示的三个电路接受来自 DAC 的互补输出电流, 并提供单端输出电压。将后两者的失真与变压器解决方案进行比较。

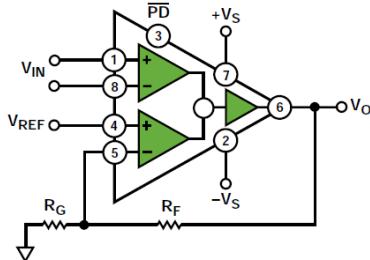

**差分放大器:** AD8129 和 AD8130 差分转单端放大器 (图 15) 用于第一个电路 (图 16)。它们在高频下具有极高的共模抑制性能。AD8129 在增益为 10 或以上时保持稳定, 而 AD8130 则在单位增益下保持稳定。它们的用户可调增益可以由  $R_F$  和  $R_G$  两个电阻的比值来设置。AD8129 和 AD8130 在引脚 1 和引脚 8 上具有很高的输入阻抗, 不受增益设置的影响。基准电压 ( $V_{REF}$ , 引脚 4) 可以用来设置偏置电压, 该偏置电压被乘以与差分输入电压相同的增益。

图 15. AD8129/AD8130 差动放大器

图 16. 采用 AD8129/AD8130 的 DAC 缓冲器

方程 1 和方程 2 所示为放大器的输出电压与 DAC 的互补输出电流之间的关系。端接电阻  $R_T$  执行电流-电压转换;  $R_F$  与  $R_G$  之比决定了增益。 $V_{REF}$  在方程 2 中被设为 0。

$$V_{IN} = I_1 R_T - I_2 R_T = R_T (I_1 - I_2) \quad (1)$$

$$\begin{aligned} V_O &= \left(1 + \frac{R_F}{R_G}\right) (V_{IN} + V_{REF}) \\ &= \left(1 + \frac{R_F}{R_G}\right) R_T (I_1 - I_2) \end{aligned} \quad (2)$$

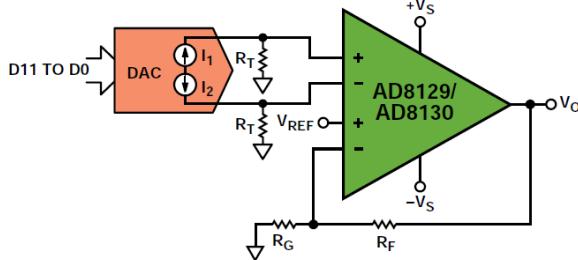

在图 16 中, 该电路采用一个四通道高速、低功耗、14 位 DAC, 其中, 互补电流输出级将提高速度, 降低低功耗 DAC 的失真。

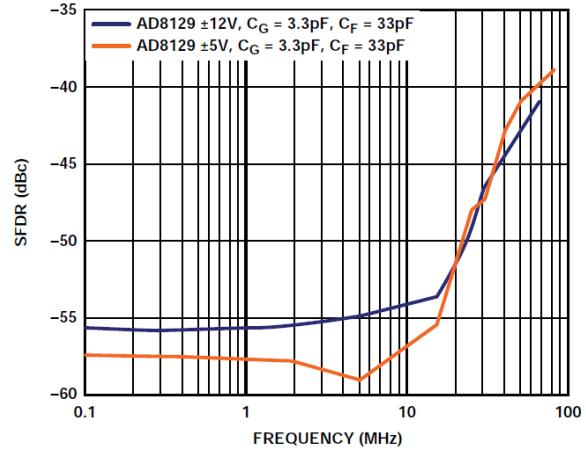

图 17 展示的是电路的无杂散动态范围(SFDR), 它是频率的函数, 采用 DAC 和 AD8129, 其中,  $R_F = 2 \text{ k}\Omega$ ,  $R_G = 221 \Omega$ ,  $R_T = 100 \Omega$  且  $V_O = 8 \text{ V p-p}$ , 两个电源电压对应的不同值。此处选择了 AD8129, 因为它提供较大的输出信号, 在  $G = 10$  时保持稳定, 与 AD8130 相比, 具有较高的增益带宽积。两种情况下, SFDR 一般都要好于 55 dB, 超过 10 MHz, 在低电源电压下, 约有 >3 dB 的改善。

图 17. DAC 和 AD8129 的失真 ( $V_O = 8 \text{ V p-p}$ )

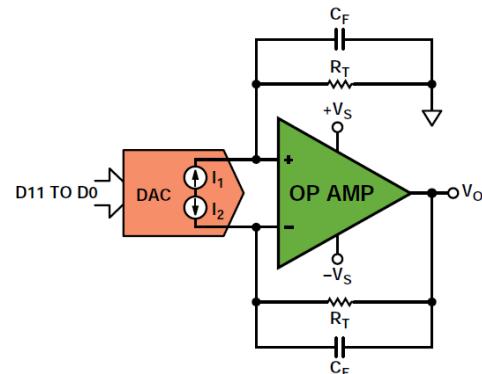

**单位增益下的运算放大器:** 第二个电路 (图 18) 采用了一个高速放大器与两个  $R_T$  电阻。该放大器只是通过  $R_T$  将互补电流  $I_1$  和  $I_2$  转换成单端输出电压  $V_O$ 。这个简单的电路不允许以放大器为增益模块放大信号。

图 18. 采用运算放大器的简单差分到单端转换器

方程 3 所示为  $V_O$  与 DAC 输出电流之间的关系。失真数据通过与  $R_T$  并联的 5 pF 电容进行测量。

$$V_O = (I_1 R_T - I_2 R_T) = R_T (I_1 - I_2) \quad (3)$$

为了展示这个电路的性能, DAC 与 ADA4857 和 ADA4817 运算放大器配对, 其中,  $R_T = 125 \Omega$  ( $C_T = C_F = 5 \text{ pF}$  与  $R_T$  并联, 以实现稳定性和低通滤波)。单通道 ADA4857-1 和双通道 ADA4857-2 为单位增益稳定型、高速、电压反馈放大器, 具有低失真、低噪声和高压摆率等特点。作为众多应用 (包括超声、ATE、有源滤波器、ADC 驱动器等) 的理想解决方案, 其带宽为 850 MHz, 压摆率为 2800 V/μs, 0.1% 建立时间为 10 ns——全部都是在 5 mA 的静态工作电流下实现。ADA4857-1 和

ADA4857-2 具有宽工作电压范围 (5 V 至 10 V)，特别适合需要宽动态范围、精密、高速度和低功耗的系统。

ADA4817-1 (单通道) 和 ADA4817-2 (双通道) *FastFET™* 放大器是具有 FET 输入的单位增益稳定、超高速电压反馈型运算放大器。它们采用 ADI 公司的专有超快速互补双极性(XFCB) 工艺制造，具有超低的噪声 (4 nV/√Hz 和 2.5 fA/√Hz) 和极高的输入阻抗。其输入电容为 1.3 pF，最大失调电压为 2 mV，功耗低(19 mA)，-3 dB 带宽较宽(1050 MHz)，非常适合数据采集前端、光电二极管前置放大器以及其他宽带跨阻应用。它们具有 5 V 至 10 V 的宽电源电压范围，可采用单电源或双电源供电，适合包括有源滤波、ADC 驱动和 DAC 缓冲在内的各种应用。

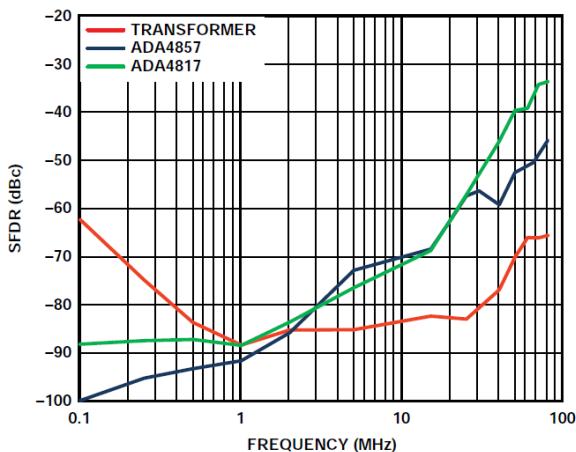

图 19 比较了该电路在  $V_o = 500$  mV p-p 时相对于一个采用变压器的电路的失真和频率之间的关系。变压器的失真低于放大器，后者的增益在高频下不断下降，但采用变压器的失真却在低频下不断变差。在此，可在有限范围内实现接近 90 dB 的 SFDR，在高达 10 MHz 时优于 70 dB。

图 19. DAC、ADA4857 和 ADA4817 的失真

( $V_o = 500$  mV p-p,  $R_L = 1$  kΩ)

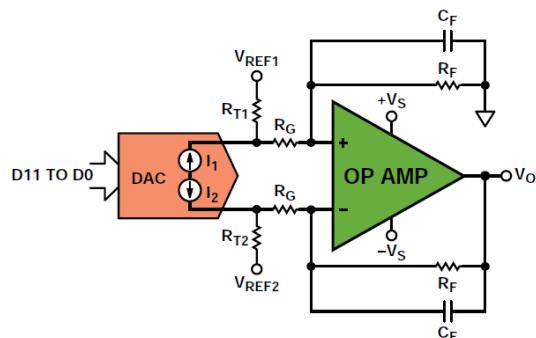

**具有增益运算放大器：**第三个电路 (图 20) 也使用了相同的高速运算放大器，但所含电阻网络拉远了放大器与 DAC 之间的距离，支持增益设置，并可以利用  $V_{REF1}$  和  $V_{REF2}$  两个基准电压之一调整输出偏置电压。

图 20. 支持增益和偏置功能的差分到单端转换

方程 4 定义了 DAC 输出电流与放大器输出电压在  $V_{REF1} = V_{REF2} = 0$  时的关系。为了匹配 DAC 之外的放大器网络的输入阻抗， $R_{T1}$  和  $R_{T2}$  两个端接电阻必须单独设置，同时要考虑放大器的特性。

$$V_o = I_1 \left( \frac{R_{T1} \times R_F}{R_{T1} + R_F + R_G} \right) \left( 1 + \frac{R_F}{R_G + R_{T2}} \right) \quad (4)$$

$$- I_2 \left( \frac{R_{T2} \times R_F}{R_G + R_{T2}} \right)$$

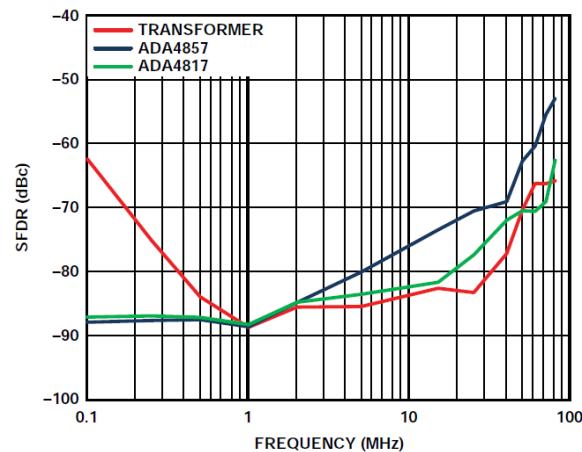

图 21 比较了放大器在这种配置下的失真以及变压器电路的失真。 $R_{T1} = 143 \Omega$ ,  $R_{T2} = 200 \Omega$ ,  $R_F = R_G = 499 \Omega$ ,  $C_F = 5 \text{ pF}$ ——出于稳定性和高频滤波考虑——且  $R_L = 1 \text{ k}\Omega$ 。在此，ADA4817 的性能可与变压器在高频下的性能相媲美，在最高 70 MHz 时，其 SFDR 可维持在优于 -70 dBc 的水平。与变压器相比，两个运放都能维持出色的低频保真。

图 21. DAC、ADA4817 和 ADA4857 的失真 ( $V_o = 500$  mV p-p)

本文讨论了将低失真、低噪声、高速放大器用作 DAC 缓冲器的一些优势，并将其性能与变压器进行了比较。同时比较了采用两种不同架构的三类应用电路，并以实例展示了 DAC 和 AD8129、ADA4857-1/ADA4857-2 以及 ADA4817-1/ADA4817-2 放大器的测量数据。数据显示，放大器在频率低于 1MHz 时的性能优于变压器，在频率不超过 80 MHz 时，非常接近变压器。在权衡考虑功耗和失真时，放大器的选择非常重要。

### 作者简介

**Padraic O'Reilly** [padraic.oreilly@analog.com] 是精密数模转换器部门的应用工程师。他于 2007 年毕业于利默里克大学，获电子工程学士学位，之后加入 ADI 公司。

**Charly El-Khoury** [charly.el-khoury@analog.com] 高速放大器部门的应用工程师。他于 2006 年毕业于伍斯特理工学院(WPI)，获得电气与计算机工程(ECE)硕士学位，之后加入 ADI 公司。