#### 文档号: BR8BITBYNDBITS Rev 1

# 超越比特位

# 从零到实现ZigBee, 只需几分钟!

#### BeeKit™无线连接工具包

实际上, 您只需30分钟就可以构建一个小型网络并开始运行。秘诀就是我们的开发软件环境及其高度直观的图形化用户界面(GUI)。它使您的团队可以在一个即时且集中的环境中进行协作 — 无论他们是在另一幢大楼里还是

在另一个大陆上。在最终确定软件结构之前,团队成员可以自由而独立地进行试验和创新。不管是复杂的网状网络,还是简单的点到点网络,开发时间都可缩短数周。它以

最快的方式将ZigBee设计推向市场。

## 超越比特位

### 第二期实现了界限的突破

欢迎阅读第二期《超越比特位》! 在一这期中,我们扩大了讨论的范围,涵盖了在飞思卡尔 产品系列中采用的多种技术,包括8位微控制器(MCU)、32位ColdFire控制器、我们曾获大奖 的16位数字信号控制器(DSC)及ZigBee®无线技术等。此外,我们还增加了一个来自设计 联盟合作伙伴的内容,以及飞思卡尔客户如何用我们的产品和服务取得成功的实例。

本期所包含的技术文章有一个共同的主题,那就是为您提供实际的方案和可以解 决问题的 参考资料。其内容对各个层次的技术人员都非常适合,而且我相信,不管是对于提高专业 技术水平还是开发新设计,您都会发现它是有用的。

《超越比特位》第二期中的许多文章可帮助您设计成本敏感的应用。一些文章所讨论的 激动人心的新技术可以帮助您达成设计目标。还有一些文章著重介绍了飞思卡尔的控制 器联合体(Controller Continuum) — 行业的第一个也是唯一的8位和32位兼容架构的路线 图。

无论您为工业、消费类还是汽车市场开发产品,我们所拥有的广泛产品系列必能满足 您的需求,帮助您获得丰厚的投资回报。因此,请深入其中,您会发现飞思卡尔的创新 技术是如何帮助您简化设计过程的。

本期与第一期相比有了很大的改进,其中很大一部分应归功于你们的重要建议。欢迎 阅读这一期并继续提供宝贵的反馈意见。最重要的是,感谢您在现在或以后的设计中 想到飞思卡尔。

顺颂商祺!

Mike McCourt

副总裁兼总经理

飞思卡尔半导体微控制器业务部

通过frescale.com/beyondbits发送您对产品的看法、诀窍或问题。

# 超越比特位

# 目录

| <b>控制器联合体</b>                               |

|---------------------------------------------|

| 成功之路10<br>Robert Lewis                      |

| <b>低功率考量</b> 13<br>Inga Harris              |

| 超低功率无线设计                                    |

| JTAG TAP的有效控制22<br>David Baca               |

| 加速创新                                        |

| <b>DSP56800E中的高速32位除法</b>                   |

| 马达控制及电源设计31 Daniel Torres                   |

| 最新S08/RS08工具36<br>Inga Harris               |

| <b>ZigBee®与低成本无线网络</b>                      |

| <b>针对成本敏感应用的微控制器</b> 48 Dr. Martin Mienkina |

| <b>如何构建简单的无线应用</b>                          |

| <b>飞思卡尔设计联盟计划</b>                           |

| 采用8位MCU的BLDC马达控制60 Pavel Grasblum           |

| <b>LCD驱动的诀窍</b>                             |

| <b>SMAC无线连接的简单实现</b>                        |

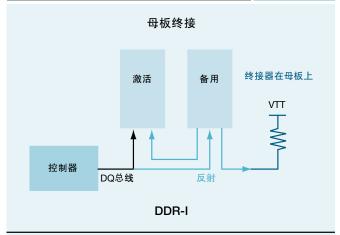

| <b>DDR存储器的比较和综述</b> 70 Joaquin Romo         |

| <b>如何使用HCS08的TPM模块</b>                      |

| 产品概览                                        |

Jeff Bock和Joe Circello

# 控制器联合体

# 解决从8位到32位的过渡问题

长期以来,从8位到32位MCU的过渡对设计人员来说 一直是一个严峻的挑战。许多因素都要求建立一个不同 功能的处理器的统一平台;然而,现有的8位和32位的 专业知识只能了解各自领域用户的需求。本文将介绍 飞思卡尔如何认识这个过渡问题,修改软硬件设计的 理念,并最终定义了具有兼容的封装、外围设备和工具的8位和32位新产品。这种硅芯片设计方法有望简化并加快大量的最终产品的性能升级,使客户能够更快地将产品推向市场。

#### 性能路径

微控制器的应用范围非常广泛,从简单替换采用固态技术的传统机电功能,到已经数年发展、如今需要高级32位MCU的极其复杂的控制应用。虽然有几家公司能提供可以支持多种应用的单一解决方案,但没有哪家公司提供可以从8位到32位MCU实现轻松过渡的产品。目前,对低端8位MCU和中端16位MCU的需求正在迅速增长。如果这些应用需要更高的性能,答案可以在多种低成本32位架构中找到。然而,对于从8位和16位MCU进行移植的用户来说,他们会感觉32位架构有很大的不同。这通常需要新的硬件工具,因此移植就成了一项昂贵而耗时的工作。

通过充分利用飞思卡尔在8位和32位MCU领域的丰富经验,我们定义了一种可帮助用户简化过渡过程,并重复使用软件和工具的方法。中级性能的MCU通常是根据价位、功耗、外围设备和/或特定应用所需的性能水平等定义的,而不是根据比特位定义的。在大多数情况下,客户并不在乎比特位,他们只关心能否解决系统问题。一个8位到32位的联合体可以在这段空白上架起桥梁,让客户从当前的系统需求入手,同时规划未来的改进计划,且无需进行重大修改,也不必为先期的工具和软件再追加投资。

###

#### 内核

8位与32位内核之间的无缝过渡从8位级产品开始。成熟的HCS08(S08)内核奠定了8位性能的基础并配备了丰富的外围设备。新近开发的RS08内核将S08中央处理器(CPU)的大小缩小了30%,并为联合体提供了更大的产品范围。该内核的目标是用电子控制代替机电设备的低成本应用,在管脚数较少的封装中配置不到16K的闪存,而且所用的指令更少,编码更紧凑、更高效。这种体积更小、更高效的内核充分利用了为广大S08应用开发的外围设备。

在高端产品方面,先进的32位ColdFire V1内核可以 提供转换链条上缺失的环节。V1平台由V1内核、本地 内存(闪存和SRAM)、后台调试模块(BDM)和总线桥 组成。总线桥提供内核的本地高速总线与辅助外围设备 模块之间的互连,它还是将一种协议转换成另一种协议 的总线接口。

一般情况下,V1平台部分的运行速度是外围设备模块的两倍。除了提供总线协议转换功能外,总线桥模块还可以用作不同时钟区之间的接口。

采用成熟、易用的8位外围设备,加上16位内部架构和32位内核,8位和32位产品系列可以方便地连接起来,为工程师提供设计灵活性。

从8位迁移到16位MCU的决定是基于多种考虑的。根据 现有的处理技术,32位V1内核的价格与16位内核大致 相同。然而,可提供的性能却要高得多。

#### 通用外围设备

32位的V1 ColdFire通过IPS总线连接到8位S08外围设备模块。总线桥模块使V1平台部分能用高达外围设备模块2倍的速度运行。

#### 可互换的内核

8位S08内核和32位V1 ColdFire内核都可与众多的 S08外围设备一道使用,甚至可以封装在引脚兼容的 封装中。单引脚的BDM使8位和32位MCU可以使用 同样的CodeWarrior Development Studio开发套件。

#### 兼容的外围设备、封装和工具

多种因素促成8位与32位架构之间的无缝移植。进程从 内核开始,并涉及外围设备、封装以及开发工具。 从10多年前首次实施以来, ColdFire的指令集架构(ISA) 发生了很大变化,从最初只在一定程度上支持8位和16位 操作数,面向32位操作数的优化体系演变成扩展并改进 8位和16位操作数处理支持的架构。对于V1类的应用, 这对从8位和16位应用移植的用户尤其重要。在处理器 内核层,指令集是否能直接解决涉及8位和16位操作数的 高效处理问题,是非常重要的。

V1内核微架构实施了大量的优化,以提高那些处理8位和 16位操作数的指令的性能。V1不仅支持这些指令类型, 它们在V1通道中的执行也是优化过的。在有大量数据被 用作8位和16位操作数的应用中,对这些指令的支持和 快速执行时间可以实现大幅度的性能改进。

"控制器联合体"可以充分利用现有外围设备的知识产权 (IP)。外围设备模块连接通用总线的结构可以确保S08 IP的完全重复使用。结果,不管是飞思卡尔还是用户在 8位产品上的投资,在移植时都会得到保持,包括外围 设备驱动软件的重复使用。虽然可能还需要考虑定时和 其他一些问题,但这种方法确实可以使现有的外围设备 驱动软件继续发挥作用。

后台调试模式(BDM)曾是保持相同引脚数的困难之一。 传统ColdFire中的BDM是采用三针串行接口(时钟、数据 输入、数据输出)实现的,还用第四根针来提供断点功能。 这种BDM支持连续插入读/写寄存器和读/写内存命令的 功能,还可以运行和停止处理器等。由于S08用于更低端 应用中,管脚数也非常有限,所以传统ColdFire内核的 调试功能被重新映射到针对V1的单引脚接口上,与S08 完全一致。有关调试的改变的第二个部分与ColdFire内核 对实时追踪的支持有关。

对于V1来说,必须修改实时追踪操作。CPU可以输出 处理器状态信息、地址和调试数据等。然而,V1不像V2 和其他ColdFire MCU一样立即输出这些信息,而是采用了 一个PST(处理器状态)和调试数据追踪缓冲器。利用这个 方法,用户就可以设置开始和停止条件来记录追踪端口 发出的信息。这些信息被收集、压缩并载入追踪缓冲器中。 然后,用单引脚的BDM就可以读取跟踪缓冲器中的数据了。 这是一个非常有用的概念,由此可以捕捉跨越数百个机器 周期的活动,从而保留了追踪功能,只是把它们映射到 采用单引脚接口的技术上了。

8位到32位过渡的最大挑战是工具。主要的开发工具必须 是可互换的,并且在移植到32位时,要给8位用户提供 同样简洁的外观和感觉。采用一种新版本的CodeWarrior® 开发环境软件,用户可以用完全相同的工具、连接线和 CodeWarrior工具,直接将8位S08拿掉并用32位ColdFire V1内核替换。用户只需简单地重新编译一下用C语言开发 的代码即可。

#### 用户的工作有何不同

利用飞思卡尔的"控制器联合体",起初采用S08微控制器的 客户可以比以前更轻松地过渡到32位架构。通过过渡, 用户可以获得远远高于8位S08内核的32位内核的处理 功能。以相同速度运行时,32位V1估计可提供高达8位 S08架构十倍的性能。与RS08相比的性能改进幅度就 更大了。

如此大幅度的性能改进可开辟新的应用领域,而且可以 改变一个公司规划其长期产品路线图的方式。这样一种 基于简便易用的32位架构的方法,非常适合那些寻求轻松 获得32位性能的8位用户。

这种"联合体"的方法对那些寻求降低功耗和应用成本的 32位用户同样有效。V1采用了先进的低电压、低功率 流程,不管是在待机还是运行模式下都能提供一个非常 低功耗的32位MCU。此外,它的功率密度预计将是 独一无二的,可创建很多新的应用。

由于ColdFire V1 MCU产品具有高达S08器件10倍的 性能,因此有可能在某个应用中大幅提高产品的性能而 不必提高频率。对于那些对EMC敏感的应用,如家电和 洗衣机,这可能会是一个重要的优势。我们已经与很多 客户讨论并验证讨这些方法。一旦设计人员在设计过程中 看到采用这种新方法的可能性,他们会立即想到可以应用 干未来的设计的新途径。

#### 千里之始

通过对客户的反馈意见采取行动,"联合体"构建了扩展 的8位S08以及32位ColdFire。这种反馈导致了大量的 改进,包括指令集、硬件(包括调试功能)和这些器件的 开发工具,这一切使向上过渡变得十分简单。此外, 飞思卡尔正在推出Flexis™系列 — 首批管脚、外围设备 和工具都兼容的、处于控制器联合体的"连接点"上的8位 和32位微处理器。MC9S08QE128和MCF51QE128分别 采用S08和ColdFire V1内核,是Flexis系列中将这种 兼容性路线图变成现实的首款产品。

在大部分嵌入式控制设计中,很少是只有一个重要因素来 左右设计决策。决策一般是根据许多较小的,但也很重要 的细节的累加来制定的。8位到32位的"控制器联合体" 可以为系统设计人员提供独特的性能,让他们可以采取 "穷尽一切"的理念来优化功率、大小、性能、外围设备 使用和开发工具等等。此外,利用无缝地向上或向下过渡 的功能,该"联合体"可给公司提供长期规划的能力,进而 改变许多行业的产品路线图。

#### 参考文档

#### 飞思卡尔"控制器联合体"

www.freescale.com/files/abstract/overview/ TSP8773\_CONTINUUM.html

#### 飞思卡尔Flexis™ MCU系列

www.freescale.com/flexis

Jeff Bock是飞思卡尔MCU部门的全球产品营销经理。Jeff主要负责针对消费和工业领域的产品的启动和推广活动。 他在半导体行领域拥有10多年的经验。

Joe Circello是飞思卡尔半导体TSPG产品部的MCD处理器/平台设计师,负责通道组织、控制结构和性能分析。他在 摩托罗拉/飞思卡尔工作超过15年,一直担任MC68060和ColdFire系列产品的首席设计师。

#### Robert Lewis - 设计联盟合作夥伴

### 成功之路

### 嵌入式处理器和C

这个项目就像其他项目那样开始 — 有一个合理的营销 计划、功能规范以及可行的时间表。如果不是发生了那件 不可避免的事,一切都会按计划运行。可预测的变化 范围…"如果可能,我们需要加上它;倘若我们加上了, 我们就会真正改进产品,它不会很难的。毕竟,它只是 软件。"

且慢,让我们回顾一下刚开始的情况 — 项目实施之前。 项目很简单,选择一个频率,根据用户选择的设置将它 转换到另一个频率,然后在某种条件下输出。采用一个 简单的8位微控制器就可以实现这一点,但我们想要额外 的调试功能。当时908只有一个断点,因此我们选择了 HCS12系列。我们不想用汇编语言编程,因此C语言似乎 是唯一合理的选择,也是一个好方法。汇编器可能会很好 用,但是由于命名问题和寄存器寻址错误引起的编程一致 性标准的管理,以及对调试结果的管理造成的开销不值得 我们冒额外的风险。

接下来,我们开始寻找良好的ANSI编译器。我们考察了 CodeWarrior工具包,但考虑到项目的大小以及要执行的 有限功能,我们认为把大笔的预算花在工具包和全是开关 和选项的大堆文档上,似乎不太合理。这意味著仅仅在 了解交互式开发环境(IDE)上就要花费大量的时间。

因此我们开始考虑免费的第三方C编译器。免费的编译器 似乎足够稳定,然而很明显,我们需要大量的专业知识来 设置系统以进行编码和链接,而我们唯一可以得到的支持 就是去网上论坛。当时,我们没有足够的时间和背景知识 来处理如此之多的未知风险,因此我们只能将注意力放在 看起来比较好的第三方替代产品上。论坛中的用户对整个 ANSI C编译器的稳定性和支持赞赏有加,因此我们决定 使用所选的产品。

有了编译器,下一步就是调试器。购买2万美元的在线 仿真器(ICE)一定是很爽的,然而它看起来与我们300美元 的编译器和预算太不相称了,因此我们很快排除了它。 我们开始寻求不需要"在线仿真器"的产品。用评估模式 运行了这个产品几天之后,我知道我们做了一个正确的 选择。该产品拥有出色而合理的输出接口、稳定而且没有 冲突、意外停机、崩溃、锁死或其他常见的问题。我们 相信,这种产品将会非常好用。

在开始之前,我们还需要将另外几种工具结合起来。我们需要一个多版面编辑器、能跟踪修改的源代码保存库以及用于交叉参考和符号查找的源代码分析系统。这个用于源代码分析的开源产品是一个令人惊异的免费产品,具有许多功能,但遗憾的是没有相关文档。

现在,您可能看到了我们以前未能看到的前进方向。我们有效地构建了自己的IDE,因此也要负责集成和支持每一个方面。因为没有说明书,所以我们需要搞清楚如何让它运行。事实证明,这不是一件小事。

正如所料,让编译器和调试器运行花了很长时间。调试器是好的,但这个编译器是新版本的,因而在将目标代码正确写入闪存,以及正确地匹配分页寄存器的读写方面存在一些问题。不幸的是,问题发生时,编译器供应商正在度假。最后,我们得到了来自调试器团队的良好支持。他们找出了编译器中的不一致性,等到那个供应商回来时,编译器已经变得可以正确载入闪存了。

有一段时间一切都运行得很好,代码正在设计,有关命名规则、函数调用等方面的编码标准也或多或少地制定出来了。然后,第一次变化出现了。我们要去掉简单的BCD开关,用一个4行16字符的LCD和一个选择不同选项的按键来替代。("什么选项?BCD开关没有选项,它只有开关!它们只是开或关,只在启动时读一下!我们需要显示和开关…")

现在我们必须编写子程序来建立液晶控制寄存器、过滤地址和数据、编写定位字符的所有原代码,构建字符行,还有大约40个其他与显示器有关的子程序。做完这些之后,我们还要增加一个中断处理程序来运行5路开关。另外还需要一些子程序来跟踪菜单中光标处在哪一行。现在有了一大堆的功能,每个功能中有很多行,因此我们需要一个菜单来跟踪选项。

代码变长了,然而在下一个要求出现之前还是可管理的,这就是用户保存选项的方法。我的回答是:"如果您使用BCD开关,您就不需要保存任何东西,您只要看开关就可以了。"这个建议被拒绝了,然后我们就开始考虑采用串行数据连接。但是这样就需要一个PC应用程序。我们用面包板搭了一个串行连接电路,并用先进的第四代工具做这个PC应用程序,这之后我才知道串行传输本质上就极易出错,完全不适合我。如果失去同步,系统将会挂死;或者如果它错过一个字节,一切都会乱套并且做怪异的事情。唯一的解决方案是大量的握手软件。通过

大量工作之后,我们决定放弃使用与PC的动态连接,另外 采用一个带FAT文件系统的SD卡。一切也从此开始恶化。

SD卡将目标代码的输出增加了约20KB,并且出现了大量的问题。调试器开始显示代码会跑飞,进入完全无关的区域。在看似随机的时间,运行程序会跳到无关的函数。我们整天整天地编写代码来试图跟踪可能的堆栈问题,还有更多时间花在试图捕捉可能的错误中断上,结果都没有成功。最后,在调试工具的作者的帮助下,我们发现由于函数引用的顺序,以及引用函数时是内嵌式的而不是链接式的,编译器生成了错误的符号表和链接。编译器供应商为我们提供了一个变通方法,我们的业务恢复了运行,尽管有些不尽如人意。我们艰难地等待著永久性的解决方法,然而至少我们能够继续前进。

接著出现了字符显示"太滥"的说法,认为这降低了产品的价值 — 因此我们需要图形显示。无需非常奇特。它可以是单色的,只要比我们现在的字符显示精细和时髦就好。我的答复是:"BCD开关既时髦小巧、又颜色丰富",结果被认为既没有建设性也没有用处。

由于添加了带有字体表的图形子程序,目标代码又增加了 20KB,代码执行过程中也出现了更多问题。编译器似乎 在设置分页寄存器上遇到了的问题。编译器供应商已在 尽其全力解决这一问题来支持这个产品了,然而论坛上的 交流帖子显示,他的公司将大量的时间花费在为另一家 制造商的产品开发新编译器上了。

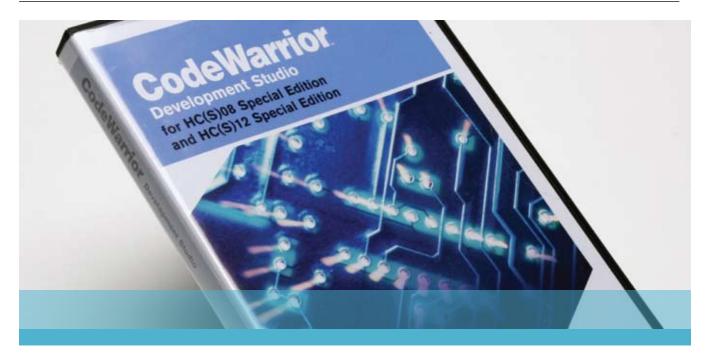

这是压垮骆驼的最后一根稻草;我们最后不得不承认,如果要继续使用我们开发出的代码库,就必需一个能确保稳定性的产品。唯一的选择就是重新考虑使用CodeWarrior工具包。我们不会天真地认为CodeWarriorIDE没有自己特定品牌的问题,然而我们的确知道,只有像飞思卡尔这样生产处理器并提供工具包的大型跨国公司,才会拥有非常强大的动力来保持工具包的最新性和可操作性。

因此,我们购买了完整版的CodeWarrior IDE,但没有购买完整版的Processor Expert™ Bean。该版本使我们可以构建各种规模的代码库,它还拥有一些基本的Processor Expert目标代码。当时我们对Processor Expert beans一无所知。看起来似乎只要掌握了CodeWarrior工具包就可以开始使用了。

我浏览了一些飞思卡尔网站上的培训课程,过程似乎没有我最初设想的那么令人生畏。接著,我开始转换代码。

我没有调节讨任何编译器或连接程序开关,只是使用默认 设置。

大约两天后,我们完成了代码的编译和链接,没有出现 任何错误。由于我们曾经使用的编译器是兼容ANSI的, 因此几乎没做什么修改。主要的修改在干文件系统的 命名、那些与CodeWarrior中定义端口和ECT配置的文件 相冲突的Pragma声明和构件。原来的文件系统使用了 几个ANSI库预留的函数,如fopen()和fclose()。它们 很容易修改,只要重新命名函数调用为fopen\_imn即可。 Pragma的修改非常直观也非常容易。

我们加载了代码并开始运行,令我们惊异的是它运行 得十分顺畅 — 第一次就这样。不仅如此,由于 CodeWarrior IDE是一种优化编译器而我们的旧编译器 不是,因此CodeWarrior代码容量要小30%,而且明显 快得多。在我们以前的代码库中所遇到的所有问题和 Bug都消失了。而且还有一个惊喜,我们的老朋友(那个 非在线的仿真器)调试器可以用CodeWarrior的ELF输出 运行。因此我们既可以使用CodeWarrior调试器,也可以 使用以前选择的工具进行调试。目前我们使用的是 X-Gate处理器,因此我们需要更经常地使用CodeWarrior 调试器了。

以事后之见,您可从中学到什么?尽管我做大型控制系统 项目已经有30多年了,但我仍然陷入了我经常警告别人 注意的小陷阱中。如果不用我的钱,我会购买最好的工具 和所有其他必需的东西来确保以最小的风险尽快完成 项目。如果用我的钱(或部分是),我就会花时间挑选较低 成本的工具,因为我相信我的经验能使它很好地运行; 而且在一定程度上的确是这样。然而当涉及其他人员时, 有可能出现你无法控制项目结果的情况。即使以非常低的 费率计算我的时间,也比购买CodeWarrior工具支付的 费用要高出好多倍。此外,这还不包括情感方面的投入或 项目延误造成的损失。有时,大量投资购买工具可能 不可行。然而,有了免费的支持高达32KB的程序大小的 CodeWarrior工具包,以及优化得很好的编译器,我们 可以构建以前不太合适的很多项目。然后,一旦项目足够 大的话,应该就会有能够负担额外开支的资金了。

如果您依靠的是一个拥有较小客户群的小供应商,这个 供应商可能会受到他们不能控制的因素的影响。例如, 主要员工的流失、疾病或收入的变化都有可能影响这些 供应商的交付能力。

这可能不是一个在所有项目中都值得考虑的因素。这是否 影响您的决策过程取决于最终的用户。如果您的产品是 同一类型,而且您可以在本地通过变通方法迅速地支持 客户,那么可能根本就没有风险。您可能从未遇到过 编译器和连接程序的Bug,或是因为您的代码库较小, 或是过去的项目经过了全面的测试,所以新代码可轻松 完成调试和隔离。然而,如果您是构建的是一个将用干 实时控制系统或大规模生产的产品,一旦在最终用户方 发现错误,会造成大规模的收入损失以及信任度的丢失。 这种类型的项目需要即时响应,所以重新考虑考虑一下 您的"保险策略"可能是一种比较明智的做法。也就是说, 当您为经过证明、有支持的产品支付额外费用时,您可以 升级支持问题并得到响应。这可能不能立即解决问题, 但总比被告知"我们之前从没遇到过这种问题;看看论坛上 是否有人能提出相关建议"要好得多。那是一种危机中的 茫然无助的感觉。

我是否提到了我们穿过Processor Expert beans的朦胧 地带的经历?没有?那么,下次再说吧。

Robert Lewis是iMn MicroControl公司的工程师。他拥有电子工程专业理科学士学位和硕士学位,专业是基于微 处理器的系统。

#### Inga Harris

# 消费和工业应用的 **低功率考量**

消费和工业市场一直要求新产品设计具有更高的电源效率。每一代新的便携式产品都需要提供更长的电池寿命,而大型产品(如白色家电)则需要更高的能效比来保持竞争力。在许多情况下,用电子器件替代机械部件可以改善电路板的功耗,而另外的软件控制可以精细地调整应用的功率性能。

产品器件的发展使工程师可以使用新的设计理念和技术来克服早期产品的功率使用限制。由于以下两个方面的原因,微控制器(MCU)成了实现功率降低创新的关键:第一,MCU本身就消耗功率;第二,MCU控制消耗功率的其他系统器件。因此,MCU制造商需要将极低功耗的特性结合到他们最新的产品设计中。

本文著重描述了飞思卡尔采取哪些措施来满足这一市场需求,同时还介绍为了降低功耗所采用的方法和增加的特性。最重要的是,它介绍了如何在应用设计中充分利用这些方法和特性。

通过在最新的低功耗8位MCU即MC9S08QE128上运行一个通用应用,重点介绍节能的实现。本文将通过逐一开启S08QE128上的每种节能特性来显示各个特性对应用功耗的影响。

#### 功率与性能

系统设计人员总是要在适合其应用需求的功耗(Amp)和性能(MIPS)之间寻求平衡。一般而言,器件的时钟频率越高,它们所消耗的能量就越多。在大部分时间都在运行的应用中,以系统能够容忍的最低速度运行的解决方案就是最高效的方案。这种系统的一个实例就是电机控制器。如果其主要功能是通过模数转换器(ADC)通道转换信号,那么根据Nyquist定律,ADC的时钟频率就不能低于最小采样频率,这样就限制了MCU的最低运行速度。

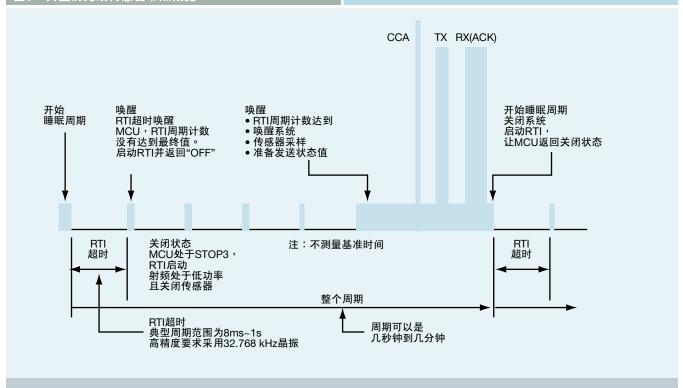

在许多情况下,应用程序会通过尽可能快地执行预定任务,从而使MCU快速回到极低功耗的状态来实现整体功耗最低的目标。例如烟雾探测器,仅需每5秒种唤醒

一次,进行读取、作出决策然后回到休眠状态。这种方法在电池供电的设备中很常见,此类系统在大约99%的时间里都处于休眠状态。

为了实现这种系统, 飞思卡尔结合了快速时钟切换和快速 唤醒程序来帮助应用设计人员实现其功耗目标。

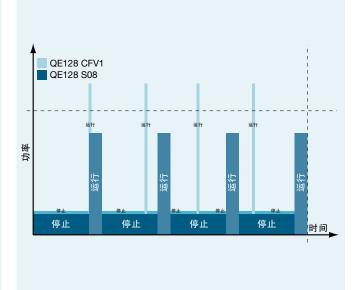

#### 烟雾探测器案例分析

图1和图2分别显示了烟雾探测器的结构框图和功率与时间关系示意图。MCU有一路来自烟雾舱的主要输入,还有两路输出:报警器和发光二极管(LED)。MCU内的实时时钟(RTC)模块可以定期从"停止2"模式(稍后描述)中唤醒设备,以便使运放读取并处理数据,并决定LED和报警器的状态。然后,MCU重新进入"停止2"模式以降低功耗。HCS08在"停止2"模式下的电流略低于ColdFire v1的同等部分,但S08 CPU的内置数据处理功能也较弱。图2对比了两种器件的功率和时间方块图,帮助您选择最适合您的应用需求的解决方案。在任务执行速度最为重要的应用中,MCF51QE128 ColdFire V1器件可能是更好的解决方案。这两种产品间的管脚兼容性意味著从一种策略到另一种策略的迁移可以迅速而轻松地完成,因为它们可以使用相同的电路板、软件和工具。

#### 图1: 烟雾探测器结构简图

# 3.3V至1.8V 报警 MC9S08QE128 或 MCF51QE128 烟雾仓 运放 LED ghb

#### 图2: 烟雾探测器应用功率与时间关系示意图

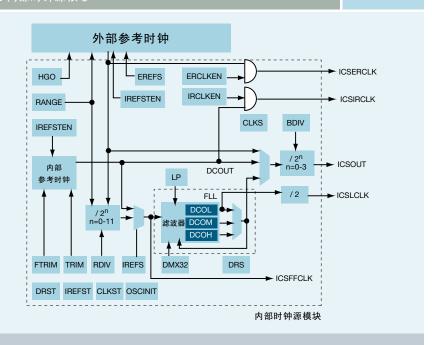

#### 时钟选择

QE128的心脏是图3所示的内部 时钟源模块(ICS)。该模块使设计 人员可以选择从32 kHz至16 MHz的 外部参考时钟(ERCLK)或可调整的 从31.25 kHz至39.06 kHz的内部 参考时钟(IRCLK)。ICS的核心是 锁频环(FLL)模块,它可以将其输入 时钟频率倍频至最高50 MHz。 FLL的输入时钟,也称为FLL参考 时钟,必须在31.25 kHz至39.06 kHz范围内,这样FLL才能正确 运行。使用内部FLL参考时钟时非常 简单,您要做的只是将频率调整到 适当的范围。外部参考时钟的频率 可高达16 MHz,并且可以由参考 分频器(RDIV)分频,它可以设置为 1到1024。如果需要低频总线, 那么FLL可以旁路。第二个分频器 模块,即总线分频器(BDIV)可以对

时钟信号进行1、2、4或8分频,再将其输出到ICSOUT 信号。MCU总线时钟为ICSOUT除以2。

ICS还控制一个独立的1kHz超低功率振荡器(LPO), 它可以供实时时钟(RTC)和看门狗(COP)使用,其使用 符合EN60730的标准。EN60730是针对家庭或类似应用 的自动化电气控制标准。

表1显示了MC9S08QE128上的每个模块可以使用的 时钟源。表中出现的其它时钟有OSCOUT(到外部时钟的 直接通路)和XCLK(进入FLL模块的信号,是内部振荡器或 经过RDIV后的外部时钟源)。

| 表1: 每种模块的可用时钟源    |        |       |       |     |                |  |  |  |  |  |  |  |  |

|-------------------|--------|-------|-------|-----|----------------|--|--|--|--|--|--|--|--|

|                   | ICSOUT | IRCLK | ERCLK | LPO | 其他             |  |  |  |  |  |  |  |  |

| ACMP              | /2     |       |       |     |                |  |  |  |  |  |  |  |  |

| ADC               | /2     |       | •     |     |                |  |  |  |  |  |  |  |  |

| COP               | /2     |       |       | •   |                |  |  |  |  |  |  |  |  |

| CPU               | /1     |       |       |     |                |  |  |  |  |  |  |  |  |

| Flash             | /2     |       |       |     |                |  |  |  |  |  |  |  |  |

| I <sup>2</sup> C1 | /2     |       |       |     |                |  |  |  |  |  |  |  |  |

| I <sup>2</sup> C2 | /2     |       |       |     |                |  |  |  |  |  |  |  |  |

| RTC               |        | •     |       | •   | OSCOUT         |  |  |  |  |  |  |  |  |

| SCI1              | /2     |       |       |     |                |  |  |  |  |  |  |  |  |

| SCI2              | /2     |       |       |     |                |  |  |  |  |  |  |  |  |

| SPI1              | /2     |       |       |     |                |  |  |  |  |  |  |  |  |

| SPI2              | /2     |       |       |     |                |  |  |  |  |  |  |  |  |

| TPM1              | /2     |       |       |     | XCLK或外部<br>时钟源 |  |  |  |  |  |  |  |  |

| TPM2              | /2     |       |       |     | XCLK或外部<br>时钟源 |  |  |  |  |  |  |  |  |

| ТРМ3              | /2     |       |       |     | XCLK或外部<br>时钟源 |  |  |  |  |  |  |  |  |

这款MCU的灵活性的关键是不同模块可以同时使用内部 振荡器和外部振荡器的时钟源。这意味著一些模块可以比 其它模块运行慢一些,从而可降低功耗。

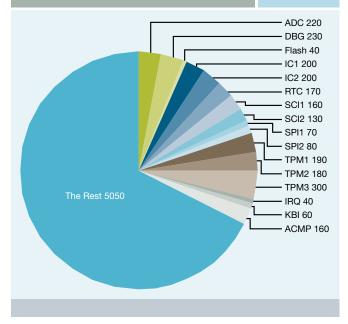

MC9S08QE128的设计中采用了与时钟有关的另一种 节能特性。系统时钟门控寄存器1和2(SCGC1和 SCGC2)使用门电路打开(1)或关闭(0)时钟源,从而控制 各单元的时钟门控电路,如定时器、ADC、IIC、SCI、

图1: 在10MHz总线、在FEE模式,通过时钟 门控节约的uA数

调试模块、闪存、IRQ、键盘中断模块(KIM)、模拟 比较器、RTC和SPI(串行外围设备接口)。通过门电路 关闭未使用模块的时钟,可以在MCU的"运行"和"等待" 模式(后文介绍)下节约宝贵的微安数(uA)。这种特性对于 MC9S08QE128等器件尤其重要,因为它集成了大量的 通信模块和定时器。

仅在需要时打开模块的门电路,在作业完成时关闭门 电路,这是一种重要的节能方法。在写入寄存器后时钟门 将立即开启或关闭。然而,这种方法也有一些弱点需要 考虑。

- 复位后,所有的时钟门都是开启的,因此为了保持低 功耗,时钟门应尽快关闭。

- 对时钟门已关闭模块的寄存器的写操作无效。

- 为了避免错误操作,比较好的做法是在时钟门关闭前 禁用该模块,并在时钟门开启后重新初始化该模块的 寄存器。

图1说明了通过关闭各模块的时钟门可以实现的节能 效果。这些数字仅表现了某个测试环境中的情况, 飞思卡尔半导体不对这些数字的准确性负责。

#### 操作模式一时钟

如上所述,ICS连到了所有消耗功率和器件控制的外围 设备上。这使设计人员能够根据需要去选择功率降低的 程度和性能水平。同样重要的其它因素包括:

- 使用低频率、低增益的外部振荡器比使用内部电路更加 节能

- 通过旁路FLL或PLL(锁相环),由于降低了频率从而可 降低功耗,同时旁路FLL本身也可以降低功耗。

- 在MC9S08QE128 MCU中禁用而不是旁路FLL/PLL 可讲一步降低功耗。

注意,在PLL和FLL之间进行选择时,FLL是功率最低的 选项,尽管它的长期准确性较低。

MC9S08QE128 MCU中的ICS有6种运行模式:FEI(FLL 启用的内部时钟模式),这是缺省模式;FEE(FLL启用的 外部时钟模式);FBI(FLL旁路的内部时钟模式);FBE (FLL旁路的外部时钟模式);FBILP(的功耗FBI模式)和 FBELP(低功耗FBE模式),它们通过ICS控制寄存器2中的 LP位来控制。FBILP和FBELP可以降低振荡器轨道上的 电压摆幅,从而降低整体功耗。

#### 运行模式─CPU

在系统设计的适当阶段选择正确的运行模式可以实现甚至 突破产品功耗目标。最新一代的MCU产品能提供多种模式 选择,每种方式又有不同的优点和缺点,以往的简单选择 "运行"模式还是"低功率"模式的日子已经过去。设计人员 必须选择退出路径、唤醒次数和寄存器保持等等。除了常用 的"运行"模式,MC9S08QE128还有另外5种节能模式。其中 的"等待"、"停止3"和"停止2"等三种模式对于S08内核而言并 不陌生,在其它内核中使用也很常见,只是名称有可能不同。

在"等待"模式下,CPU完全关闭以降低功耗。MCU系统时钟 和整个电压调节功能将保持。根据总线频率的不同,等待模式 可将运行模式电流降低30%~60%,而且任何中断都允许立即 退出等待模式。

"停止"模式暂停系统时钟并使稳压器进入待机状态。 在MC9S08QE128 MCU中,"停止3"模式在两种停止模式中 消耗的能量最高,但好处是能够使唤醒时间缩短到仅仅6微秒 (us)。"停止3"模式有三种版本:

- 启用BDM

- 稳压器工作

- 精简型

与"等待"模式不同,退出"停止3"模式仅限于从RTC、低电压 检测/低电压报警(LVD/LVW)、ADC、带内部参考电压的 模拟比较器(ACMP)、IRQ、SCI、KBI和复位。"停止2"是 MC9S08QE128 MCU中最低功率模式的名称。这种方式下, 内部电路断开电源,但仍维持RAM的内容和引脚状态。 主要的不同之处在于,只有三种方式可以退出这种模式, 即复位、IRQ和RTC,且MCU在退出时产生复位,效果与上 电复位相同。

MC9S08QE128器件中有两种新的节能模式:"低功率运行" (LPR)和"低功率等待"(LPW)。LPR与常规"运行"方式相比 降低功耗的方法是将稳压器置于待机状态。要进入这种 模式,必须运行FBELP模式,即功率最低的ICS模式。必须 禁用低电压保护系统、MCU内部带隙电压以及内置在线 仿真器/后台调试控制器(DBG/BDC)模块,因为无论总线频率 是多少,这三个模块都将消耗大量功率。由于稳压器处于待机 状态,我们建议在此方式下使用所有可能降低功耗的方式。

"低功率等待"(LPW)模式只能从LPR模式进入,因此对LVD 电路、调试和ICS模式的限制是一样的。与LPR相比,MCU 在LPW模式下通常可以将电流消耗量降低50%。

表2对比了不同CPU运行模式的主要特性。

| 表2: CPU运行模式对比表 |            |        |                                                  |                      |  |  |  |  |  |  |  |

|----------------|------------|--------|--------------------------------------------------|----------------------|--|--|--|--|--|--|--|

|                | 典型总线<br>频率 | 典型 ldd | 退出源                                              | 退出<br>时间             |  |  |  |  |  |  |  |

| 运行             | 8 MHz      | 5 mA   | 无                                                | 无                    |  |  |  |  |  |  |  |

| 低功率运行          | 16 kHz     | 25 μΑ  | LP位清零                                            | 无                    |  |  |  |  |  |  |  |

| 等待             | 8 MHz      | 2 mA   | 任何中断                                             | 立即                   |  |  |  |  |  |  |  |

| 低功率等待          | 16 kHz     | 4 μΑ   | 任何中断                                             | 立即                   |  |  |  |  |  |  |  |

| 停止3            | 无          | 450 nA | RTC, LVD/<br>LVW, ADC,<br>ACMP, IRQ,<br>SCI, KBI | 6 µs                 |  |  |  |  |  |  |  |

| 停止 2           | 无          | 370 µA | RTC, IRQ<br>或RESET                               | 6 µs +<br>73总线<br>时钟 |  |  |  |  |  |  |  |

#### 有助于节约功率的其他MCU特性

MC9S08QE128 MCU具有可以在低至1.8V电压下进行重新 编程的闪存,这可以在便携式应用中延长电池使用寿命。 MC9S08QE128器件上的三个端口都具有"置1"、"清零"和 "翻转"功能,这可以加速引脚操作,缩短代码执行时间, 从而可以迅速重新进入低功率模式。器件的所有输出引脚都 具有斜率控制功能,当驱动外部器件时,可以通过减慢瞬变 过程来降低功率并控制驱动强度。

#### 结论

通过仔细考虑模块基础上的时钟源、时钟分布和时钟模式, 以及在恰当的时间和恰当的时间长度使用恰当的CPU模式, 通过我们的MCU可以实现针对现代消费和工业产品的严格功 耗限制。不是只有时钟和CPU模式是可以降低功率或延长电 池寿命的MCU功能,在应用指南AN3460中进一步讨论了其 他一些简单方法,可以从freescale.com上下载。

总之,优化的MCU设计可使系统功耗降低一半。飞思卡尔所 采用的功能都是概念简单且易于使用的。功能的多样性意味 著所有类型的应用,无论是电池还是电源供电的,都可以 从中获益。这些功能很容易理解、合成和使用,为您提供了 一个实实在在的工具,可以有效地处理您的系统中最严格 的功率问题。

S08产品采用SST许可使用的SuperFlash技术。该信息可能会有所变化,决策时应使用最新参考手册。

Inga Harris于2000年毕业于Strathclyde大学,拥有电子学和电子工程专业的荣誉学位。她所从事的飞思卡尔的技术 市场和应用工程工作主要面向消费和工业市场,以8位MCU系列为主。

#### Radomir Kozub, Pavel Laisner

# 用于实时通信的 超低功率无线设计

我们的设计团队被要求开发一个用于演示三轴加速计 (飞思卡尔MMA7260QT)的无线系统。这样做的目的是 为了用无线连接代替最初RD3112MMA7260Q (STAR) 演示板中使用的串行电缆,使用最新的飞思卡尔技术来将 加速计数值从传感器中实时地传输到PC中。

无线演示板的主要特性包括:

- 非常小的尺寸(硬件和软件)

- 低功率

- 电池供电

- 20米的无线覆盖范围

- 印刷线路天线

- 实时响应

- 低成本

- 可用作参考设计

初级评估之后,我们清楚地发现主要的设计挑战是低功率 和低电流消耗。该演示的目的就是为加速计测量值提供 每秒约30次的传输频率。因此在使用有限的电源时每个 微安秒(µAs)都不容忽视。

只知道传感器电路板所用的电池而不知道将采用哪种无线 技术会也是一个难题。起初考虑的是AA和AAA碱性电池。 容许的电流是足够的,然而电池的实际尺寸与项目的其他 部分相比就显得过大。由于该演示的目标之一就是演示 飞思卡尔的极低功率技术,因此最后决定使用"纽扣"型的 锂电池。常见的220 mAh CR2032 3V纽扣电池带有合适 的电池固定架,从外形来看是非常理想,而且可提供充足 的电池寿命来进行成功的演示。为了强调采用低功率电池 作为电源,传感器电路板考虑使用透明罩甚至不使用 盖罩。

#### 找寻合适的无线技术

下一个设计选择是确定最理想的低功率无线技术,将数据 从加速计传输到计算机。最后选择了2.4 GHz工业、科学 和医用(ISM)频段,因为它是全球都接受的,而且能够 充分利用小型电路板和低成本(印刷线路)天线。

3种知名的标准无线通信技术可在2.4 GHz ISM频段内 运行,即Wi-Fi、蓝牙和IEEE 802.15.4技术。Wi-Fi可能 是最有名的,可提供最快的通信速率,而且非常适合 计算机连接的部分。然而它不是为超低功率运行和长期 电池寿命而设计的。蓝牙技术的确更适合低功率、电池 供电的设备,它设计用于为电话、耳机和其他手持消费 设备提供近距离(10m或更少)的中速无线连接。另一 方面, IEEE 802.15.4技术最初就是为小型电池供电的 设备提供数月至数年的低速率近距离(20m至100m)的 无线连接而设计的。它的初衷就是低数据速率(如传感器 和控制网络中),而且超低功耗的表现卓越。由于这些 原因,基于802.15.4的无线传输技术被选择用于无线加速 计演示设计,我们团队将其命名为ZSTAR。

#### 演示方案概述

该演示使用ZSTAR传感器模块和(一般通过USB接口)连接 到PC的802.15.4无线数据收集器模块。飞思卡尔有许多 演示模块可用作数据收集器。ZSTAR演示方案采用的模块 是一个无线传感器电路板,它使用了飞思卡尔的3种主要 器件:

- 三轴加速计MMA7260QT,也称为"Triax"

- 16脚8位微控制器(MCU)MC9S08QG8

- MC13191 802.15.4收发器(无线调制解调器)

所有这些器件都能够支持超低功率运行。为了确保合理 的电池寿命,必须充分利用所有这些器件提供的强大的 低功率运行模式。

#### 表1: 调制解调器、MCU和三轴加速度计各状态下的电流消耗

| 调制解调器运行模式  | 描述                                                    | 典型电流消耗 |

|------------|-------------------------------------------------------|--------|

| 关闭         | 整个器件断电                                                | 0.2 μΑ |

| 休眠         | 保持RAM/寄存器内容·数字IO保持其状态。参考时钟振荡器关闭。                      | 1 μΑ   |

| 半休眠        | 晶振参考时钟开启。保持RAM/寄存器内容,数字IO保持其状态。<br>输出时钟可用。定时器可用于唤醒功能。 | 35 μΑ  |

| 空闲         | 参考时钟振荡器运行。可快速过渡到接收和发送模式。                              | 500 μΑ |

| 接收         | 接收模式或CCA                                              | 37 mA  |

| 发射         | 发射模式                                                  | 30 mA  |

| MCU运行模式    | 描述                                                    | 典型电流消耗 |

| 停止1        | 所有I/O脚自动转换到默认的复位状态。MCU的大部分内部电路断电。<br>RAM内容丢失。         | 475 nA |

| 停止2        | 保持RAM。所有I/O脚控制信号维持原状态。唤醒等同于复位启动。                      | 600 nA |

| 停止3        | 保持所有内部寄存器和RAM内容,保持I/O脚状态。唤醒等同于中断服务。                   | 700 nA |

| 等待         | CPU核心时钟停止,所有启动的外围设备正常运行。                              | 1 mA   |

| 运行         | 所有外围设备关闭,CPU内核时钟为32.768 kHz,源自32.768 kHz<br>晶振。       | 95 μΑ  |

| 运行         | 所有外围设备关闭,CPU内核时钟为约32KHz,源自内部振荡器<br>(无锁频环)。            | 150 μΑ |

| 运行         | 所有外围设备运行,CPU内核时钟开启(8MHz)。                             | 3.5 mA |

| 三轴加速度计运行模式 | 描述                                                    | 典型电流消耗 |

| 睡眠         | 无输出                                                   | 3 μΑ   |

| 运行         | 三轴加速计运行                                               | 500 μΑ |

#### 低功率考量

影响功耗的几个重要因素:

- MCU、Triax和调制解调器的省电模式须在整个通信周期的每个部分进行处理(指将一批加速计数值发送给PC的时间段)

- 每秒发送的数据包的数量(即通信周期的速率)

- 每秒交换的数据包的数量(802.15.4协议对每个数据包进行确认,但是为了降低功耗,传感器每进行8次传输才发送一个确认)

- 数据包长度(协议必须简单而轻便,具有最少的开销和 最小数据长度)

表1总结了可用的器件状态,综合介绍了这些器件可提供的运行模式。

#### 为实现低功率而平衡系统

传感器电路板的运行必须从功耗角度考虑。由于所发送数据包的数量和大小是一致的,没有变化,因此功率的处理必须著眼于工作周期的各个部分。

A. 低功率或通讯之间的安静时间

由于电路板具有MCU时钟模式灵活性,低功率考量可在 精确定时和非精确定时之间的作充分的选择。

- 1. **精确的接收/发送定时(基于晶振)** —发送/接收操作 都可精确定时。此外,接收窗口可以尽可能的窄, 从而节约电流。

- a. MCU带32.768 kHz晶振、调制解调器为关闭模式。 在等待下次通信时,MCU低速运行。在需要高速 运行的时间段,MCU切换至锁频锁环(典型总线时钟

为8 MHz)。该解决方案的缺点是从关闭到空闲模式的 过渡需要10至25ms的时间,用于稳压器和时钟振荡器 的启动。此外,调制解调器RAM的内容与GPIO状态 也会丢失,因此每次必须重复进行所有的配置。 它需要两个晶振(调制解调器为16 MHz, MCU为 32.768 kHz) °

总体功耗: 200 nA (调制解调器) + 9 5 μA (MCU)

b. MCU带32.768 kHz晶振、调制解调器处于休眠模式, 表现于1a) 的情形类似。从休眠到空闲模式的过渡 时间稍短(8至20ms)。该模式的优点是RAM的内容与 GPIO状态可以保持。该模式与前述相同使用两个 晶振。

总体功耗: 1 μA (调制解调器) + 9 5 μA (MCU)

- c. MCU由内部振荡器提供时钟,或由外部提供(通过 调制解调器提供的CLKO输出),调制解调器处于 半休眠模式。若MCU提供内部振荡器,当命令MCU 退出半休眠模式时,它可以快速响应。MCU复位并 配置调制解调器。调制解调器在休眠模式下也可以 提供参考时钟。MCU将CLKO编程至所需频率并等待 CLKO稳定。CLKO稳定后,MCU将时钟切换到外部 时钟源。调制解调器中长时间延时的精确定时是由 周期性地从半休眠模式中退出的时间来完成的,而此时 MCU处于睡眠状态。在这种结构中,设计人员可充分 利用自动启动的定时器触发事件,如:

- 激活接收模式

- 激活发射模式

- 激活空闲模式

此外,接收帧在接收期间会进行"时间标记",从而可以 在各种不同事件间精确定时。微控制器可一直处于低 功率模式。与MCU使用独立晶振的方法相比,这种 情况下的功耗稍高,但它只需要一个晶振(调制解调器 晶振)。

#### 2. 非精确数据包定时

a. MCU定时由内部振荡器(RTI)控制,调制解调器处于 关闭模式。这种情形的缺点是通信定时不是那么精确。 MCU定时由不能提供精确定时的RTI内部振荡器控制 (仅30%的精度)。因此接收窗口必须更宽,从而对功耗 产生负面影响。只需一个晶振。

总体功耗: 200 nA (调制解调器) + ~1 μA (MCU睡眠 模式 + RTI开启)

b. MCU定时由内部振荡器(RTI)控制,调制解调器处于 休眠模式。这种情形与a相似。不同的是到空闲模式的 过渡时间更短,并且不需要重新初始化调制解调器。

总体功耗: 1 μA (调制解调器) + 1 μA (MCU睡眠 模式 + RTI开启)

c. MCU由内部振荡器提供时钟,以最低频率运行(4kHz), 调制解调器处于关闭模式。

MCU总线时钟由内部参考时钟驱动。具有2%的精度 (调整之后),足以满足许多应用的需求。调制解调器为 关闭模式,只需要一个晶振。

总体功耗: 200 nA (调制解调器) + 150 μA (MCU以 4 kHz内部时钟运行)

d. MCU由内部振荡器提供时钟,以最低频率运行(4kHz), 调制解调器处于休眠模式。该情形与c相似;调制 解调器处于睡眠模式。

总体功耗: 1 μA (调制解调器) + 150 μA (MCU以 4 kHz内部时钟运行)

| 表2 |                  |         |             |        |

|----|------------------|---------|-------------|--------|

| 模式 | MCU时钟            | 精确性     | 调制解调<br>器模式 | 消耗     |

| 1a | Xtal<br>32768 Hz | 100 ppm | 关闭          | 95 μΑ  |

| 1b | Xtal<br>32768 Hz | 100 ppm | 休眠          | 96 μΑ  |

| 1c | 调制解调器<br>的时钟     | 20 ppm  | 半休眠         | 36 μΑ  |

| 2a | RTI 时钟           | 30%     | 关闭          | 1.2 µA |

| 2b | RTI 时钟           | 30%     | 休眠          | 2 μΑ   |

| 2c | 内部时钟<br>4 kHz    | 2%      | 关闭          | 150 μΑ |

| 2d | 内部时钟<br>4 kHz    | 2%      | 休眠          | 151 μΑ |

现在让我们看看总体功耗的另一部分。

#### B. 发送和接收事件

正如调制解调器发送/接收操作模式的电源电流所示, 调制解调器的发送和接收状态对功耗也有很大的影响。 因此,数据包的长度需要进行高度优化,而且必须仔细 选择通信速率。

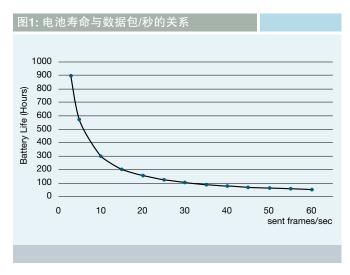

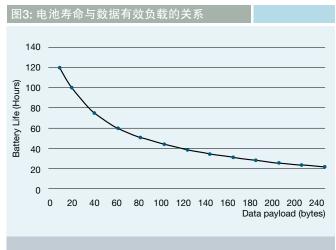

在下面的几张图中,您可以看到通信速率和数据有效 负载长度对电池寿命的影响。图1显示了电池寿命小时 数与每秒发送的帧数的关系。我们必须将速率折衷为 每秒30个包,以得到足够的采样速率和合理的电池 寿命。

数据包的长度对电池寿命也有很大影响。这就是我们为什么只 发送三轴加速计的原始数据的原因(请参考《ZSTARRM参考 手册》第5.3章中的数据包格式及长度,以了解更多详情。)

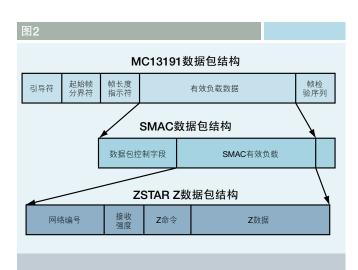

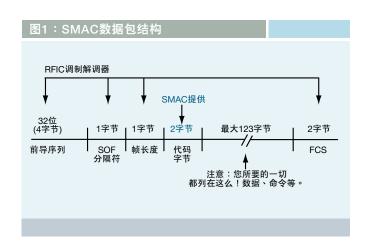

符合IEEE 802.15.4的标准数据包有4个字节的引导符、 1个字节的STD(起始帧分界符)、1个字节的FLI(帧长度 指示)、2字节的FCS(帧检验序列)以及有效负载数据(最多 125字节)。因此,帧开销为8字节或8 x 32 = 256 μs, 最长的有效负载发送时间为 $125 \times 32 = 4000 \text{ us}$ 。那么 数据包发送时间为:

总发送时间 (μs) = 256 + (有效字节 x 32)

我们传感器电路板的标准SMAC数据包有17字节(包括 2字节的IEEE 802.15.4控制字段包)。还有两个分别需要 144 μs和10 μs的所谓"预热"(从空闲到发送过渡)和 "冷却"(发射到空闲过渡)时期。

下图显示了数据包长度和电池寿命的关系。很明显,数据 包长度应尽可能小。

这个图也只是理论上的,因为实际上还有另一个物理限制。 电源(锂电池)只能提供非常有限的持续电流,因此如果 传输较长的帧,电池电压将明显下降。在ZSTAR的设计中, 使用了一个大容量钽电容器(470 µF)来改善电源对接收或 发送引起的电流峰值的响应。即使如此,较长的数据帧 (大于约50-100字节)还是会导致电压大幅下降。

电容计算:我们规定发射期间(1 ms)容许的电压下降为 100 mV °

$$\Delta u = \frac{1}{C} * i * \Delta t$$

$$C_{min} = i \frac{\Delta t}{\Delta u} = 30 \text{ mA} * \frac{1 \text{ ms}}{100 \text{ mV}} = 300 \text{ } \mu\text{F}$$

最后,我们从相同封装系列中选择了470 uF电容器。

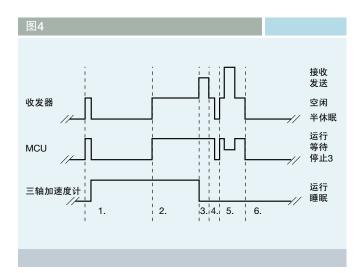

#### 如何协同运行

传感器电路板卡设计得非常小巧而且具有高性价比,因此 我们在调制解调器中只使用一个晶振。同时,我们需要 精确的通信定时,所以用调制解调器休眠模式进行通信 定时,而MCU使用内部时钟(在工作期间),否则MCU就 处于停止3模式。传感器电路板与USB接收头之间的通讯 如下所述。

- 一个数据包的发送过程

- 1. 该阶段开始时,调制解调器从停止3模式中唤醒 MCU。MCU将Triax从睡眠模式下唤醒(控制Triax的 SLEEP脚)。然后Triax的输出必须稳定,然后再进行 测量。在这段时间内,调制解调器再次进入定时的 半休眠模式,同时MCU也进入停止3模式。

- 2. 当Triax准备好进行测量时,调制解调器再次唤醒 MCU,然后MCU测量Triax。MCU获得数据后Triax 切换回睡眠模式,数据包形成并放入调制解调器的 RAM缓冲器中。

- 3. 调制解调器通过射频发送数据包。

- 4. 为了检测连接错误(传感器电路板和USB接收头 之间),必须等待USB接收头的响应。然而,因为 USB接收头需要一定的时间来处理接收到的数据并形成

- 响应数据包,所以MCU再次将调制解调器设置为短 时间的半休眠模式。

- 5. 这段短时间过后,MCU醒来并在规定的接收窗口内 接收USB接收头的响应。然后,调制解调器被设置为 半休眠模式,直到一个周期结束,同时MCU进入停止 3模式。

- 6. 在两个连续数据包之间,MCU一直处于停止3模式, Triax切换到睡眠模式,调制解调器处于休眠模式。 同时,其时基会测量到收到下一数据包的时间。

在评估该通讯方式的过程中我们发现,每次发送后的接收 会大幅增加电流消耗。由于这不是要求实现的或必需的, 因此USB接收头的响应接收窗口只是每8次才打开一次。 在其他情况下,发送结束之后传感器电路板立即进入休眠 模式(跳过状态4和5)。

#### 总结

我们对ZSTAR项目的最初目的(使用有限的电源传输实时 数据)进行了评估。系统设计的各个方面(硬件架构和 软件实施两方面)被经过研究和优化以实现最佳的应用 性能。三轴加速计的XYZ采样值,加上内部温度与电池 电压水平值,使用微型钾CR2032电池每秒发送30次, 可达到100小时的运行时间。系统的平均电流消耗估计为 2.5 mA, 实际测量也证实了这种预期。

总之,ZSTAR的设计表现了一个采用MC1319x 调制解调器系列和高性价比的少管脚8位微控制器 (MC9S08QG系列)实现的高性价比方案,用于3轴 加速度计(MMA7260QT)的无线感测。

Radomir Kozub是飞思卡尔的应用工程师,在公司任职已近4年。他拥有电气工程专业硕士学位。加盟飞思卡尔 之前,Kozub致力于开发各种测量应用。

Pavel Lajsner是飞思卡尔的应用工程师,在公司任职已超过11年。他拥有电气工程专业硕士学位。

# JTAG TAP的高效控制

# JTAG TAP转换变得更轻松

#### 介绍

飞思卡尔的许多微处理器都带有JTAG端口 — 一种兼容 IEEE1149.1标准、用于执行边界扫描和调试嵌入式应用 程序的端口。早在20世纪80年代中期, Joint Test Action Group (JTAG)就开始著手IEEE 1149.1标准的制定,后来 IEEE接手了这项任务。因此,符合IEEE 1149.1标准的 测试接入端口就按最初发起标准化的这个机构命名,通常 被称作JTAG端口。

现在,JTAG端口主要用于边界扫描、编程和调试目的。 所有符合IEEE 1149.1标准的JTAG具体实现并不只限于 提供该标准规定的功能,其功能可以自由扩展。例如 IEEE-ISTO 5001论坛™标准在定义嵌入式处理器调试接口 时就以JTAG为基础。

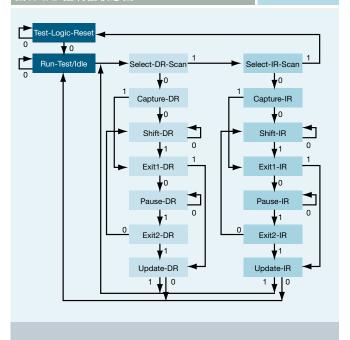

IEEE 1149.1标准把通用测试接入端口(TAP)定义为访问 JTAG功能的物理层。此外,该标准还定义了TAP控制器。 该控制器负责控制用于访问JTAG功能及其他可能包含的 电路(如调试模块)的信号。TAP控制器是一种同步有限状 态机(FSM),可以响应TAP引脚的变化。为了访问特定的 JTAG功能,您必须使TAP控制器在各状态间变化。如需 了解有关各个TAP控制器各状态的作用及其他JTAG技术 规范的详细信息,请参见IEEE 1149.1标准。

本文介绍了一种简单而高效地沿著最短路径将TAP控制器 从当前TAP状态跳转到其他状态的算法。编程人员一般是 通过编写一系列操作TAP输入引脚的指令来跳转TAP 控制器的状态。因此,为所有软件模块编写跳转代码, 同时还要协调JTAG和其他相关功能,极易变成一件 棘手、乏味而且容易出错的任务。我们的算法采用一个 例子程序将TAP控制器引导到希望的状态,从而免除了 一系列的TAP控制指令。因此,您只需要调用该程序, 如GoTo(dstate)程序,TAP控制器就能跳变到希望的状态 dstate o

#### 跳变算法

在TAP控制器状态机中(如图1所示),如果由TAP的TMS 引脚上的逻辑信号电平(O或1)进行使能控制,并且TAP 处于转换的初始状态,那么在时钟(引脚TCK)的上升沿之 后就会产生一次转换。图1中的箭头0和1代表使能控制 信号的逻辑电平。

图1所示的框图可以看作是由顶点和有方向的边沿组成的 图表,其中顶点为TAP控制器的状态,有方向的边沿为 转换。寻找任何两个顶点之间的最短路径是一个经典的 已解问题。在TAP状态机中,最短路径很明显,可以手动 找到。因此,我们需要一个高效的机制来保存最短路径, 这样以后就可以照做而不需再次寻找了。

为保存最短路径,我们可以利用以下推论。假设状态s,到 状态s。之间有一条最短路径,并且该路径经过状态sk。 这样该路径为s,,...,s,,...s,。那么,路径s,,...s,就是状态 s<sub>k</sub>和s<sub>a</sub>之间的最短路径。如果该路径不是最短路径,那么

#### 图1: TAP控制器状态图

我们就可以缩短s、和s、之间的路径,这样最 初那条路径就不是最短路径,这就产生了 矛盾。

因此,对于任意从s,到s,之间的最短路径, 只保存路径上紧跟著s,状态之后的下一个状 态就足够了。存储各最短路径的下一个状态 的信息库被称作路由表,类似于网络中对路 由信息的定义。在网络中,每个节点都保存 下一个相邻节点的向量,与此不同,我们 的路由表是一个矩阵,因为状态转移是由 TAP接口控制的。TAP路由表如表1所示。

通过最短路径将TAP控制器转移到希望状态 的算法非常简单。假设当前的TAP状态保存 在变量tap\_state中,而二维矩阵Routing-Table保存表1的内容。GoTo(dstate)函数的 运行如下所示:

```

GoTo(dstate)

Update-IR

{

while(tapstate != dstate)

step(RoutingTable[tapstate][dstate]);

return;

}

step(tms)

将 TMS引脚设置为tms (通常在并行端口上);

在TCK引脚上生成时钟脉冲;

tap state = next state(tap state,tms); //

更新当前状态

}

next_state(tap_state,tms)函数使用另一个表

```

#### 实现

我们使用C++实现上面介绍的算法。一个称为JTAG的 Singleton类控制TAP控制器的信号,保存当前状态并 将TAP控制器转移到希望的状态。当这些类启动时,路 由表及其他表格被载入内存,TAP控制器复位到testlogic-reset初始状态。JTAG Singleton接口提供一种叫 作AssertTAPState(tapstate)的功能来确保当前的TAP控

格,它给出每个给定的TMS引脚值的状态的下一个状态。

| 表1: TAP路由表       |                  |               |                |            |          |          |          |          |           |                |            |          |          |          |          |           |

|------------------|------------------|---------------|----------------|------------|----------|----------|----------|----------|-----------|----------------|------------|----------|----------|----------|----------|-----------|

| 状态               | Test-logic-reset | Run-test/idle | Select-DR-scan | Capture-DR | Shift-DR | Exit1-DR | Pause-DR | Exit2-DR | Update-DR | Select-IR-scan | Capture-IR | Shift-IR | Exit1-IR | Pause-IR | Exit2-IR | Update-IR |

| Test-logic-reset | 1                | 0             | 0              | 0          | 0        | 0        | 0        | 0        | 0         | 0              | 0          | 0        | 0        | 0        | 0        | 0         |

| Run-test/idle    | 1                | 0             | 1              | 1          | 1        | 1        | 1        | 1        | 1         | 1              | 1          | 1        | 1        | 1        | 1        | 1         |

| Select-DR-scan   | 1                | 1             | х              | 0          | 0        | 0        | 0        | 0        | 0         | 1              | 1          | 1        | 1        | 1        | 1        | 1         |

| Capture-DR       | 1                | 1             | 1              | х          | 0        | 1        | 1        | 1        | 1         | 1              | 1          | 1        | 1        | 1        | 1        | 1         |

| Shift-DR         | 1                | 1             | 1              | 1          | 0        | 1        | 1        | 1        | 1         | 1              | 1          | 1        | 1        | 1        | 1        | 1         |

| Exit1-DR         | 1                | 1             | 1              | 1          | 0        | х        | 0        | 0        | 1         | 1              | 1          | 1        | 1        | 1        | 1        | 1         |

| Pause-DR         | 1                | 1             | 1              | 1          | 1        | 1        | 0        | 1        | 1         | 1              | 1          | 1        | 1        | 1        | 1        | 1         |

| Exit2-DR         | 1                | 1             | 1              | 1          | 0        | 0        | 0        | х        | 1         | 1              | 1          | 1        | 1        | 1        | 1        | 1         |

| Update-DR        | 1                | 0             | 1              | 1          | 1        | 1        | 1        | 1        | х         | 1              | 1          | 1        | 1        | 1        | 1        | 1         |

| Select-IR-scan   | 1                | 1             | 1              | 1          | 1        | 1        | 1        | 1        | 1         | х              | 0          | 0        | 0        | 0        | 0        | 0         |

| Capture-IR       | 1                | 1             | 1              | 1          | 1        | 1        | 1        | 1        | 1         | 1              | х          | 0        | 1        | 1        | 1        | 1         |

| Shift-IR         | 1                | 1             | 1              | 1          | 1        | 1        | 1        | 1        | 1         | 1              | 1          | 0        | 1        | 1        | 1        | 1         |

| Exit1-IR         | 1                | 1             | 1              | 1          | 1        | 1        | 1        | 1        | 1         | 1              | 1          | 0        | х        | 0        | 0        | 1         |

| Pause-IR         | 1                | 1             | 1              | 1          | 1        | 1        | 1        | 1        | 1         | 1              | 1          | 1        | 1        | 0        | 1        | 1         |

| Exit2-IR         | 1                | 1             | 1              | 1          | 1        | 1        | 1        | 1        | 1         | 1              | 1          | 0        | 0        | 0        | х        | 1         |

制器状态为tapstate。如果当前状态不一样,该功能会将 TAP控制器转换到正确的状态。

JTAG Singleton通过操纵连接到嵌入式处理器上的 JTAG物理接口的并口引脚来转变TAP控制器状态。通过并 口控制JTAG引脚的方法由另一个称为JTAGPort的Singleton实现,它只能由JTAG访问。

#### 结论

我们介绍了可以用一个很小的路由表来保存任意两个 TAP控制器状态间的最短路径,以此方法可以省去编写冗 长乏味的一系列转变TAP控制器状态的指令。考虑到当 前计算机的速度和能够在并行端口上实现的最大频率(约 1MHz),调用函数或功能以及查看TMS引脚值产生的相关 开销可以忽略不计。此外,JTAG端口通讯速度受处理器时 钟频率的限制。

David Baca是飞思卡尔的应用程序工程师,在飞思卡尔工作近两年。他拥有电气工程和工商管理专业硕士学位, 目前正在攻读人工智能博士学位。在加盟飞思卡尔之前,Baca曾参与过NASA和美国空军等机构赞助的研发项目。

# 利用ColdFire® MCF5223x嵌入式控制器

# 加速创新

#### 介绍

在当今这个迅速发展的世界里,节省时间以及让我们 生活的各部分都处于控制之中的要求变得日益重要。技术 在影响世界的变化方式方面继续发挥著重要的作用。 在家中,几乎每一个设备都内置某种技术,而这种技术 本身还在不断创新。连接就是一个很好的例子,说明技术 总是在不断变化,提供新的解决方案来使我们的生活变得 更轻松、更快捷和更高效。

#### 设计挑战

以太网为人类打开了一个充满无限可能的新世界。它使 我们可以从全球任何地方接入全球网络,让我们能够 随时著手进行日常活动和家务。借助以太网连接,人们在 办公室就可以通过计算机远程控制家里的温度或照明。

随著低成本具有以太网功能器件的面世,房屋和楼宇的 自动化功能现在也已开发。高端家电,诸如与以太网连接 的冰箱、报警系统、摄像头、门窗锁、灌溉系统和空调 系统等,只是一部分说明该技术如何使生活更轻松的 实例。

飞思卡尔半导体致力干使生活变得更轻松、更安全, 这正是我们推出大量新型低端32位ColdFire设备来实现 家用电器、工业流程和安全系统的远程控制的原因。 飞思卡尔让开发工程师可以灵活地从一系列不同的 ColdFire嵌入式控制器产品中选择合适的32位微控制器。

#### 飞思卡尔解决方案

以太网控制可用于许多应用,如家用电器和工业控制。 它们都采用以太网作为主要的通信协议,同时使用一个 能实现应用程序和连接任务的控制器。飞思卡尔提供的 新型低成本ColdFire MCF5223x系列器件非常适合这类 控制和连接需求。

#### MCF5223x概述

ColdFire MCF5223x系列建立在过去曾广泛应用的 68 KB系列的基础上,是新型低端ColdFire器件中的 一种。为了确保安全的连接,MCF5223x系列ColdFire 器件是一种单芯片解决方案,提供具有以太网接口的32位 控制。它包含有10/100快速以太网控制器(FEC)、以太网 物理层(EPHY)、CAN 2.0B和加密加速单元(CAU), 它采用Version 2 ColdFire内核进行安全硬件加密, 从而以合理的成本提供出众的性能(60MHz时可达57个 Dhrystone 2.1 MIPS)。MCF5223x嵌入式控制器可为 设计人员提供一系列合适的外围设备和内存空间(高达32 KB的SRAM和高达256 KB的闪存:10万次擦/写周期, 10年数据保持),适合作为紧凑型的具有以太网功能的 平台,可减少开发时间和成本,帮助您的产品更快上市。

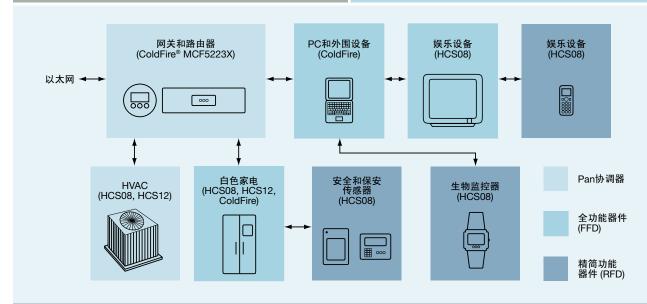

#### 图2: 典型的ZigBee®网络

MCF5223x系列集成了标准的ColdFire外围设备,包括 三个用于中远程连接的通用异步接收器/发送器(UART)、 一个集成电路互连(I2C)和一个队列式串行外设接口 (QSPI),用于所连外围设备的系统内通信。

在数字控制方面,MCF5223x系列提供以下外围设备: 4个带有DMA功能的32位定时器通道、4通道/16位或 8通道/8位PWM发生器、2个用于报警和倒计时的周期 中断定时器(PIT)、4通道DMA控制器、8通道12位ADC, 多达73个通用I/O以及系统集成模块(如PLL和COP)。

这些器件为现有的8位和16位用户拓宽了移植桥梁,如果 这些用户需要具有32位性能、快速以太网功能和高级工具 支持的低成本入门级32位解决方案。飞思卡尔通向高端 32位运行和连接功能的ColdFire路线图可以帮助客户轻松 而快捷地移植其应用程序。

#### ColdFire MCF5223x作为ZigBee®系统的主机

想像一下,如果您能从PC上控制家中的照明、传感器 或门锁该有多好。其实这类网络控制没有听起来那么 复杂-只需要无线通信和连接到以太网的网关就可以 实现。飞思卡尔同时提供无线解决方案和控制器解决 方案。M13192器件是在2.4 GHz频段上运行的收发器, 误包率(PER)为1%时的接收灵敏度为-92 dBm,电源为 2.0-3.6V(采用片上稳压器),逻辑接口1.7-3.3,使用 一块锂电或两块碱性电池,带有完整的RF收发器数据 调制解调器 — 天线输入,全数据包输出,通过最低频率 为4MHz的标准SPI实现数据和控制接口。MC13192还 带有802.15.4的MAC。

收发器可通过SPI轻松连接到MCU上。收发器可连接到 锁扣传感器上、灯光断路器上或任何希望被监控或控制的 设备上。这些设备应当带有标签,而且作为设备与连接到 MCF5223x控制器的中心收发器进行通讯。MCF5223x 设备可以连到Web,可以对每个设备进行监控,甚至在 需要时还可以采取行动(使用InterNiche的免费协议栈)。 图2显示了一个典型的家庭ZigBee网络。

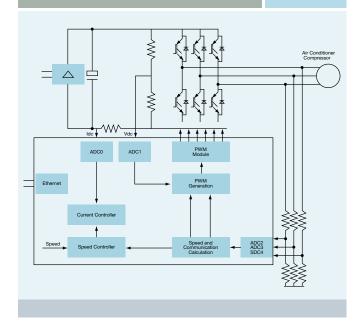

#### 图3: 具有以太网功能的空调控制器

#### ColdFire MCF5223x用作网关进行监控和诊断

监控某个工业线路并将结果自动显示到内部网络上也是 一项常见任务。实时监控系统可以提高时效,系统化地将 数据库中的信息写入系统中而无需人工干预。这样就可以 在生产线内进行远程过程控制,如果遇到问题,技术支持 团队就可以决定采取哪些纠正动作。

#### ColdFire MCF5223x用于空调控制和监控

不管是对干家用电器还是工业应用,空调的控制和监控都 是一个关系到舒适度和生产力的问题。MCF5223x是一种 理想的器件。空调通常由专用于电机控制应用的DSP或 DSC进行控制,而MCF5223x除了可以完成这些器件 的控制功能外,还添加了远程监控的以太网连接功能。 MCF5223x具有PWM模块、定时器和一个12位ADC, 这些正是调节电机控制速度和扭矩的合适的外围设备。 它还包括以太网控制功能和物理层,另外还有协议栈可对 此器件提供诊断、监控和远程控制等全部功能。

#### 结论

在工业、商业甚至消费市场上连接32位控制的应用正在 变成一项必然需求,而不只是可有可无的选项。飞思卡尔 ColdFire MCF5223x系列可以提供一种单芯片解决方案, 通过以太网接口实现32位控制,从而有助于确保安全的 连接。这些高性价比的嵌入式控制器可提供合适的外围 设备和内存空间,帮助构建紧凑的以太网平台来缩减开发 时间和成本,帮助您的产品更快上市。

Lech Olmedo是飞思卡尔RTAC的市场部应用程序工程师。他为ColdFire系列产品提供支持并参与ColdFire和Linux (uClinux)应用程序的连接解决方案开发。他参与的其他项目包括8到16位汽车应用移植等。

Daniel Torres是飞思卡尔半导体的应用工程师。他在数字信号控制器、ColdFire处理器和8位MCU领域具有丰富 经验。他主要从事电机控制和电源管理领域的工作。

#### David Baca

## DSP56800E中的高速32位除法

### 最小化不复原除法算法

#### 介绍

处理器内核DSP56800E包含多个32位寄存器。执行32位整数除法看起来应当是件简单的任务,但是,如果您不是二进制除法的专家,您可能需要更多支持。DSP56800E使用一种叫作DIV的指令来执行除法运算。该指令代表对除数结果进行1位的迭代除运算。该指令以及16位除法算法的描述可以参见DSP56800E参考手册。

DIV采用32位的被除数和16位的除数,在16次迭代后 生成16位的商和16位的余数。迭代运算使用2个32位 的操作数,其中16位除数位于操作数的高16位。这种 用来计算商和余数的算法称作"不复原除法算法"(NrDA)。

如果我们要将NrDA用于32位除法,我们就需要64位的操作数。在一个DSP56800E这样的16位处理器上用64位操作数实现NrDA是很麻烦的,因为它需要对64位算法的支持。还有一种选择是采用著名的牛顿一拉普森迭代法,这种方法只需要32位算法。但这种方法采用除法,因此需要大量的反复才能得到所需的精度。此外,我们不能确保所有的运算对(被除数和除数)都能得到正确的运算结果,除非对几乎所有可能的输入对都进行过测试。

最小化不复原除法算法(MNrDA)可以用32位运算中高效低实现32位不复原算法。由于DSP56800E中的DIV指令也采用32位数字作为除数,所以我们能高效地实现NrDA算法。

#### 本文将介绍以下内容:

- 介绍基本的复原除法算法

- 说明源自恢复算法的不复原除法

- 介绍如何消除NrDA中不必要的迭代,以实现最小版本的NrDA

- 给出处理器内核DSP56800E实现最小化不复原除法的 实例

#### 不复原除法算法

整数除法符号

整除可以定义如下:

$$N = Q \cdot D + R$$

其中,

- N表示分子(被除数)

- D表示分母(除数)

- Q表示商

- R表示余数

为了方便,我们假定 $N \cdot D \cdot Q$ 都是正数。根据定义R是正数,且 $0 \le R < D$ 。此外,每个操作数都可以拆解成单独的位,形如 $Q = \sum_{i=1}^{m-1} Q_i \cdot 2^i$ 。

#### 复原除法算法

不复原除法算法(NrDA)源自复原除法。复原算法从分子中连续减去分母得到余数,直到余数进入相应的范围。 现在,我们可以得到M位整数复原除法的算法。

余数计算的代数等式为:

$$R = N - (D \cdot Q)$$

我们将Q拆分为位

$$R = N - D \cdot \sum_{j=0}^{m-1} Q_j \cdot 2^j$$

$$= N - D \cdot \sum_{j=0}^{m-1} Q_j \cdot D \cdot 2^j$$

这可以看作从N中减去 $D \cdot 2^{j}$ ,对于所有 $Q_{j} = 1$ 。在这个减法运算中,只有当余数仍为正数 $(Q_{j} = 1)$ 时才能成立。所以,我们可以将复原算法公式表示如下。我们设:

R(m) = N其中m代表整数大小(用位表示), 如16位和32位。

然后我们计算R(i)和Qi,这时 $i = m - 1 \dots 0$ 。如下 所示:

计算出R(0)后,R(0)就是实际余数,Q包含得出的商。

为了执行复原算法,我们需要临时变量Z,而且我们必须 在减法得出负值的那一步复原余数。这是因为我们在同一 步内计算 $Q_i$ 和R(j)的值。不复原算法就不是这样了,因为 它从Q<sub>i+1</sub>计算R(j)。

#### 不复原除法算法

在不复原除法算法中,我们将负数结果用于下一次迭代。 为了用公式表示这个算法,我们首先从复原算法入手。 假设我们在第k步得到一个负余数。

$$R(k) = R(k+1) - D \cdot 2^k$$

显然 $\mathbf{Q}_{\iota} = \mathbf{0}$ ,因此在下一步我们应当计算:

$$R(k-1) = R(k+1) - D \cdot 2^{k-1}$$

由于 $Q_{\iota} = 0$ ,所以我们采用R(k)的结果,用加法表示为

$$R(k-1) = R(k) + D \cdot 2^{k-1}$$

$$= R(k+1) - D \cdot (2^{k} - 2^{k-1})$$

$$= R(k+1) - D \cdot 2^{k-1}$$

因此,我们在不复原算法中用公式表示这个迭代,如下 所示:

我们将上面的两个等式组合起来将迭代步骤的代数式 表达为:

$$R(j) = R(j + 1) + (1 - 2 \cdot Q_{i+1}) \cdot D \cdot 2^{j}$$

开始算法时,我们首先假设R(m) = N, $Q^m = 1$ . 在完成m-1迭代后,我们得到R(0)。

$$R(0) = N - (2^{m-1} - \sum_{j=0}^{m-1} (1 - 2 \cdot Q_{j+1}) \cdot 2^{j}) \cdot D$$

$$R(0) = N - (2^{0} - \sum_{j=0}^{m-1} Q_{j} \cdot 2^{j}) \cdot D$$

显然, R(0)不是正确的实际余数。因此, 在算法结束时, 我们需要通过另一次计算来获得余数。

$$R = R(0) + (1 - Q_0) \cdot D$$

最后,我们可以将不恢复算法概括如下:

不复原算法要求转换Dm-1次。特别是32位除法,D必须 左移31位。因此,执行不复原算法需要64位算法。总之, m位除法需要(2\*m)位算法来执行不复原算法。

#### 最小不复原除法算法

最小不复原除法算法(MNrDA)可以用m位运算执行m位数的 不复原算法。

**命题1** ,如果 $n \cdot d$ 和q分别是 $N \cdot D$ 和Q的最高有效位的数 值,那么n-d ≥ q

命题1证明:对于m位整数,我们有:

$$\begin{split} \sum_{j=0}^{m-1} N_j \cdot 2^j &= \sum_{j=0}^{m-1} D_j \cdot 2^j \cdot \sum_{j=0}^{m-1} Q_j \cdot 2^j + R \\ 2^m + \sum_{j=0}^{n-1} N_j \cdot 2^j &= (2^d + \sum_{j=0}^{d-1} D_j \cdot 2^j) \cdot (2^q + \sum_{j=0}^{q-1} Q_j \cdot 2^j) + R \end{split}$$

$N = Q \cdot D + R$

马上就可得到n-d ≥ q

推论1 在整数除法中,以N为分子,D为分母。n和d分别 作为N和D的最高有效位的数值。那么对于所有的i > n - d.  $Q_i = 0$  °

#### 推论1证明:这个推论是命题1的直接结果

如果我们将推论1应用到不复原除法算法中,我们可以 直接跳到R(n-d)的运算,因为前面的迭代得出商位为0。

$$R(n - d) = N - D \cdot 2^{m-1} + \sum_{j=n-d}^{m-2} D \cdot 2^{j}$$

$$= N - D \cdot 2^{n-d}$$

$$= N - 2^{n-d} \cdot (2^{d} + \sum_{j=0}^{m-2} D_{j} \cdot 2^{j})$$

$$= N - (2^{n} + \sum_{j=0}^{d-1} D_{j} \cdot 2^{j+n-d})$$

由于第一次计算得出的部分分数是R(n-d),我们只需要 对D转换n-d次,就能有效地将D的最高有效位移动到位置 n。由于m-1 ≥ n,我们只需要m位来存储转换后的D。

即使在最坏的情况下(n = m - 1, d = 0), MNrDA也没有减 少迭代数量。既然定时分析通常基于最坏案例执行次数, 我们只需假设n = m - 1即可。因此,MNrDA的执行过程 如下:

- 1. 计算**D**的前导零: I<sub>a</sub>

- 2. 将D左移I。位

- 3. 执行不复原除法算法,从 $R(I_a)$ 开始,假设 $Q_i = 0$ ,  $j = I_0 + 1 \dots m - 1$

#### 在DSP56800E采用MNrDA实现带有符号数除法

DSP56800E上的DIV指令代表16位复原除法迭代。这个 指令采用32位被除数和16位除数。除数会被左移16位, 在每次迭代中的除数右移,而不是将被除数左移。Q位 结果在每次迭代中都会移入。因此,在执行16次迭代后, 余数R(0)包含在被除数的高16位中。在代数上可以表示 如下。一个迭代步骤为:

$$R' = 2 \cdot R' (j + 1) \pm D \cdot 2^{n}$$

$$= 2^{n-j} \cdot R (j + 1) \pm D \cdot 2^{n}$$

$$= 2^{n-j} \cdot (R (j + 1) \pm D \cdot 2^{n})$$

$$= 2^{n-j} \cdot R (j)$$

最后得出:

$$R'(0) = 2^n \cdot R(0)$$

在我们的例子中,n = 16,因此R(0)包含在高16位中。 商占据了低16位。

为了执行完全的32位除法,我们给DIV指令提供32位的 除数并左移n - d位,这里n和d分别是被除数和除数的 最高有效位。

$$R'(n-d) = R (n-d)$$

$$= N - D \cdot 2^{n-d}$$

$$R'(n-d-1) = 2 \cdot R (n-d) - D \cdot 2^{n-d}$$

$$= 2 \cdot (R (n-d) - D \cdot 2^{n-d-1})$$

$$= 2 \cdot R (n-d-1)$$

$$\vdots$$

$$R'(n-d-j) = 2^{j} \cdot R (n-d-j)$$

$$\vdots$$

$$R'(0) = 2^{n-d} \cdot R (0)$$

基于这个原因,R(0)包含在高m-1-(n-d)位中,商包 含在低 n - d位中。如果我们假设n = m - 1,那么R(0)位 于高d位中,其LSB在第(n-d)位上。为了得到商,我们 对DIV的目的操作中进行掩码操作。在我们的例子中,m = 31, 而且我们假设实际的除法中被除数和除数都是正 数。我们采用MNrDA实现四象限除法以得到商。由于从 MNrDA中得到余数的复杂度几乎等同于乘以商,再从被除 数中减去,所以我们就不计算余数了。这种算法最差情况 下的执行时间为60个循环。

; A = 有符号的被除数 (分子)

; B = 有符号的除数 (分母)

; A1:A0 / B1:B0

;程序使以下寄存器:A,B,D,X0,Y

tfr B.Y ; Y=den

; 商符号

; B的MSB保留符号位 eor.I A,B

;准备R(q)和den

abs A ; abs (num)

abs Y ; abs (den), 因此我们能够计算R(q)

; DIV接收负数的S, 但是对于

; R(q)计算,我们对减法进行硬编码

: 移动后的分母和第一个位

clb Y,X0 ; 计算前导零 asll.l X0,Y ; Y=den\*2^q

sub Y,A ;A=R(q), Carry=1<sup>,</sup>这时Y>A

; 计算位q; 1, 这时R(q)>=0

bftstl #\$8,A2 ; 如果是正数,设置Carry

;除以环数

; 计算位q-1...0 X0 rep

; Carry拥有最低有效位 div Y,A

rol.l A ;最后Carry必须进来

: DIV会破坏最高位

;屏蔽位0...q-1

eor.l Y,Y ; 清除**Y**

add.l #2,Y ;对于X0=0的情况,我们计算位0

asll.l X0,Y

dec.l Y ; Y包含掩码 and.l Y.A : 应用掩码

;应用有符号的位

brclr #\$8000, B1, Qpositive

nop

neg A

**Qpositive:**

#### 结论

在本文中,我们介绍了带DSP56800E内核的飞思卡尔 处理器能够执行全精度的32位除法。由于DSP56800E DIV指令能采用32位数作为除数,因此我们能够通过最小化 不复原除法算法(MNrDA)来实现32位除法。DIV指令最初 设计用于16位不复原除法。在该除法中,除数的首次移动 自动设置为全16位。

与32位除法不同,在16位除法中采用MNrDA会增加最坏 情况下的执行时间,因为计算和执行初始除数移动会或多 或少地耗费掉减少的迭代次数。另一方面,对于32位除法, 我们超过了16位处理器的寄存器规格,因此MNrDA是最佳 选择。这种方法的另一个好处是迭代次数减少的实际效果, 与纯粹的不复原除法算法需要32位迭代的因素之间的平衡。

David Baca是飞思卡尔的应用程序工程师,在飞思卡尔工作了近两年的时间。他拥有电子工程和工商管理硕士学位,目前 正在攻读人工智能博士学位。在加入飞思卡尔之前,Baca曾参与过NASA和美国空军等机构赞助的研发项目。

#### **Daniel Torres**

# 采用BLDC、PMSM和SMPS的 电机控制和电源设计

#### 介绍

现在,大部分帮助我们生活得更轻松、更舒适的设备都 需要极性运动的控制,诸如洗衣机、冰箱、风扇、空调、 电动工具和搅拌器等等。

所有这些设备都需要消耗能量以产生机械运动,而有效 利用能源的途径取决于控制系统、电气机构的设计及控制 算法等。作为人类,我们面临的一个最大挑战是如何有效 地利用能源。在解决这个问题的过程中,人们将大部分 精力集中在机械运动控制系统上。因此,许多节能方面的 进步是通过改进电机控制技术、结构设计、材料和制造 精确度来实现的。

早在几年前,人们就已经开发出了更高效的控制技术, 但执行这类复杂算法和计算所需的CPU成本较高,不能 满足成本敏感市场(如家电市场)的需求。这种情况在最近 几年已经发生了变化,成本更低而且具有执行这些复杂的 控制算法所需的所有功能的高性能数字信号控制器已经 面世。

实现节能的另一个开发领域是功率转换。功率转换系统 用于将电能从一种形式转换为另一种形式,在此过程中, 由于系统的固有能耗、拓扑结构的效率、控制技术以及所 使用的电子元器件,必然会产生一定的能量损失。大部分 功率转换控制是由模拟电路实现的,但新的节能法规提出 的要求越来越高,使得模拟控制系统越来越难以达到这些 要求。

微控制器(MCU)和DSC的使用为此开辟了新的前景。 现在,借助数字控制技术和高性能、低成本的数字信号 控制器实现的复杂算术计算,功率转换系统的效率达到 98%是完全可行的。

#### 机械运动控制设计中的难点

在机械运动控制中会使用多种电机,包括无刷直流电机 (BLDC)、有刷换向永磁直流电机、线性电机和步进电机。

系统工程师不但需要选择正确的电机来完成机械动作, 同时还必须选择适当的控制环路结构来满足系统的机械和 电子时变响应的要求。控制环的调节通常在电子驱动装置 的设计阶段进行。

由于不同的电机对电子驱动装置有一系列不同的设计 要求,开发人员可能需要处理大量的设计变量。此外, 由于电动机的感性特点,它容易造成电磁干扰(EMI)、射频 干扰(RFI)和具有破坏性瞬间高能量,因此,电机本身也使 电子驱动装置的设计变得更为复杂。这类设备的设计不但 要避免电磁干扰(EMI)和射频干扰(RFI),同时还必须能够 承受瞬间过电压和过电流的情形。

BLDC电机已广泛用于许多应用领域。BLDC电机不带 换向器,因而比直流电机更可靠。BLDC电机同时也在 许多方面优于交流感应电机。BLDC电机通过转子磁体 生成旋转磁通,具有很高的效率,因而它们一般用于高端 家用电器(如冰箱、洗衣机和洗碗机)、高端水泵、风扇和 其它需要较高可靠性和效率的设备中。

由于BLDC电机的结构非常牢固,所以被广泛应用于泵、 风扇和压缩机等应用中。这些应用的一个共同特点是它们 不需要位置信息,只需要速度信息,而且只需要控制 速度。BLDC电机的使用不需要复杂的控制算法。

在BLDC电机中,必须知道转子的位置,才能提供相电压 对并控制其电压值。如果使用传感器检测转子的位置, 那么检测到的信息必须传送到控制单元中去。

这就需要与电机建立额外的连接,可是这在有些应用中是 无法接受的。有时候可能无法建立与位置传感器的物理 连接。有时,位置传感器和布线所产生的费用可能是无法 接受的。虽然物理的连接问题可以通过在电机内部集成 驱动器的方法加以解决,但大量的应用由干低成本的 特点,需要无传感器的解决方案。

永磁同步电机(PMSM)可以用一个与电源频率同步的恒定 速度进行旋转,而不受负荷或线路电压的影响。电机运行 可以保持恒定的、与电源频率同步的速度,只要转矩 不超过电机极限运行值。因此,PMSM是高精度定速驱动 的理想选择。

3相PMSM是一种永励电机。它能产生非常高的功率 密度、非常高的效率和极好的响应,所以能适应机械工程 领域中最复杂的应用。另外它还具有很强的过载运行 能力。PMSM基本上不需要维护,因此可以确保最高效的 运行。

精确的速度调节使PMSM成为特定工业过程的理想选则。 PMSM的速度/转矩特性非常适用于直接驱动大马力、 低转速(rpm)的负载。

同步电机能够以更高的功率因数运行,因此能提高整个 系统的功率因数,进而能消除或减少功率因数的损失。 功率因数的提高还可以减少系统及电机终端的压降。

PMSM舍弃了激励线圈,而且转子的转速与定子磁场的 转速率相同。PMSM的这种设计可以减少转子铜损, 与传统的感应电机相比可以产生极高的峰值效率。 PMSM的功率重量比也高干感应电机。

功率电子和微电子领域的进步使PMSM可用于高性能的 驱动,而这在过去是只能使用直流电机的。

#### 功率转换设计中的难点

电源的主要作用是不论电网的情况如何,都能向负载 提供经过调节的稳定的能量。由于具有很高的效率和 功率密度,开关模式电源(SMPS)被广泛用干办公设备、 计算机、通信系统和其它应用中。

由在数字信号控制器(DSC)上运行的软件进行完全数字化 控制的SMPS比混合模拟器件和处理器控制的方案具有 更多的优势,包括可编程性、适应性、更少的元器件 数量、设计重复使用性、处理的独立性、高级调整功能和 更好的性能等。

采用完全数字化的控制后,SMPS系统变得更加灵活, 能够实现复杂的控制算法,从而提高效率并降低成本。 基于控制器的SMPS系统将功率电子技术与高性能数字 信号处理能力相结合,提供了一种全新的功率电子设计 方法、还提供了SMPS系统经常需要的高级控制和通信 功能等。

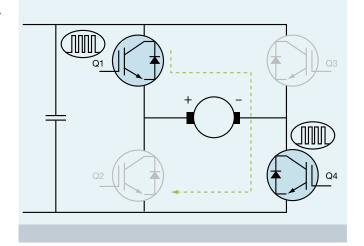

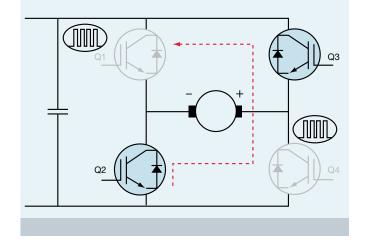

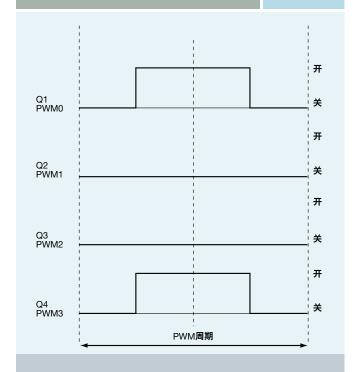

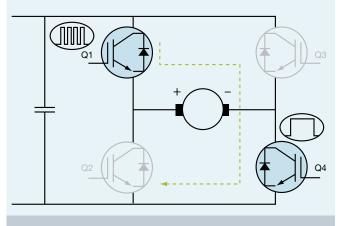

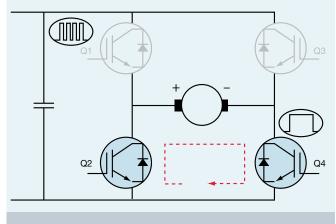

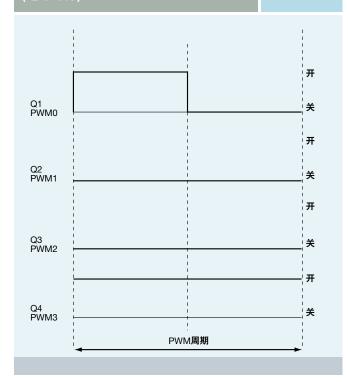

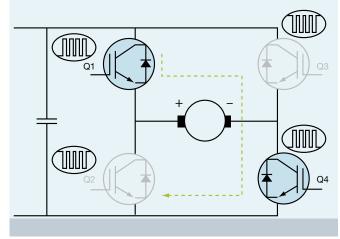

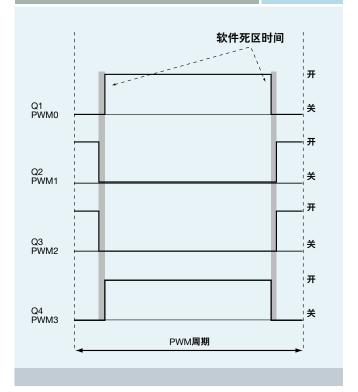

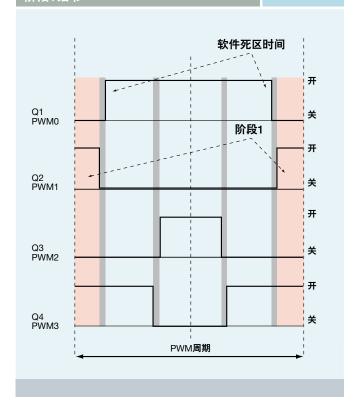

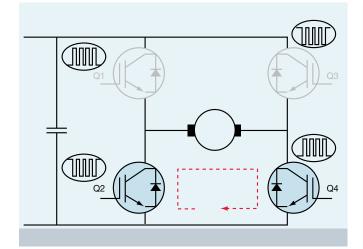

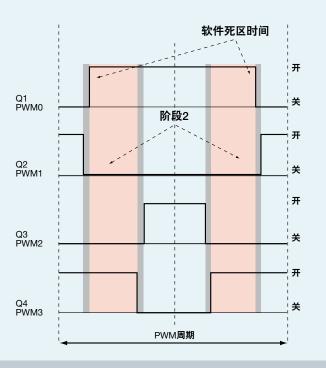

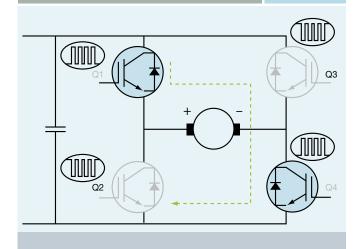

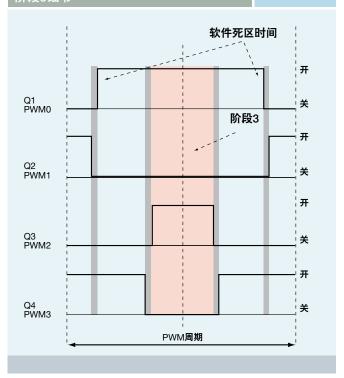

#### 无刷直流电机的控制原理

BLDC电机是一种电气旋转机械,具有类似于感应电机的 经典三相定子。其转子表面装有永磁体。它也称为电子 换向电机。转子上没有电刷,换向在特定的转子位置上以 电子方式完成。定子通常由磁铁薄片制成。定子相位绕组 插入凹槽中(分布式绕组),或作成绕在磁极上的线圈。 由于气隙磁场是由永磁体产生的,所以转子磁场恒定 不变。永磁体的磁化及其在转子上的分布是经讨选择的, 可以确保反电势(定子绕组中由干转子运动而感应的电压)。 的波形是梯形的。这样就可以采用具有矩形波形的直流 电压来生成低转矩纹波的旋转磁场。

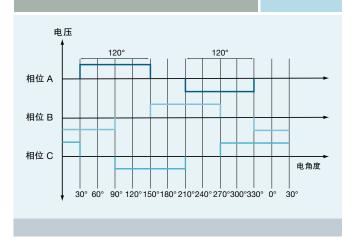

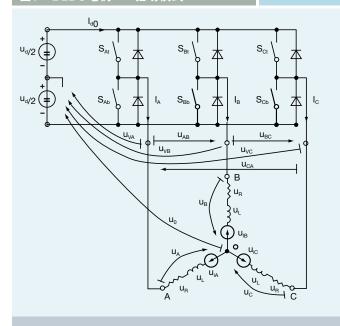

#### 图1: BLDC电机的三相电压系统

这种电机的每个相位可以有多对磁极。每个相位的磁极对 的数量决定了电气旋转与机械旋转之间的比率。例如, 图中所示的BLDC电机每个相位上有三对极对,表示三次 电气旋转对应于一次机械旋转。

由于所施加的矩形电压很容易产生,所以电机控制和驱动 变得简单。但是必须知道转子的位置在某个角度,才能让 所施加的电压与反电动势对齐。反电动势与换向动作对齐 是非常重要的。只有这样,电机才能作为直流电机以 最高的效率运行。因此,控制和实现的简单使BLDC电机 成为低成本、高效率应用的最佳选择。图1描绘了加在 三相BLDC电机上的波形。

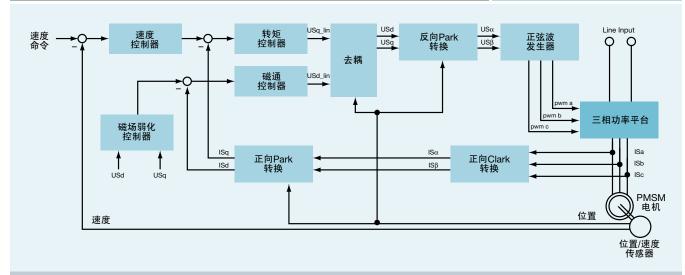

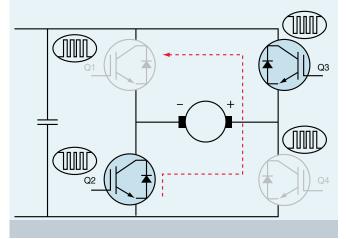

#### 永磁同步电机的控制原理

借助诸如失量控制等复杂的控制方法,PMSM可以提供与 高性能四象限直流驱动电机相仿的控制功能。

失量控制是永磁同步电机的一种先进控制方法,这种方法 利用电机磁场定向的原理来控制磁通量、电流和电压的 空间失量。可以建立一个坐标系统,将失量分解成磁场 产生的部分和转矩产生的部分。这样,电机控制器(即失量 控制器)的结构几乎与分励直流电机完全相同,从而简化了 永磁同步电机的控制。过去开发这种向量控制技术的目的 是在同步电机中达到同样出色的动态性能。

在此方法中,必须将定子电流分解为的产生磁场的部分 和产生转矩发的部分,以便分别控制磁通量和转矩。 要做到这一点,必须建立与转子磁场关联的转子坐标 系统。该坐标系统通常称为"d,q坐标系统"。将转子坐标 系统转换成定子坐标系统通常需要很强的CPU运算 性能。

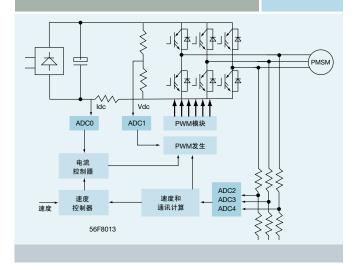

图2: 给出了CPU在失量控制技术中需要执行任务的 方框图

要执行失量控制,必须做以下步骤的工作:

- 测量电机的数值(相电压和电流)

- 用Clarke转换将它们转换成两相系统(a、B)。

- 计算转子磁通空间失量的大小和位置角度

- 用Park转换将定子电流转换成d,q坐标系统

- 定子电流的扭矩(isq)和磁通量(isd)分量由控制器分别 进行控制

- 用去耦模块计算定子电压空间失量的输出值

- 通过Park逆转换将定子电压空间失量从d,q坐标系统 转换回固定于定子的两相系统

- 用正弦调制生成三相输出电压

#### 56F8013 DSC的优点和特性

飞思卡尔的MC56F801x DSC系列在单个芯片上结合了 DSP的计算功能和MCU的控制功能,非常适合数字电机 控制。这些混合控制器提供多种专用外设,如脉宽调制 (PWM)模块(组)、数模转换器(ADC)、定时器、通信外设 (SCI、SPI、I<sup>2</sup>C)、内置闪存和RAM等。

- 32 MHz运行频率时高达32 MIPS

- 片上内存包括高速易失性和非易失性组件

- 16KB编程闪存

- 4KB 统一数据/程序RAM

- 闪存加密功能防止未经授权访问其内容

- 闪存保护防止意外修改

- JTAG/增强型片上仿真(EOnCE),提供无干扰实时调试

- 4个36位累加器

- 16位和32位双向桶型移位器

- 具有特殊寻址模式的平行指令集

- 提供硬件DO和REP循环

- 3个内部地址总线

- 4个内部数据总线

- 支持MCU类型的软件堆栈

- 控制器类型的寻址模式和指令

- 单周期16 x 16位平行乘-累加器(MAC)

- 已证明能采用比竞争性架构更小的内存面积,提供更多 控制功能

#### 机械运动控制的推荐方案

BLDC系统结合了交流和直流电系统的优点。与有刷直流 电机不同,BLDC系统采用的电机一般是一种具有梯形反 电动势波形的永磁交流同步电机,而且用电子换向取代了 直流电机中的机械电刷。尽管这种控制方法在相位换向过 程中会产生转矩跳变,但它还是能满足以控制转子速度为 目标的大部分应用的需要。

反电动势波形为正弦波的PMSM电机也可应用于BLDC 系统。但是,定子磁通和转子磁通之间的矢量角度应保持 在60°和120°电角度之间。运行期间会产生转矩波纹, 但平均扭矩可维持恒定,从而能满足大部分低端应用程序 的要求。图3显示了既可用于实现PMSM失量控制,也可 用于实现BLDC电机控制的方框图。

#### 图3: PMSM/BLDC电机控制方案通用方框图

反电动势的过零信息可用干确定转子的位置,以实现 正确的换向,决确定开通哪个功率晶体管以获得最大的 电机转。成本最低且最可靠的反电动势过零信息的采样 方法是将电阻网络采集的反电动势信号发送到ADC输入端 或GPIO。在有传感器控制结构中,转子每转动60°电角度 换向一次。这意味著只需6个换向信号就足以驱动BLDC 电机。此外,有效的控制还需要Bemf相与电源相位之间的 同步,要确保Bemf只在不馈电的60°区间内过零一次。

由于在某一时刻定子线组中只有两个有电流,所以这 两相电流是相反的,而第三相位电流为0。既然知道三个 定子电流总和等于0(星形绕组定子),就可以计算预期的 Bemf瞬间波形。三个定子端的电压之和是中心点电压 (Vn)的三倍。各个Bemf在每次机械旋转中过零两次。由于 Bemf的数值计算比较方便,再由于56F8013的信号处理 能力,因此才能够得到与换向有关的6个必需的信息。

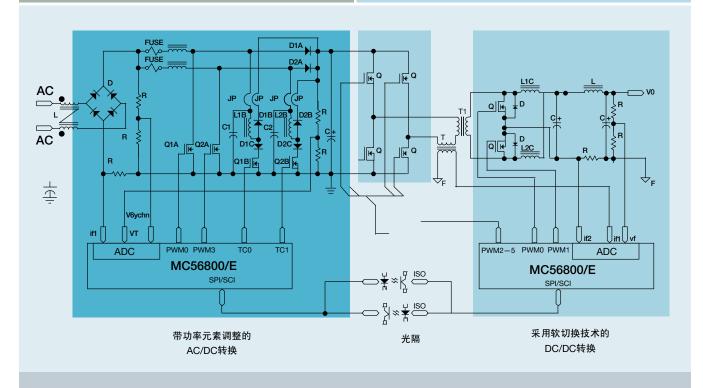

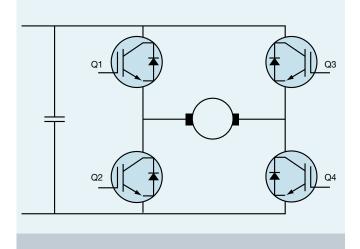

#### 开关模式电源的推荐方案

一般的SMPS AC/DC系统包含两大部分:前端是带功率 因数调整(PFC)的 AC/DC转换器;后端是一个全桥DC/ DC转换器。AC/DC系统采用交错型PFC升压控制结构, 包括一个全桥整流器、两个平行交错升压PFC电路和 两个辅助开关,以实现主开关的过零切换(ZVS)。采用 ZVS算法可减小器件的压力,并提高效率,还可以在设计 中省去反向恢复输出二极管。DC/DC转换器采用以软件 实现的ZVS移相全桥控制结构,带有倍流整流器。这样 不仅减小了滤波电感的尺寸,还提高了效率。

图4是一个基于56800/E 的开关模式电源(SMPS)的电路

#### 图4: AC/DC方框图

框图。整个系统由两个56800/E芯片进行控制。前端芯片 负责PFC系统的全面控制,包括两个主开关和两个ZVS开 关。后端芯片负责DC/DC移相全桥转换器的全面控制, 包括4个主开关和2个同步整流器。软件中用于PFC和 DC/DC转换器的功能包括:电源系统中的2个数字PI调整 功能,所有开关的控制、软启动、前端PFC正弦参考数字 信号的发生、通讯、电源保护和监控功能。

#### 参考资料

www.freescale.com

#### 应用笔记AN1931

"采用DSP56F80x实现三相永磁同步电机的矢量控制" 飞思卡尔半导体

#### 引用笔记AN3115

"采用56F8300数字信号控制器实现数字AC/DC开关 模式电源"

飞思卡尔半导体

#### 设计参考手册DRM070

"采用MC56F8013实现三相BLDC电机的无传感器控制" 飞思卡尔半导体

#### 设计参考手册DRM077

"采用56F8013器件实现PMSM和BLDC的无传感器控制" 飞思卡尔半导体

Daniel Torres是飞思卡尔半导体的应用工程师,在数字信号控制器、ColdFire控制器和8位MCU领域拥有丰富的 经验。他主要从事电机控制和电源管理。

## 最新的S08/RS08工具

## 新一代SPYDER已推出

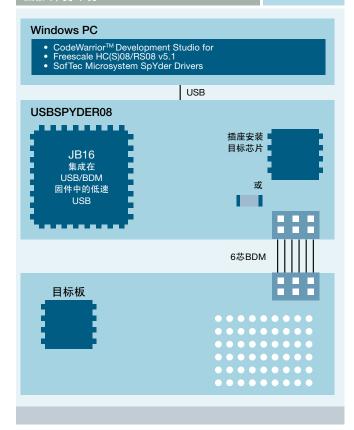

飞思卡尔半导体是全球领先的嵌入式半导体设计和生产商, 产品广泛应用于汽车、消费、工业、网络和无线市场。 过去几年时间里,我们越来越重视为大众市场和专业市场 提供工具。随著我们新增了电子商务网站、馈赠样品、 免费编译器和调试器、以及经济高效的硬件工具等,设计 人员现在很容易接触到飞思卡尔的微控制器系列。SofTec Microsystems™推出最新的工具,2007年价格仅为29美元 的USBSPYDER08证明了我们提供小型、快捷、经济高效 的硬件工具的承诺,助您的设计启动。

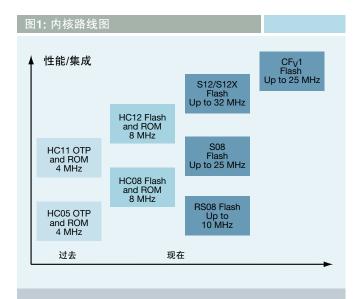

上个世纪80年代推出的HC05和HC11 8位内核目前已经 广泛应用到市场的各个主要领域。在90年代末又推出了 HC08 (8位)和HC12 (16位)内核,它们现在更受某些特定 的消费和工业应用客户的欢迎。2000年初,HCS12 16位 内核和HCS08 (S08) 8位内核引进了一项重要功能, 即后台调试模块(BDM)。该模块使开发过程变得更轻松。 图1是飞思卡尔内核路线图的一部分。

最新推出的RS08(精简的HCS08内核,通过减少指令和 其他降低成本的方法使物理体积减小)和8位S08微控制器 包含单线后台调试接口,支持片上非易失性内存的在线 编程和复杂的无干扰调试功能。该模块有助干开发经济 高效、使用方便的工具。同样的BDM连接还出现在刚刚

推出的32位微控制器ColdFire V1内核产品上(如需了解更 多信息,请参见www.freescale.com/flex)。

2005年, freegeeks.net为HCS12微控制器社区提供了 一种名为TBDML(Turbo BDM Light)的开放源代码工具。 在12个月的时间内,该产品的下载次数就达1454次, 我们意识到它对工程师非常有用。现在,我们为8位 MCU也提供了同等具有BDM功能的工具,可以通过两种 形式得到:

- 针对S08的开放源代码BDM (OSBDM) 详细信息可见 于飞思卡尔论坛(www.freescale.net/forums)。这种自 制工具的物料单(BOM)成本不到10美元,可以购买由 小公司预先制作的产品。

- USBSPYDER08开发工具包支持MC9S08QG、 MC9S08QD和 MC9RS08KA 8位微控制器。这套工具 的设计支持飞思卡尔未来的8位、8管脚MCU。

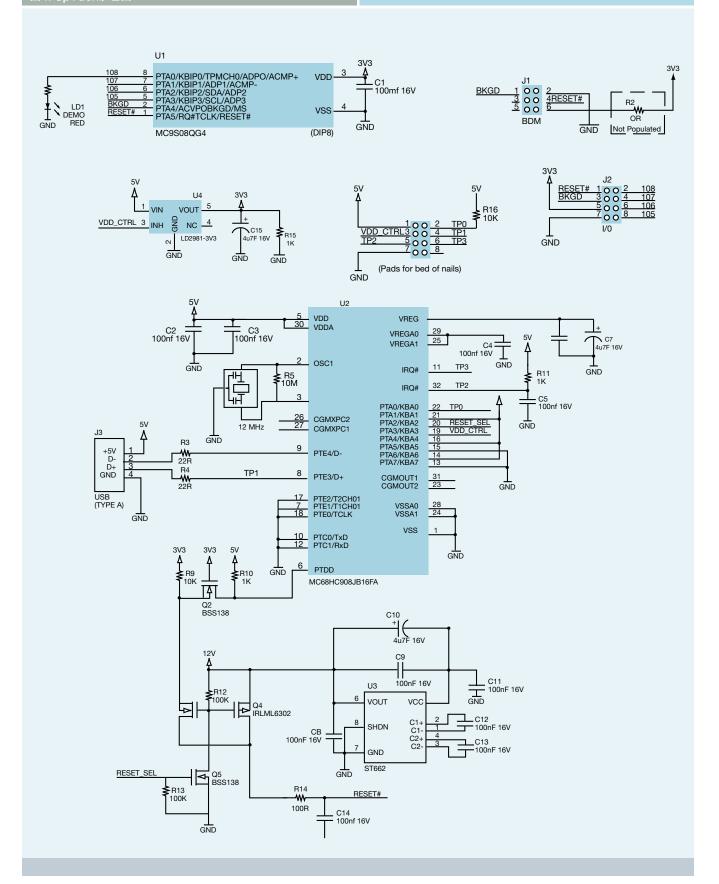

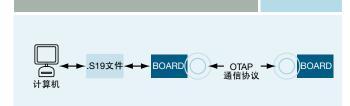

OSBDM和USBSPYDER08在本质上是一样的。它们是 您的开发环境(基于Windows PC)和目标MCU之间的 接口,如图2所示。这些工具的主要目标是提供更便宜、 更方便的设计,供爱好者选用。

USBSPYDER08是飞思卡尔新的USB-to-BDM开发工具。 如果您不熟悉BDM,它与新近推出的8位和16位MCU上 使用的debugWIRE或JTAG类似。

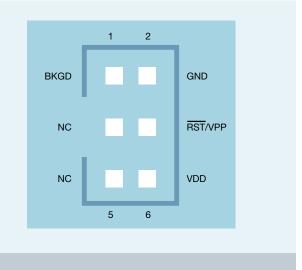

这些芯片上的后台(BKGD)引脚提供一个单线的后台调试 接口,连接到片上调试模块。如需了解这些调试模块的 更多信息及使用方法,请参见S08或RS08说明书的开发 工具章节。这个接口是单线的,通常是一个6芯的接插件, 称为BDM端口,用来和目标板的接口。如图3所示。

BKGD脚的主要功能是用于后台激活模式命令和数据传送 的双向串行通信。复位时,这个管脚用来选择是启动进入 后台激活模式,还是启动用户的应用程序。此外,这个 管脚还要求发出定时同步响应脉冲,以便开发工具主机 确定正确的后台调试串行通信时钟频率。后台调试控制器 (BDC)命令从主机连续发送到目标S08或RS08 MCU的

#### 图2: 开发环境

BKGD管脚上。这些命令和数据采样自定义的BDC通信 协议发送,最高有效位(MSB)先出。通过单线的后台 调试接口,可以采用相对简单的接口盒,将主机的命令转 化为BDC的命令。

在USBSPYDER08中,使用的是低速通用串行总线 (USB)接口。为了方便,此工具采样USB闪存棒的形式。

USBSPYDER08是由SofTec Microsystems构建的 一种经济高效的工具,飞思卡尔半导体提供了全面协助。 USBSPYDER08与获奖的CodeWarrior®开发工具一道 使用,为您编辑、编译、下载、在线仿真和调试代码提供 必需的基本工具。全速率程序执行允许开发人员以实时 方式执行硬件和软件测试。这个工具运行的的总线速率 可高达10MHz,支持3.3V的MCU运行电压。它的电路 板上有一个插座安装的MCU,可以替换为其他能支持的 PDIP封装器件,这些器件可以从www.freescale.com网站 上申请少量样品。为了提高此工具的灵活性,它安装了一 个BDM接头,可以对能支持的其他封装的产品进行板外的 调试,或者在开发需要时可以与其他电路板元器件协同 工作。

#### 图3: BDM连接器

#### USBSPYDER08是如何工作的

依靠S08和RS08后台调试控制器(BDC)模块,USBSPYDER08 能够快捷、便利地对片上闪存及其他内存进行编程。它是 讲行开发的主调试接口,可以对内存数据进行无干扰的 访问,还具有传统的调试功能,如CPU寄存器修改断点 以及单指令跟踪命令等。

该工具采用USB接口与PC通信,采用USB总线电压给工具 和微控制器供电,不再需要过去的体积庞大的适配器, 从而成为真正的便携式设备。如果不用拖动太多电机运行 的话,USB电源也可以给目标板供电(高达100mA)。 MC9S08JB16 (JB16)微控制器处于USBSPYDER08工具 的核心。该MCU带有USB(2.0低速)接口,借助USB提供 的5V电压运行。当该工具支持RS08 MCU时,需要12V 电压进行编程。JB16识别目标芯片,然后通过PTD0的 控制用DC-DC转换器芯片启动12V信号。

#### 第1步-USBSPYDER08 电路板组装

USBSPYDER08工具的一些基本部件已经安装在该产品上, 您可以通过一个插座安装的微控制器,把它当作一个 独立的工具来使用。如果需要采用其他的封装形式或 独立的目标板,它同样也支持。在标为R2的空焊盘上 加上0 ohm的电阻或短路线,就能把电源连接到BDM 插座上,这样您就能使用另一个目标板了。最终的结果 是"USBSPYDER08探索工具包"变成了BDM盒。

#### 第2步 - 调试器安装

USBSPYDER08 CD中提供有免费的CodeWarrior Development Studio for Freescale HC(S)08/ RS08 v5.1特别版。如需了解本工具的更多信息,请访问 www.freescale.com/codewarrior。如果没有证书密钥, 本产品将以演示模式运行,代码大小仅为1KB。要突破 1KB限制,有两种选择:

- 联系飞思卡尔获得无时间限制,免费的证书密钥,可将 代码容量限制增加到16KB。

- 联系飞思卡尔获得30天限制的免费证书密钥,可以在 无代码容量限制的情况下运行编译器。

### 第3步 - 驱动器

一旦电路板做好了开发准备,CodeWarrior也已安装, 接下来就是让USBSPYDER08与调试器进行通信。通过 随附的CD安装驱动后,当该工具就与PC首次连接时, Windows会识别新USB设备,"Windows新硬件向导 "对话框打开,要求提供需要的驱动。开发人员只需 选择"自动安装"选项就可完成安装了。

#### 第4步 - 准备探索

值得赞叹的是,USBSPYDERO使用目标MCU而非仿真器 执行在线调试。这样,微控制器的外围设备(如计时器、 A/D转换器、串行通信模块等)就不需要通过软件或外部器 件来重新构建了。

为某个USBSPYDER08支持的器件用CodeWarrior工具 创建新项目,首先应从CodeWarrior工具入手。从主菜单 上选择"文件>新项目"(File > New Project)或在启动选项 框中点击"创建新项目"(Create New Project)。然后会 出现一个对话框,提示从下拉菜单上选择目标器件。" 选择"SofTec HCS08"作为连接类型。然后选择代码 类型、项目名称和位置。如果不需要添加新文件,而且

您又不想使用器件初始化工具,请按"完成"(Finish)。 CodeWarrior将创建项目,建立代码框架,引用带有所有 寄存器定义的头文件。一旦您写好代码,准备开始调试, 请"制作"(make)文件,即开始编译。可以通过多种方法 完成该操作,例如可以使用窗口的快捷键,使用下拉菜单 "项目"(Project),或按F5键,然后按F7键。

首次进入调试过程时,系统会出现"MCU配置"(MCU Configuration)对话框,提示选择连接到您的PC的调试 硬件。连接类型一定要选择"USBSPYDER08"。这时, CodeWarrior工具已经擦除内存并重新编程了,如果选定 的MCU具有相应的功能,它会调整振荡器。

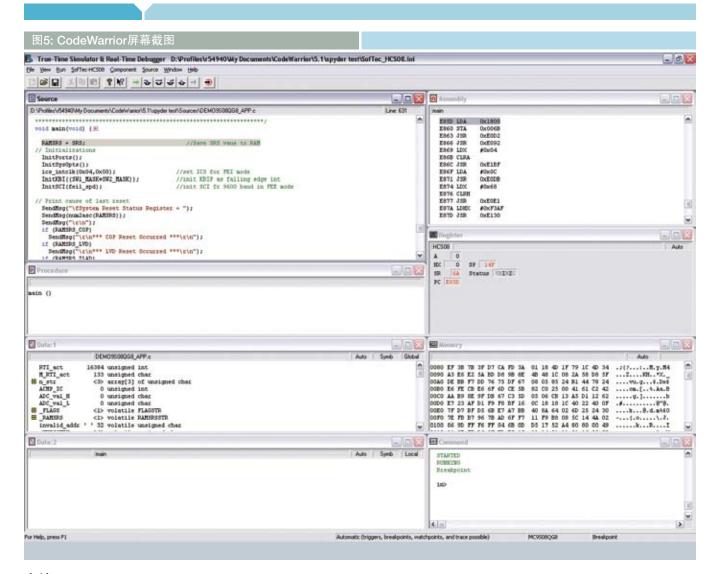

在这个阶段,您已经拥有开始调试代码所需的工具。 CodeWarrior工具套件提供了多种不同的方式,如断点、 观察点和跟踪缓存等来分析程序流程。所有这些功能都是 利用目标微控制器的调试外设来实现的。图5显示了一个 CodeWarrior窗口,它包括:

- 显示您的代码的源代码窗口

- 汇编窗口,在此您可以看到编译器由您的源代码生成的 汇编代码

- 可以看到CPU寄存器的寄存器窗口

- 内存窗口,在此您可以观察任何位置,或者强制字节为 另外的值

- 显示数据、进程和命令的其他窗口

右击窗口并修改模式或格式,可以修改数据格式和 数据刷新率。通过"文件>保存配置"(File > Save Configuration)可以保存首选设置。不熟悉CodeWarrior 工具套件的新用户需要花一点时间先熟悉Start/Continue, Single Step, Step Over, Step Out, Assembly Step, Halt和Reset Target按钮。在熟悉调试环境时,诸如 AN3335-Introduction to HCS08 Background Debug Mode和AN2616-Getting Started with HCS08 and CodeWarrior Using C这样的应用笔记都是不错的资源。

MCU旁边的焊盘可以连接到某个范围,允许实时地监控 调试器外部的管脚。

## 小结

USBSPYDER08探索工具包是一种非常灵活的工具,它体 积小,使用简单,能够满足低预算开发要求。它支持飞思 卡尔的8脚S08器件,也能选择片外目标来支持扩展引脚数 的器件。当与CodeWarrior工具套件(IDE、编译器、调试 器、编辑器、连接器、汇编器、运行控制器件)提供的强大 能量结合后,飞思卡尔为大众和专业市场提供了构建平台 和应用程序所需的关键工具。

令人愉悦的开发之旅!

#### 更多阅读资料

#### AN3335

Introduction to HCS08 Background Debug Mode

#### AN2616

Getting Started with HCS08 and CodeWarrior Using C

#### **BR8BITLOWEND**

A Little 8-bit Goes a Long Way

#### HCS08QRUG

HCS08 Peripheral Module Quick Reference

#### RS08 Peripheral Module Quick Reference

A Compilation of Demonstration Software for RS08 Modules

Inga Harris 2000年毕业于Strathclyde大学,获得电子和电气工程荣誉学位。

她在飞思卡尔曾先后担任过8位MCU系列的技术市场开发人员和应用工程师,重点研究消费类和工业市场。

## Pattye Brown

## 适用于传感与控制应用的

# ZigBee®和低成本无线网络

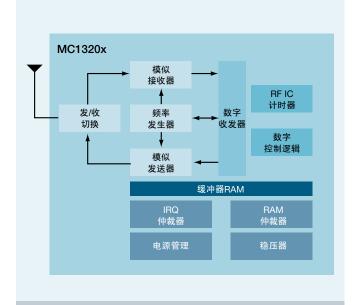

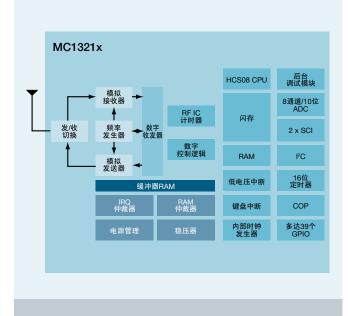

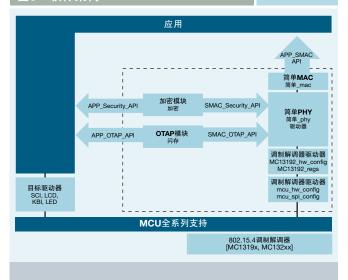

图1: 可以与各种微控制器一起使用的独立

(飞思卡尔半导体MC1320X)

图2: 封装(SIP)在一起的收发器和微控制器集成

许多感应、监控和控制应用程序都具有融合低成本无线 网络功能的独特潜力。低成本无线网络解决方案通常需要 30~70米或者更短的距离,250kbps及以下的数据速率, 在很多情况中还要求实现最优化电池使用寿命的功能,特别 是对于终端节点功能而言。如果在开始设计之前能够提前对 几个关键因素进行预先的分析,无线网络的实现会更有效。 这些关键因素的阵列会帮助您选择合适的元器件和方案。 这里也提供了一些参考设计原理图作为开始设计的基准。 在制定您的设计要求时,请考虑检查如下几个方面的问题:

- 集成度

- 无线网络拓扑结构(图3)

- 。射频(RF调制解调器或收发器)

- ο 性能

- 工作电压

- o 数据速率

- ○范围

- 。 通道灵活性

- 输出功率

- o 敏感度

- 电源管理

- o 外围设备

- o 时钟

- 多层软件

- 。 硬件和软件设计的简单性

- o 天线设计

- o 封装

- 微控制器(MCU)

- o CPU特性

- 性能

- o 内存选项

- 电源管理

- 时钟源选项

- o 数模转换

- o 外围设备

- 。 封装

- 在线调试和编程

- 软件和硬件设计的简单性

这些分析将为工程决策提供一个结构清晰的前景,为设计 成功铺就一条宽阔的道路、为产品面市缩短宝贵的时间, 为低成本无线网络的实现提供一个更简单的方法。

大量可选择的低成本网络方案能够为您在设计过程中提供 高层次上的灵活性。作为一种选择,可以考虑大量供应商 提供的各种独立收发器的结构,它们可以选择与大量的 各种MCU(图1) 结合使用。另一种同样有效的选择是考虑 使用最新解决方案,即提供收发器/MCU集成的产品 (图2)。如果您的工作涉及多个相似的终端产品,设计部件 和工程投资的再利用应该非常重要。因此,解决方案的 结构性评估选项就既具有成本效率又具有资源效率。考虑 周全的研究可以为在单一平台上设计多种终端产品提供 良好的基础。

#### 无线网络技术

2.4 GHz的工业、科学和医学(ISM)波段支持多种短距离 无线网络技术。每种技术的开发都是为了更好地满足特定 应用或功能的需求。与2.4 GHz频率范围有关联的最为 常见网络拓扑结构是Bluetooth™、WiFi™、ZigBee及 其他专用解决方案。非标准的专用解决方案具有一定 风险,这些解决方案与供应商具有密切关系,因而随时 可能发生变化。

ZigBee联盟定义的ZigBee 是基于IEEE 802.15.4标准的 解决方案,是专门为支持感应、监控和控制应用程序而 开发的。ZigBee解决方案具有一些明显优势,例如具有 功率低、通信稳定和自愈网状网等。ZigBee解决方案的 频率通常在868/915 MHz或2.4 GHz频谱范围内。

ZigBee技术解决方案的数据速率是250 Kbps。使用碱性 电池或锂电池,功耗必须非常低才能使电池使用寿命以 年计(相当于电池保存期限)。理论上ZigBee技术最多可以 支持65000个节点。ZigBee技术解决方案支持的最佳 感应、监控和控制应用通常包括:

- 个人和医疗监控

- 保安、访问控制和安全监控

- 过程感应和控制

- 供暖、通风和空调(HVAC)的感应和控制

- •家庭、楼宇和工业自动化

- 资产管理、状态和跟踪

- 健身监控

- 能源管理

| 图3: 无线网络技术     |                        |                |                                       |                                               |                                            |                            |

|----------------|------------------------|----------------|---------------------------------------|-----------------------------------------------|--------------------------------------------|----------------------------|

|                | ZigBee®                | Bluetooth®     | UWB™                                  | Wi-Fi™                                        | LonWorks®                                  | 专有                         |

| 标准             | IEEE® 802.15.4         | IEEE 802.15.1  | IEEE 802.15.3a<br>(to be ratified)    | IEEE 802.11<br>a, b, g<br>(n, to be ratified) | EIA 709.1, 2, 3                            | 专有                         |

| 行业组织           | ZigBee Alliance        | Bluetooth SIG  | UWB Forum<br>and WiMedia™<br>Alliance | WiFe Alliance                                 | LonMark<br>Interoperability<br>Association | 无                          |

| 网状、星状、<br>树形拓扑 | 星状                     | 星状             | 星状                                    | 媒体相关                                          | P2P、星状、<br>网格                              |                            |

| RF频率           | 868/915 MHz<br>2.5 GHz | 2.4 GHz        | 3.1–10.6 GHz<br>(U.S.)                | 2.4 GHz 5.8 GHz                               | N/A (wired technology)                     | 433/868/900<br>MHz 2.4 GHz |

| 数据速率           | 250 Kbps               | 723 Kbps       | 110 Mbps-1.6<br>Gbps                  | 10-105 Mbps                                   | 15 Kbps-<br>10 Mbps                        | 10-250 Kbps                |

| 范围             | 10–300m                | 10m            | 4–20m                                 | 10–100m                                       | Medium-<br>dependent                       | 10–70m                     |

| 功率             | 很低                     | 低              | 低                                     | 高                                             | 有线                                         | 很低-低                       |

| 电池使用(寿命)       | 硷性电池<br>(几个月/年)        | 可充电<br>(几小时/天) | 可充电<br>(几小时)                          | 无                                             | 硷性电池<br>(几个月/年)                            |                            |

| 节点             | 65,000                 | 8              | 128                                   | 32                                            | 32,000                                     | 100–1,000                  |

### RF调制解调器或收发器(射频)

在构建低成本无线网络系统时,射频(RF)调制解调器 的几个特性是需要考虑的。大部分低成本的个人局域网 (PAN)RF调制解调器解决方案都推荐使用2.0-3.6V的 电源。

对轻质无线网络来说,低数据速率就足以支持监控、感应 和控制功能,同时也有助于管理系统功耗。在这类应用中, 最常选择的是2 MHz通道上的250kbps积分偏置相移键控 (O-QPSK) 数据,通道间有5MHz的间距,在全频谱范围 进行编码和解码。在这种环境中,收发器醒来后,侦听 开放通道并以较低数据速率发送小型数据包。然后收发器 会关闭,直到遇到下一个事件。顺序、电源快速开启延时、 较低数据速率和小型数据包等因素让802.15.4可以选择 合适的时间增量,使数据传输达到最高效率。

正如前面提到的,对于感应和控制子系统,ZigBee技术是 支持数据传输距离和功率要求的最佳方案。ZigBee联盟 规范定义的典型距离是10-70m,但许多解决方案可提供 远高于该范围的视线距离。

在相关的设计规划中,仔细检查可用的收发器通道的数量 和类型是非常重要的。可选择的收发器通道使设计人员 可以利用不同的通道来最大限度地降低噪声,特别是远离 更加拥挤的2.4GHz WiFi信道。

您还应检查一下0 dBm以上到+4 dBm范围内的典型发送 输出功率。通常在-90 dBm范围的接收灵敏度能够对 感应、监控和控制功能已经足够。数据包的发送和接收带 有缓冲,这能够简化用于收发器的低成本微控制器的 管理。射频和收发器还应提供连接质量和能量的检测 功能,以便网络性能的评估。

多种低功耗模式可提供省电功能,用以将系统能耗降至 最低。这些模式一般包括关闭电流(off current)、休眠 电流(hibernate current)和半休眠电流(doze current), 其电流可达个位数微安(uA)级。当范围或环境需要较低的 功率就能完成发送和接收目标时,可编程输出功率的功能 还允许设计人员减少功耗。确保选定的解决方案能够提供 这些功能将有助于最大限度延长全功能/协调器或终端节点 设备中的电池使用寿命,使得电池寿命可以达到整个保存 期限。

检查可以减少MCU资源要求的其他基本外围设备(如内部 定时器比较器)。在各种不同的配置和引脚数类型中都有 通用输入/输出端口(GPIO)。在实际应用中GPIO很大程度 上根据与其他设备的接口要求来决定。在那些采用收发器 和独立的MCU实现灵活性的解决方案中,通信由串行外 设接口(SPI)端口处理。可以预见的是,当射频和MCU 集成到单个封装或芯片中时,收发器与MCU通过内置或 内部SPI命令通道进行通信。而且,集成解决方案还带有 低噪声放大器(LNA)、带内部电压控制振荡器(VCO)的 功率放大器(PA)、集成的发送/接收开关、内置稳压电源和 全频率范围的编码和解码功能,所以能减少系统外部器件 需求,降低整个系统成本。

各种各样的系统时钟配置使您能够灵活地进行最终系统 设计。最适用的是能通过外部时钟源或晶振进行CPU 定时的选择。调制解调器时钟通常需要16 MHz的外部 晶振。调制解调器晶振频率的调整功能有助于确保符合 IEEE802.15.4规范要求的严格标准。

根据最终设计的复杂性和高要求,能够提供多种网络 软件拓扑结构选择的供应商才能为您提供最好的服务。 这些选择可能包括简单的媒介访问控制器(MAC)结构, 它采用4 KB或以上的MCU闪存,支持点到点或简单的 星形网络。完全符合802.15.4标准的MAC和完全兼容的 ZigBee拓扑会需要更多内存,能够为网状和集群树状网络 提供更多的支持。

采用供应商提供的参考设计、硬件开发工具和软件开发 工具可以简化设计过程。对于硬件开发工具,简单的入门 指南、带LED或LCD,可进行视图化监控的基本电路板、 还有线缆和电池等,可提供轻松的开箱即用体验。这些 工具能帮助您在几分钟内构建一个网络,并能确实地评估 网络和方案的性能。过去,一些软件设计工具,特别是 那些支持完全符合ZigBee标准的网络的工具,使用起来 非常困难。要降低准备RF调制解调器的复杂程度,应该 寻找提供基于图形化用户界面(GUI)软件设计工具的 供应商,该工具应能引导设计人员逐步完成收发器的 搭建。

天线设计是一个非常复杂的问题,特别是对那些RF设计 经验不足的数字设计人员而言。通常情况下,设计人员在 设计时会考虑以下诸多因素,如选择正确的天线、天线 调试、匹配、增益/损失,以及了解所需的辐射模式等。 我们建议通过收发器供应商提供的应用笔记了解天线的 基本知识。但是,大部分数字工程师愿意考虑使用提供了 天线设计的供应商方案。这样,他们就能集中精力进行 应用程序的设计。应该寻找以完整的Gerber文件形式提供 天线设计的天线解决方案,这样就可以直接交给印制电路 板生产商去制板。提供这样的天线设计方案的供应商就 消除了无线应用中与良好的天线设计、出色的范围和稳定 的吞吐量等有关的问题。

对干低成本的无线网络子系统的收发器部分来说,方形 扁平无引脚封装(QFN)是最佳的小体积封装解决方案。 这种封装考虑了感应和控制方案经常面临的电路板空间 限制问题。由于实施空间有限,在通常由电池供电的最终 节点中,尺寸的大小就显得尤为重要。

#### 微控制器

在选择感应和控制实施方案时有多种替代选项。有些设计 人员选择单封装系统(SiP)或单封装平台™ (PiP),它们在 单个封装中包含收发器和MCU功能。但是,如果您选择 独立的收发器和微控制器结构,就拥有了选择各种不同 MCU的灵活性,为不同的终端产品的结构进行组合和 匹配。

当选择后一种实施方案时,要通过全面的研究来选择合适 的MCU。MCU的选择取决于感应和控制应用的复杂度与 合适的性能因素的匹配,包括内存结构和外围模块等。 通常对于低成本无线感应系统来说,具有20 MHz CPU 运行频率(10MHz总线时钟)范围的8位MCU就能提供符合 这些应用的易于实现、成本低廉的替代方案。后台调试 功能,以及在线调试过程中支持单个断点(标签和强制 选择)设置(外加两个内置调试模块断点)的功能,可以提供 理想的调试环境。许多MCU方案都可以支持多达32个 中断/复位源。

感应和控制应用对内存的要求一般是8KB闪存加512B RAM,或低至4KB闪存加256B RAM。在整个工作电压和 温度上的闪存读取、编程和擦除是必需的。

各种运行模式都能对功耗能够进行精确控制,这是扩展 电池供电方案的一个重要功能。应该寻找支持正常操作 (运行)模式、内置后台调试激活模式、多种停止模式(总线 和CPU时钟停止)及等待模式等各种选择的MCU。

考虑一下选用具有内部时钟源模块的微控制器,该模块应 包含由内部或外部参考时钟控制的锁频环(FLL),内部 参考可精确调整,达到0.2%的解析度和2%的温度、电压 偏移。内部时钟源模块应支持1 MHz~10 MHz的总线 频率。MCU可为关键模块选择时钟输入,并控制其时钟 以驱动模块功能。此外,应寻找具有低功率振荡器模块 的MCU,可用软件在31.25 KHz~38.4 KHz或1 MHz~16 MHz频率范围之间选择晶振或陶瓷谐振器,并支持高达 20MHz的外部时钟输入。

选择一个能提供系统保护功能的MCU也至关重要,诸如 看门狗计算机正确操作(COP)复位选项,而且还可以选择 以专用的1KHz内部时钟源或总线频率运行。其他必须具备 的系统保护功能还包括可进行复位或中断的低电压检测, 带复位的非法指令检测,带复位的非法地址检测和闪存块 保护。

各种嵌入式外围设备有助于简化您应用的实现。建议采用 8通道、10位模数(ADC)转换器来获得精确的连续逼 近值。特别的功能还应包括自动比较、异步时钟源、温度 传感器、内部带隙参考通道和可使用实时中断(RTI)计数器 硬件触发的ADC。

感应和控制应用的其他基本外围设备包括:可选择与内部 参考信号进行比较的模拟比较器模块(ACMP)、串行通信 接口模块(SCI)、串行外设接口模块(SPI)、集成电路互连 (I<sup>2</sup>C)总线模块、2通道计时器/脉宽调制器,可用于输入 捕获、输出比较、带缓冲的边缘对齐PWM或带缓冲的 中心对齐PWM;具有预分频器的8位模数定时器模块, 以及可用软件选择边沿或边沿/电平模式极性的8引脚 键盘中断模块。

现在有多种小型MCU封装选项能满足感应和控制设计的 要求。这有助于优化有限的电路板空间,特别是在终端 节点中和电池供电的应用中。部分满足这些要求的MCU 封装包括少管脚数的塑料双列直插(PDIP)封装、方形扁平 无引脚(QFN)封装、薄型收缩外形(TSSOP)封装、双排 扁平无引脚(DFN)封装和窄体小外形(NB SOIC)封装。

在选择MCU时,周全的考虑应兼顾硬件和软件工具的 易用性、文档的清晰度、参考设计和应用代码的可用性, 以及其他设计支持。同样,在RF或调制解调器方面的 设计中,高效的集成开发环境(IDE)应包括采用图形化 用户界面(GUI)的工具,它应内置各种功能和工具,可以 简化编码和项目文件的管理,从而加快设计进程。专业 工具会对硬件层进行抽象,并根据应用的要求针对特定的 MCU提供最佳C代码,这样您就可以将精力集中在应用的 概念上。同时也要考虑快速、简单的调试和闪存编程 功能。此外,提供允许设计人员创建可重复使用的软件 组件,并在不同的项目中重复使用的方法也相当有用。

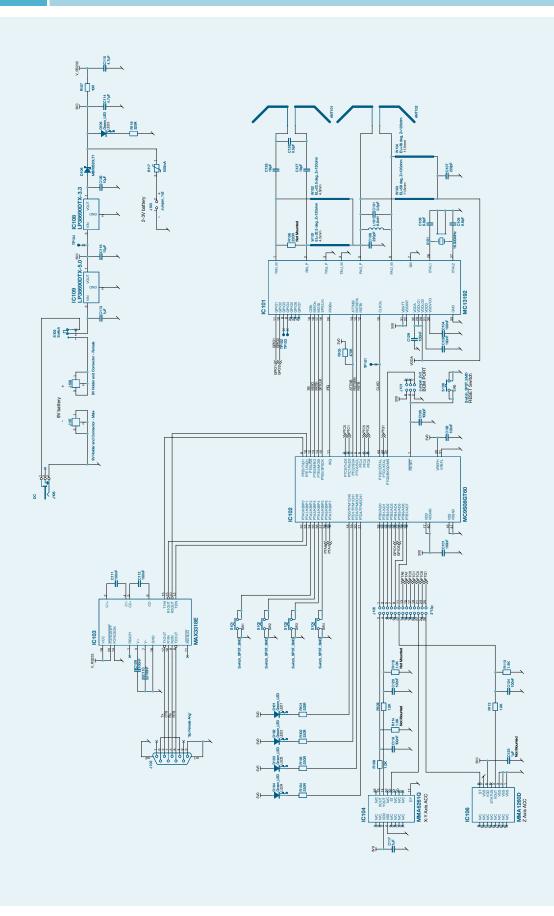

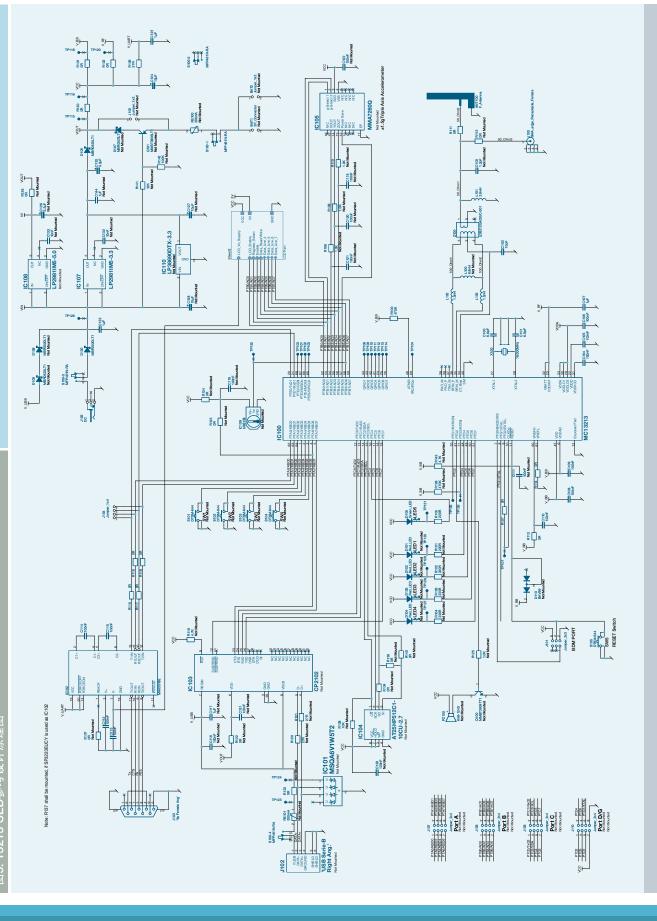

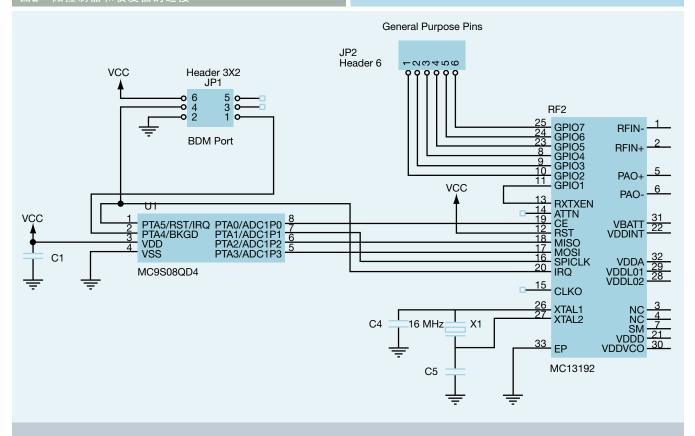

#### 感应、监控和控制子系统原理图

感应、监控和控制子系统的参考设计原理图经常用作 应用的基础,并据此来提出具体的设计要求。作为 采用单封装系统(SiP)方案的设计示例,下图给出了飞思 卡尔1321x-SRB传感器参考电路板的原理图,它包括 1321XDSK(开发人员入门工具套件)、1321xNSK(网络入 门工具套件)和1321xEVK(ZigBee评估工具套件)。 1321x-SRB包括飞思卡尔MMA7260Q三轴加速传感器, 与入门工具箱一起使用,能帮助您在几分钟内构建工作网 络。电路板提供了参考应用设计,它是感应应用开发的起 点(见图5)。

您还可以选择使用独立的收发器和MCU,以获得更多的 设计灵活性。例如,下面的方框图是飞思卡尔13192 传感器应用参考设计,用于感应、监控和控制子系 统。我们在13192DSK-A0E(开发人员入门工具套件)和 13192EVK-SFTE(评估工具套件)开发套件中提供了基于 此设计的完整电路板(图4)。

您可以从网站下载上述参考设计的支持文档。下载文件夹 包括原理图、物料单、印制板文件和实现整个参考设计 所需的其他文档。

#### 飞思卡尔用于感应、监控和控制应用的无线网络方案

我们为那些希望在最终产品中建立一个新范例的数字工程 师提供了一套理想的解决方案。该电路板能够满足上面 提到的实现一个低成本无线网络的基本要求。

示例产品包括:

- RF调制解调器或收发器解决方案(简化MAC、802.15.4 MAC和ZigBee),可与各种MCU一起使用(MC1319x和 MC1320x收发器系列与HCS08和ColdFire MCU系列 一起使用)。

- 收发器集成方案(简化MAC、802.15.4 MAC和ZigBee), 采用MCU单封装系统(SiP)方案(MC1321x SiP系列)

- 模拟器件

- 传感器器件

为了实现简便易用的ZigBee和其他低成本、低功率无线 网络,飞思卡尔为您提供大量参考设计、应用笔记、硬件 开发工具和软件设计工具。如需了解更多产品信息, 请登录我们的网站:www.freescale.com/zigbee。

Pattye Brown是飞思卡尔半导体的技术营销工程师和渠道营销联络人,在公司已经任职23年。她拥有工业工程学士 学位和工商管理及市场营销硕士学位。

### Martin Mienkina博士

## 适用于成本敏感性应用的

## 微控制器

当您仔细观察我们的周围时,你会发现生活中电器的使用 无处不在。洗衣机、冰箱、洗碗机、吸尘器、电动工具、 室内加热控制系统、汽车座椅定位、动力方向盘和刹车、 空调、吊扇、计算机等等,在工作场所包含电子器件的 设备就更多了。

每台设备都包含电气驱动部分和辅助电子部分,它们以 不同的效率消耗著能量。近来全球范围内对环境友好以及 节能的关注让工程师们面临著不小的压力,他们要在设计 中保持尽可能高的效率,同时还要得到低成本、简洁而且 可靠的方案。目前有一些对能源效率具有正面影响的 因素,但其中一些最有效的因素还是使用先进的电机和 功率器件,开发出新颖的电机控制技术,并充分利用电子 驱动装置特有的待机和唤醒状态。要成功地利用这些 因素,还要达到多个国家的标准,必须采用智能微控制器 来管理电机和辅助电子装置。

飞思卡尔在广受欢迎的多管脚HCS08微控制器系列 基础之上,推出一款先进的HCS08少管脚器件, 即MC9S08QG系列。

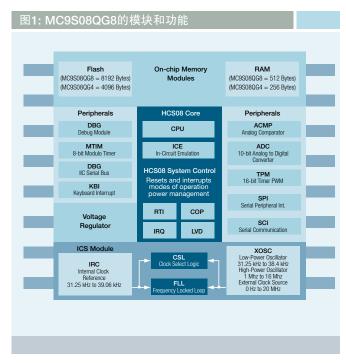

## 概览

MC9S08QGx (QG)微控制器具有丰富的功能,同时具有 一系列小型封装,因而成为设计人员的理想选择,特别是 在开发现代电子设备,同时还必须考虑低功耗、电路板 空间和系统成本等问题时。QG系列的高性能体现在它 具有低功耗率、可靠的闪存、更高的模拟精度、多种串行 通信和增强的运动控制功能。请参见图1。

#### HCS08处理内核

这些微控制器是以先进的制作工艺生产的。因此,当电压 高于2.1V时,它们的运行频率可高达20 MHz(10 MHz 总线); 当电压低于2.1V时, 其运行频率也可达16 MHz (8 MHz总线),所以它在低电压时也能提供高性能。 HCS08内核与HC08内核的指令集相同,但增加了对 进入后台调试模式(BGND)的支持,因而可以充分利用 集成的片上后台调试控制器(BDC)与在线仿真(ICE)的 优势。

BDC含有一系列无干扰指令,可以在不中断CPU的情况下 读/写片上内存。ICE包含强大的分类和跟踪单元,可以 设置断点、触发选项并捕捉软件执行流程中的改变。

调试过程仅仅使用芯片的一个BKGD引脚,通过单线的 通信接口就能执行。在完成调试过程后,用户应用程序 可以将BKGD引脚当作额外的通用I/O脚使用。这样用户 通过使用MC9S08QG的片上调试功能,省去了昂贵的 仿真工具,同时也无需牺牲有效的管脚数,从而进一步 降低开发总成本。

在电池供电的应用领域中,关键的要求是最大限度地减少 微控制器的功耗,同时维持应用必需的处理能力。为了满足 这些要求,在MC9S08QG器件中仔细地部署了专门的"等待" 模式以及另外三个低功率"停止"模式(停止3、停止2和停止1)。 这些低功率模式在下文中都称为"省电"模式。

#### 时钟源电路

时钟源分配是所有系统设计中的关键部分。MCS08QG系列的内部时钟源(ICS)模块提供多种时钟源选择,可形成非常灵活又经济高效的方案,特别是对于少管脚数的器件而言。它由锁频环(FLL)、内部参考时钟(IRC)、外部振荡器(XOSC)和时钟选择逻辑(CSL)等模块组成。

FLL将参考频率提高到512倍,它只采用简单的数字逻辑 技术,因而与PLL不同,它无需另外的外部元器件。

IRC是完全可调整的,既可用作FLL的参考时钟,也可直接用作CPU和总线时钟的时钟源。其调整精度典型值可达0.1%。调整频率范围为31.25 kHz到39.06 kHz。

XOSC参考时钟可配置成3种模式。第一种模式是低频振荡器模式,目的是与32 kHz~38.4 kHz的晶振体或谐振器一起使用。第二种是高频振荡器模式,可以与1 MHz~16 MHz晶振或谐振器连接。最后一种振荡器模式是特别定制的,可以与高达20 MHz的外部有效时钟一起使用。

CSL选择并划分时钟源,供CPU和其他微控制器模块使用。可以选择FLL、IRC或XOSC时钟源来驱动CPU和总线。输出频率可以在任何时间除以2、4或8,以降低CPU和外围设备的执行速度,从而即使不把微控制器切换到省电模式,也能延长电池的寿命。

#### 片上内存

该系列提供两种闪存/RAM内存配置。设计人员既可以选择具有8 KB闪存、512B RAM的MC9S08QG8,也可以选择4 KB闪存、256B RAM的MC9S08QG4。

这一闪存技术基于飞思卡尔的第3代(0.25µ)技术,在整个温度范围(-40°C至+85°C)上,电压降到1.8V时仍可编程。闪存可以逐字节编程,并可逐页擦写(512字节)一在室温下可以达到10次万次的闪存写/擦周期,在所有温度和电压工作条件下也能确保1万次周期。闪存数据保持期限设计为至少15年,根据系统情活的不同可以长

很多。闪存的分区大小适当,又可超快编程,所以让用户 能模拟EEPROM使用。

MC9S08QG含有专门设计的电路,可防止对闪存和RAM存储器的非授权访问,从而可防止潜在的应用代码盗用。这种实现机制具有很高的安全等级,一旦器件由这种机制加密,那么根据其设计,只有输入正确的8字节后门对比密钥后才能解锁。重要的非易失性数据和代码(如应用常数和引导程序)也可以选择性地加以保护,防止发生意外的写入和擦除动作。

#### 高级计时器

MC9S08QG系列有两个独立的计时器模块。这些模块可用于定时、机械运动控制和/或软件任务调度。

第一个模块是双通道可编程16位定时器/PWM模块 (TPM)。TPM的每个通道都能独立配置为输入捕获、输出比较和带缓冲的边沿对齐或中心对齐脉宽调制 (PWM)。支持的两种PWM模式,特别是中心对齐模式,使系统具备了强大的运动控制功能。此外,定时器的寄存器的处理方式与16位的占空比更新操作是协调一致的,这样就避免了产生意外的脉冲宽度。

第二个定时器模块是8位模数定时器中断模块(MTIM), 它具有多个可能的输入时钟源和一个可编程的中断功能。 定时器即可以自由运行,也可以作为模数定时器运行, 可以在定时器溢出时产生各种周期的中断。

#### 模拟电路

MC9S08QG系列集成了一个8通道、10位模数转换器 (ADC),能够为所有带模拟输出信号的传感器提供简单的 接口。ADC可以在选定的通道上执行单次或连续转换。 转换可由软件或实时中断(RTI)启动。ADC可以由总线 时钟、总线时钟/2或ADC内部时钟源提供时钟。此外, ADC还可配置为将测量电压与给定的上限或下限值连续 进行比较,并且分别在超过下限或上限值的瞬间产生 中断。要记住的重要一点是,当选择ADC内部时钟作为 ADC时钟源时,可以使用该功能将微控制器从省电模式 唤醒。

该器件还包含模拟比较器(ACMP)模块,用来比较两个 模拟输入电压或把一个输入电压与内部带隙参考进行 比较。此模块将其输出引到某些其他片上外围设备上, 或引到外部管脚上,这样其他片上外围设备或外部系统 就能够对比较器输出信号进行连续监控和后处理。比较器 中断可选择由比较器输出的上升沿或下降沿触发,或者 二者都可触发。这类中断可以使微控制器退出省电模式。

该器件还带有一个温度传感器,其输出连接到一个保留的 输入通道(AD26)上。其设计意图是不用消耗任何模拟输入 通道,就能让用户测量硅芯的温度。此外,内部带隙参考 电压和电源电压也能用同样的方法进行测量,从而可分别 检查片上带隙电压稳压器和外部电源是否工作正常。

#### 通讯模块

MC9S08QG8 (8脚和16脚)和MC9S08QG4(16脚)器件有 3个通信模块,给设计人员提供了多种选择以满足其应用 的需求。

串行通讯接口(SCI)提供标准的UART通讯,在微控制器 和其他远程设备之间提供全双工异步和不归零(NRZ)串行 通讯。

串行外设接口(SPI)可与其他微控制器或外围设备, 如ZigBee收发器(MC13192)、步进电机驱动器 (MC33976)、各种I/O扩展器和智能多媒体卡控制器等, 建立高速主机(高达5Mbit)或从机(高达2.5Mbit)的SPI 连接。

集成电路互连(I2C)提供了一种多个设备之间的通信 方法。该接口设计为以最大总线负载运行时,速度可高达 100kbps。它设计人员提供了一种简单的接口,可连接 LCD控制器、RTC、DAC和其他外部EEPROM。

### MC9S08QG的型号与封装选择

MC9S08QGx器件将飞思卡尔的HCS08产品系列扩展到 少管脚数领域,并提升了低电压下的功能。最初有10种 不同的器件。它们的不同在于片上闪存、RAM存储器的 数量、管脚数、封装选项等。在所有类型的封装中, 8 KB闪存和4KB闪存的器件都是管脚兼容的。表1列出了 MC9S08Q系列中的各个器件。

#### 开发工具

HC(S)08微控制器的CodeWarrior工具链完全支持 MC9S08QG微控制器的高效、快速编程。对于16KB 以下的代码容量,可提供免费的特别版FastTrack CodeWarrior工具,包括高效C编译器、调试器、连接器、 汇编器、仿真器、集成开发环境(IDE)及其他组件,可帮助 开发人员轻松、快速、毫无顾虑地完成应用开发。

每种嵌入式应用都需要进行初始化及使用片上外围设备。 正是因为这个要求,飞思卡尔已经授权使用Processor Expert™自动代码生成器,并将其集成到CodeWarrior 工具中。Processor Expert自动代码生成器极大地简化了 应用开发,加快了开发速度。此外,它使得用户即使对 片上外围设备的结构没有深入的了解,也能对它们进行 编程。

为了能够在没有拿到最终应用硬件时就开始进行开发, 飞思卡尔推出了DEMO9S08QG8评估模块。该模块通过 集成的USB-BDM调试接口和各种片上外围设备编程示例 软件,实现了简单、快速的应用开发。

#### 典型应用

MC9S08QG系列现在正越来越广泛地应用于小家电、 电动工具、智能中继、小型工业设备、汽车电子、灯光 调节设备、手持工具、无线通信、计量器、热量计和报警 应用中,这里列出的只是冰山一角。

应用实例包括使用三相直流无刷(BLDC)、直流有刷(DC) 和通用(AC)等类型的电机。当采用MC9S08QGx微控制 控制这些电机时,能够以高能效实现高性能。

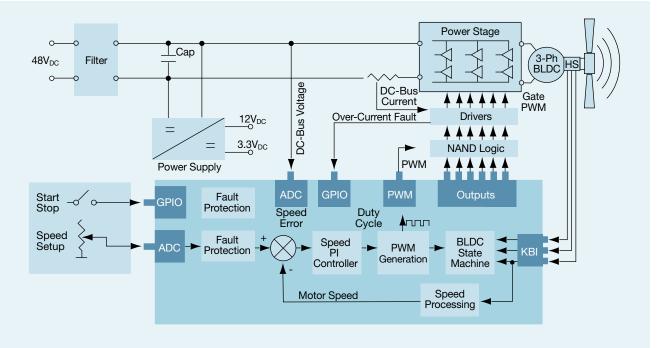

首先,图2显示的是成熟的BLDC驱动概念。它实际上是 一个速度闭环的BLDC驱动,采用低成本的霍尔传感器 作为位置和速度反馈。MC9S08QG4芯片在这类驱动中的 优势在于能维持最高水平的元器件集成度,并达到运动 控制外围设备的最佳使用状态。该驱动要求在外部硬件中 采用"与非门逻辑",以便能自动地将芯片的PWM输出扩展 为三相功率平台的驱动能力。

BLDC驱动概念可应用于白色家电、高端泵机、风扇和 其他需要以低成本实现高可靠性和效率的应用中。

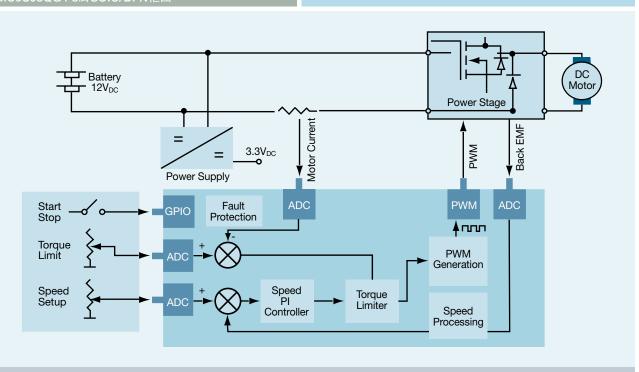

其次,图3介绍了专用干电池供电驱动的控制机制。这个 控制概念描述了如何将微控制器成功地集成到有刷直流

电机的控制应用中。驱动此类应用的微控制器应该能轻松 实现多种高级的驱动控制技术,如无传感器闭环速度控制 及转矩控制。

这个驱动概念可用于控制无绳改锥、电池供电钻头、 搅拌机、电动牙刷、玩具车或者甚至高尔夫电动车等 应用中的有刷直流电机。

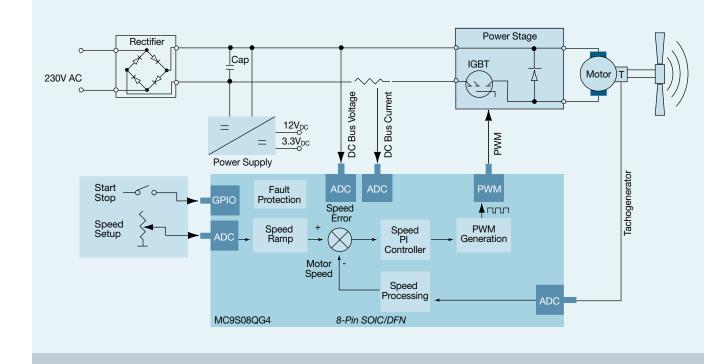

最后,通用电机驱动的实现如图4所示。这个应用代表了 基于MC9S08QG4微控制器的低成本、闭环通用电机断续 控制驱动系统。PWM技术用于调整电机上施加的电压。 PWM占空比周期的调制使加在电机上的平均电压值可以 改变。与相位角驱动相比,断续驱动对输入电源进行 整流。然而,它的优势在于效率更高、噪音更低而且 EMC一致性也更好。

| 表1: MC9S08QG系列· | 中的不同器件                        |                          |                           |                           |  |  |

|-----------------|-------------------------------|--------------------------|---------------------------|---------------------------|--|--|

|                 |                               |                          |                           |                           |  |  |

| 功能              | MC9S                          | 08QG8                    | MC9S08QG4                 |                           |  |  |

| 封装              | 16脚                           | 8脚                       | 16脚                       | 8脚                        |  |  |

| 闪存              | 8                             | KB                       | 4                         | KB                        |  |  |

| RAM             | 51                            | 2B                       | 25                        | 56B                       |  |  |

| XOSC            | 是                             | 否                        | 是                         | 否                         |  |  |

| IRC             | <del>,</del>                  | E                        | ;                         | 是                         |  |  |

| ICS             | <del>,</del>                  |                          | ;                         | 是                         |  |  |

| ADC             | 8通道                           | 4通道                      | 8通道                       | 4通道                       |  |  |

| ACMP            | <del>,</del>                  | E                        | 是                         |                           |  |  |

| DBG和ICE         | ;                             | 是                        |                           | 否                         |  |  |

| IIC             | ;                             | 是                        |                           | 是                         |  |  |

| IRQ             | <del>,</del>                  |                          | 是                         |                           |  |  |

| KBI             | 8脚                            | 4脚                       | 8脚                        | 4脚                        |  |  |

| MTIM            | <del>,</del>                  |                          | 是                         |                           |  |  |

| SCI             | 是                             | 否                        | 是                         | 否                         |  |  |

| SPI             | 是                             | 否                        | 是                         | 否                         |  |  |

| TPM             | 2通道                           | 1通道                      | 2通道                       | 1通道                       |  |  |

| I/O脚            | 12 I/O<br>1个单输出,<br>1个单输入     | 4 I/O<br>1个单输出,<br>1个单输入 | 12 I/O<br>1个单输出,<br>1个单输入 | 4 I/O<br>1个单输出,<br>1个单输入  |  |  |

| 封装类型            | 16 PDIP<br>16 QFN<br>16 TSSOP | 8DFN<br>8 SOIC           | 16 QFN<br>16 TOSSP        | 8 DFN<br>8 PDIP<br>8 SOIC |  |  |

#### 图2: MC9S08QG4 16脚QFN/TSSOP框图

通用电机概念可用于洗衣机、手持工具、真空吸尘器、 洗碗机、单相和变速驱动中,还可用于低成本、中功率的 可变电压输出应用。 现在,新的家用电器(IEC 60730)国际安全标准提倡使用独立时钟的看门狗定时器(COP)。这种定时器不仅在出现软件错误(软件堆栈损坏、程序计数器损坏、从中断或子程序返回出错以及死循环等)时,而且在时钟电路无法

#### 图3: MC9S08QG4 8脚SOIC/DFN框图

#### 图4: MC9S08QG4 8脚SOIC/DFN框图

正常工作的情况下都能将系统置于确定的复位状态。这个安全功能在MC9S08QGx微控制器上得到完全实现,因而使它们可以根据安全性和新的国际标准应用于家用电器。

#### 结论

最新推出的MC9S08QG微控制器系列,其处理内核、 片上外围设备、节电功能和开发工具等,构成了能源 效率敏感控制应用的理想解决方案。采用飞思卡尔的 MC9S08QGx微控制器系列,不仅开发的费用可明显 减少,最终生产阶段的成本也可大幅下降。在开发阶段, 一些高级调试功能,包括CodeWarrior全功能工具链和 Processor Expert工具包等都是免费赠送的。在生产 阶段,内部时钟源模块、模拟电路和EEPROM模拟则减少 了对诸如晶振或谐振器、模拟比较器、串行EEPROM这样 的外部器件的需求,否则这些外部器件都是印制电路板上 必不可少的。 飞思卡尔意识到,只有切实地对新技术进行投资,并且 持续不断的以更低的价格开发出更智能、更高速的器件, 我们才能维持在8位微控制器全球市场的领先地位(Gartner Dataquest,2004)。因此,飞思卡尔的工程师一直在不断 地扩展已得到广泛应用的HCS08微控制器系列。未来的 产品系列有望扩展现有的少管脚和多管脚数的产品, 进一步提高性能、增加片上外围设备的种类。

Martin Mienkina分别于1992和1997年获得Zilina大学工学硕士和电子工程博士学位。他曾在Trinec Steel & Iron Works Ltd公司工作过一段时间,负责设计与钢铁和轨道生产有关的现代控制系统。2000年,他加入飞思卡尔(捷克)系统中心,担任系统应用工程师,主要负责电机控制应用、驱动软件及数字信号控制器。Mienkina博士负责飞思卡尔在东欧地区的市场技术活动,工作的重点是新需求拓展和新产品开发。

#### Juan Cazares

## 用低端微控制器

## 构建简单的无线应用

无线通信是我们日常生活的一部分。在办公室、学校或 家庭等场所,我们都在接触无线通信设备,如笔记本电脑、 打印机、摄像头、手持设备和照明控制器等。这些设备的 复杂程度与它们执行的任务类型有关。

其中许多无线应用采用小型微控制器和少量代码执行简单 的任务。本文将讨论用于家庭自动化的无线应用。该应用

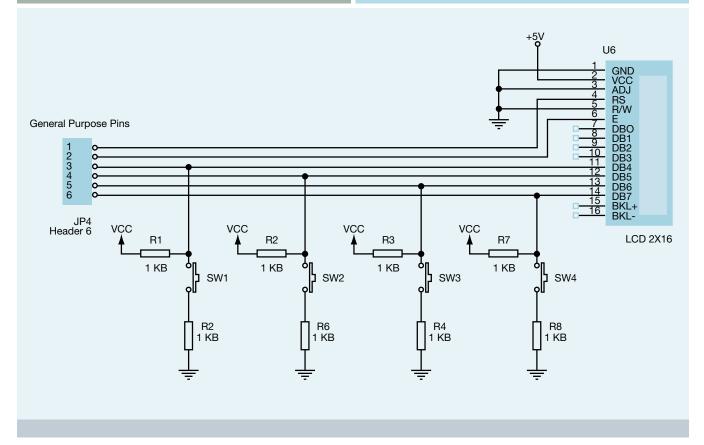

图1: 无线控制器框图 Background Debugger Programmer Interface Parallel LCD LCD Control 4 LCD MC1319x Low-End Transceiver's GPIO's Microcontroller (MC9S08QD4) Transceiver Transceive Family Control Multiplexed Bus 4 Button Inputs Keyboard

是无线控制器,设计为低成本的应用,只采用了三个电子 元件:一个低端微控制器(MC9S08QD4)、一个RF收发器 (MC13192)和一个2×16的LCD。其他需要的元器件为 电阻和按键之类的无源器件。

图1是无线控制器框图。用来在收发器和微控制器之间 交换数据的接口为串行外设接口(SPI)。该接口可以读写 收发器的配置、状态和控制寄存器。SPI接口还可以读写 位于收发器内部的RAM,用于通过RF发送和接收数据。

另一个用于收发器和微控制器间通信的信号是中断请求 (IRQ)信号。IRQ脚由收发器进行处理。当收发器的状态寄 存器发生变化时,IRQ脚会产生下降沿跳变。IRQ产生后,微 控制器要做的第一件事就是读取状态寄存器,确定产生中 断的特定事件。表1介绍的是微控制器管脚分配。

#### 图2:微控制器和收发器的连接

| 表1:引脚功能介绍 |                  |             |          |            |                |

|-----------|------------------|-------------|----------|------------|----------------|

| 引脚<br>编号  | MCU<br>引脚名       | 类型          | 引脚<br>编号 | 收发器<br>引脚名 | 类型             |

| 1         | PTA5/<br>RST/IRQ | 数字输入        | 20       | IRQ        | 数字<br>输出       |

| 2         | PTA4/<br>BKGD    | 编程和调试<br>接口 |          |            |                |

| 5         | PTA3/<br>KBI1P3  | 数字输出        | 17       | Mosi       | 数字<br>输入       |

| 6         | PTA2/<br>KBI1P2  | 数字输入        | 18       | Miso       | 数字<br>输出       |

| 7         | PTA1/<br>KBI1P1  | 数字输出        | 16       | SPI时钟      | 数字<br>时钟<br>输入 |

| 8         | PTA0/<br>KBI1P0  | 数字输出        | 19       | 芯片使能       | 数字<br>输入       |

收发器要切换运行模式(接收、发送、半休眠、休眠或空闲)还需要另外一个信号。该信号称为RXTXEN。 微控制器的所有通用引脚用来管理其他一些信号, 如表1所示。RXTXEN信号由微控制器的GPIO1进行 处理。表2描述了控制RXTXEN所需的连接。

| 表2:RXTXEN连接 |            |      |          |            |          |  |

|-------------|------------|------|----------|------------|----------|--|

| 引脚<br>编号    | MCU<br>引脚名 | 类型   | 引脚<br>编号 | 收发器<br>引脚名 | 类型       |  |

| 11          | GPIO1      | 数字输出 | 13       | RXTXEN     | 数字<br>输入 |  |

表1和表2显示了让收发器开始工作所需的最低硬件要求。参见图2的建议原理图。按照上述的方式连接硬件,可以配置收发器,并发送和接收数据。同时也可以通过SPI配置收发器提供的定时器和GPIO引脚,将其用于其它的目的。

如图2所示,收发器有7个GPIO引脚。其中一个引脚用来驱动RXTXEN信号,其余六个可用于用户的应用。在本推荐应用中,收发器提供的定时器和GPIO引脚用于驱动四个按键和一个2×16的LCD。

### 图3:无线控制器的连接

这里推荐的的无线控制器应用原理图分作两部分。第一部分 包括开发各种应用所需的基本平台(见表1、表2和图2)。 第二部分介绍无线控制器应用的连接(见图3)。

图3表明,该应用需要6条线路来驱动LCD,另外还需要 4条线路来驱动4个按键。这一共有10条线路,而这10条 线路必须由仅有的6个GPIO引脚来驱动。为了实现这一 目的,LCD的4条数据线和4个按键必须多路复用。表3 介绍了各个GPIO引脚的性能。

| 表3:应用引脚描述 |         |  |  |  |  |

|-----------|---------|--|--|--|--|

| 收发器GPIO引脚 | 功能      |  |  |  |  |

| GPIO2     | RS      |  |  |  |  |

| GPIO3     | E       |  |  |  |  |

| GPIO4     | DB4/SW1 |  |  |  |  |

| GPIO5     | DB5/SW2 |  |  |  |  |

| GPIO6     | DB6/SW3 |  |  |  |  |

| GPIO7     | DB7/SW4 |  |  |  |  |

如表3所示, GPIO4、 GPIO5、 GPIO6 和GPIO7用来 驱动LCD的四条数据线以及四个按键。四个GPIO引脚 必须配置成将数据送到LCD的输出,同时这些引脚还必须 配置为读取按键电平的输入。

该应用使用LCD来显示不同的菜单,如当前温度、定时 设置和设备超出范围等。

四个按键用来设置希望的温度、设置风扇定时时间、以及 在菜单之间的导航。表4介绍了各个按键分配的功能。

| 表4:按键功能 |        |  |  |  |  |

|---------|--------|--|--|--|--|

| 按钮      | 功能     |  |  |  |  |

| SW1     | 显示定时菜单 |  |  |  |  |

| SW2     | 减少数值   |  |  |  |  |

| SW3     | 增加数值   |  |  |  |  |

| SW4     | 接受     |  |  |  |  |

当应用开始时,风扇总是处于关闭状态。必须按SW2或 SW3按键才能打开风扇。风扇打开后,LCD上会显示当 前温度。一旦风扇打开,可以分别使用Sw2和Sw3来降低 或增加温度。最高温度可设置为60度。当风扇关闭时, SW1和SW4起作用。

可以设置定时时间来自动关闭风扇。定时时间在1~99分钟 之间。如果没有设置定时时间,风扇永远不会自动关闭。

要设置希望的定时时间,步骤是:

- 打开风扇。如果风扇处于关闭状态,就不能设置定时时间。

- 按SW1。这样会在LCD上显示定时菜单。

- 按SW2或SW3来减少或增加希望的定时时间。

- 按SW4来接受新的定时时间。

- 一旦接受新的定时时间后,LCD上会再次显示当前 温度。

该应用使用收发器提供的两个定时比较器,一个用来生成定时时间,另一个用来读取按键电平。

定时比较器1用来生成长度为1分钟的时间基准。该时间基准可生成1至99分钟的定时时间。

定时比较器2用于每100毫秒读取一次按键电平。为了读取按键电平,必须将GPIO4、GPIO5、 GPIO6和GPIO7 配置为输入。该应用将所需的GPIO引脚配置为输入,读取输入值,然后将这些GPIO引脚再配置为输出。

每次用SW2或SW3按键修改了温度后,系统会采用一个简单的协议将当前温度发送到加热-制冷系统。

#### 结论

这里仅使用了一个8脚封的装微控制器,再加上很少的一些硬件资源,说明开发无线应用时并不一定总是需要高性能的微控制器。收发器需要有一些引脚,以便能用于从低端到高端的几乎任意微控制器上。最后,使用收发器提供的定时器和GPIO引脚能减少微控制器资源的使用,如GPIO引脚和定时器之类的模块。同时还必须记住的是,低端微控制器能够完成复杂的无线网络要求的一些简单任务,从而降低了整个解决方案的成本。

### 参考资料

www.freescale.com/files/rf\_if/doc/ref\_manual/ MC13192RM.pdf

www.freescale.com/webapp/sps/site/overviewjsp?code= ZIGBEE\_REFERENCEDESIGN\_HOME

Juan Cazares是从事涉及SMAC协议栈的无线解决方案的应用工程师。他拥有电子工程学位,专攻控制和仪器领域。在加盟飞思卡尔前,Cazares曾先后担任过天然气和汽油测量设备的硬件及软件设计师。

### Gary Streber

# 共同创建解决方案的 飞思卡尔设计联盟计划

虽然高科技产品、市场和企业一直在不断发展,但是更快 速地将最好的方案推向市场的目标始终保持不变。更好、 更快、更便宜依然是当前的趋势。另一方面,面对起伏不 定的经济形势,确定合理的规模并获得需要的技术及核心 竞争力,并帮助您的客户适时推出产品,已成为比以往更 重的负担。

飞思卡尔拥有全球最具竞争力的技术和产品,以及行业内 最好的生态系统,其中不乏顶级的专家,掌握著最新的 应用硬件和软件专业技术。但是,我们自己内部可能并 不拥有所有您需要的技术和资源,可以让您的最终产品 讲入市场。

我们实施设计联盟计划(DAP)的目的是使飞思卡尔以及 我们的方案系统可以帮助您实现目标。DAP拥有450多名 第三方成员,他们在产品和应用的开发方面拥有不同的 经验。从概念到最终产品,他们可以让您在任何阶段开始 介入,帮助您的产品进入市场。我们还实施了工具联盟 计划(TAP),拥有约200名成员,他们为您或您的合作伙伴 提供用于开发方案所需的最终硬件和软件工具。同时, 大学联盟计划也已实施,以确保未来的设计团队可以跟上 飞思卡尔工具和产品的发展潮流。

为了证实DAP成员的可信度,我们采取一系列步骤来验证 列于目录中的飞思卡尔经验和应用。虽然在很多情况下 该目录也包括推出新产品和创造新应用的工作,但是, 列表内容只是飞思卡尔所有工作的一小部分。

许多DAP成员都是按纯粹的受雇设计结构,或不重做工程 (NRE)费用结构操作,为客户提供完整的设计或生成知识 产权(IP)。有的人创建并拥有知识产权,将其许可给他人 使用或作为设计的一部分来改善设计流程。同时,借助 他们丰富的应用知识和各种不同的市场知识,DAP成员 可为每种设计提出不同的观点,从而最大限度地挖掘市场 潜力。

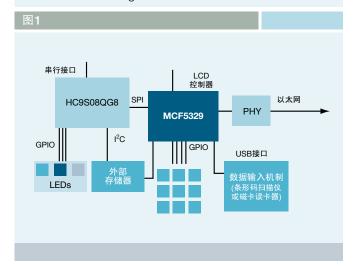

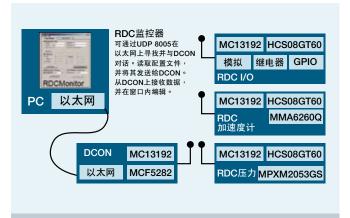

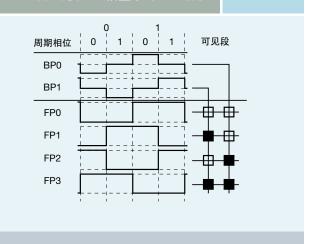

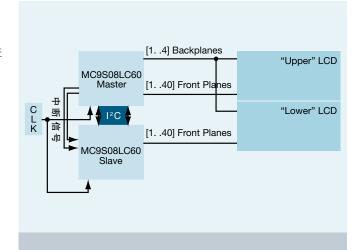

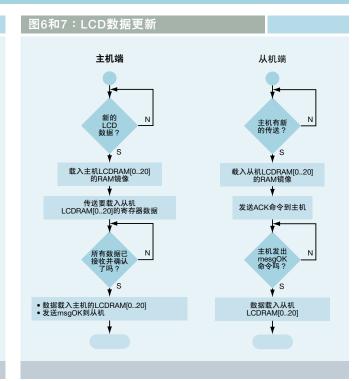

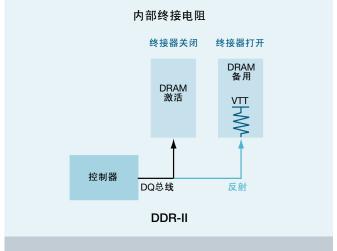

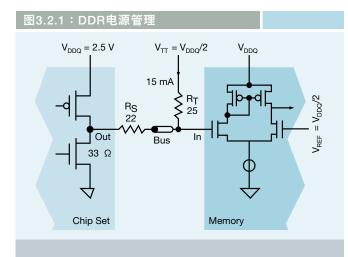

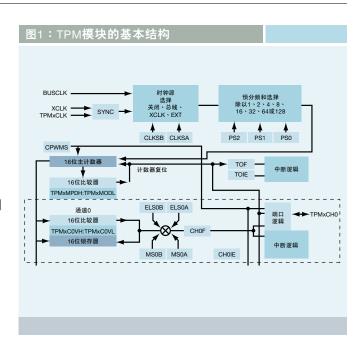

Indesign LLC与飞思卡尔地区技术应用中心通力合作, 使用32位ColdFire MCF5329嵌入式控制器和 MC9S08QG 8位微控制器设计了这个POS参考设计 (图1)。如需了解有关Indesign LLC的更多信息, 请访问www.indesign-llc.com