# 第三章 原理图输入法设计时序逻辑电路

时序逻辑电路是数字逻辑电路中最重要的一类，一个时序逻辑电路包含组合逻辑网络和存贮单元两大部分，其中组合逻辑网络部分可用译码器、数据选择器或其他组合网络模块实现，而存储单元部分则用计数器、移位寄存器或通用寄存器等实现。本章将以一个简易数字钟的分钟和秒部分为例学习如何通过 MAX+plus II 软件的图形编辑器，利用原理图库中元件进行时序逻辑电路的设计输入，如何用波形编辑器进行输入激励波形输入，再用 MAX+plus II 的模拟器和时延分析器进行逻辑验证和分析。并学习用层次显示工具进行自顶向下的设计。

## 3.1 设计输入和编译

通过图形编辑器进行时序逻辑电路设计输入的过程和第二章中组合逻辑设计输入的过程是一样的。一个简易数字钟的分钟和秒部分都可以认为是一个模 60 计数器，而模 60 计数器可以通过两个模 10 计数器采用同步置 0 法加上适当的反馈完成。

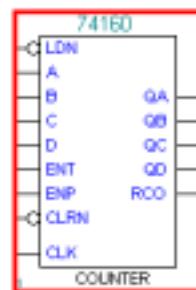

图 3.1 74160 的元件符号

表 3.1 74160 的功能表

| 输入  |     |      |     |     |   |   |   |   | 输出 |    |    |    |     |

|-----|-----|------|-----|-----|---|---|---|---|----|----|----|----|-----|

| CLK | LDN | CLRN | ENP | ENT | D | C | B | A | QD | QC | QB | QA | RCO |

| X   | X   | L    | X   | X   |   |   |   |   | L  | L  | L  | L  | L   |

|     |     | L    | H   | X   | X | d | c | b | a  | d  | c  | b  | a   |

|     |     | H    | H   | X   | L |   |   |   |    | QD | QC | QB | QA  |

|     |     | H    | H   | L   | X |   |   |   |    | QD | QC | QB | QA  |

|     |     | H    | H   | H   | H |   |   |   |    | L  | L  | L  | L   |

|     |     | H    | H   | H   | H |   |   |   |    | L  | L  | L  | H   |

|     |     | H    | H   | H   | H |   |   |   |    | L  | L  | H  | L   |

|     |     | H    | H   | H   | H |   |   |   |    | L  | L  | H  | L   |

|     |     | H    | H   | H   | H |   |   |   |    | L  | H  | L  | L   |

|     |     | H    | H   | H   | H |   |   |   |    | L  | H  | L  | H   |

|     |     | H    | H   | H   | H |   |   |   |    | L  | H  | H  | L   |

|     |     | H    | H   | H   | H |   |   |   |    | H  | L  | L  | L   |

|     |     | H    | H   | H   | H |   |   |   |    | H  | L  | L  | H   |

$$* \quad RCO = QD \& QA \& ENT$$

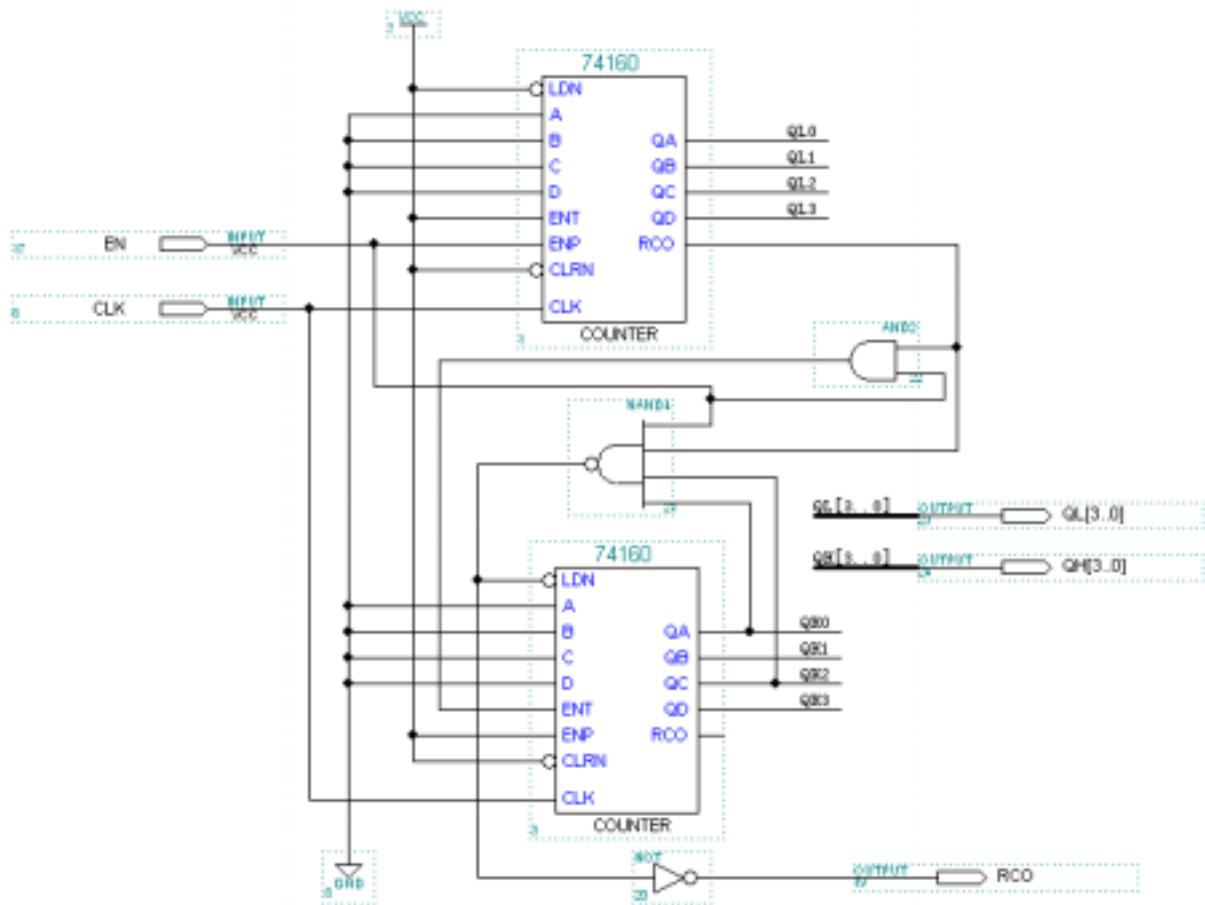

和组合逻辑电路的设计输入一样，先要建立项目和图形输入文件（示例中两个文件名用的是 MOD60），再调入元件符号。由于模 60 计数器的主体部分是两个模 10 计数器，这里我们可以调用两个 74160 同步 10 进制计数器元件来实现。元件 74160 位于 mf(宏功能库) 中，元件符号如图 3.1 所示，功能表如表 3.1 所示。由功能可以看出，ENT、ENP 是 74160 的使能端，高电平有效；LDN 是同步置数端，低电平有效；CLRN 是异步清零端，低电平有效；RCO 是进位输出端。

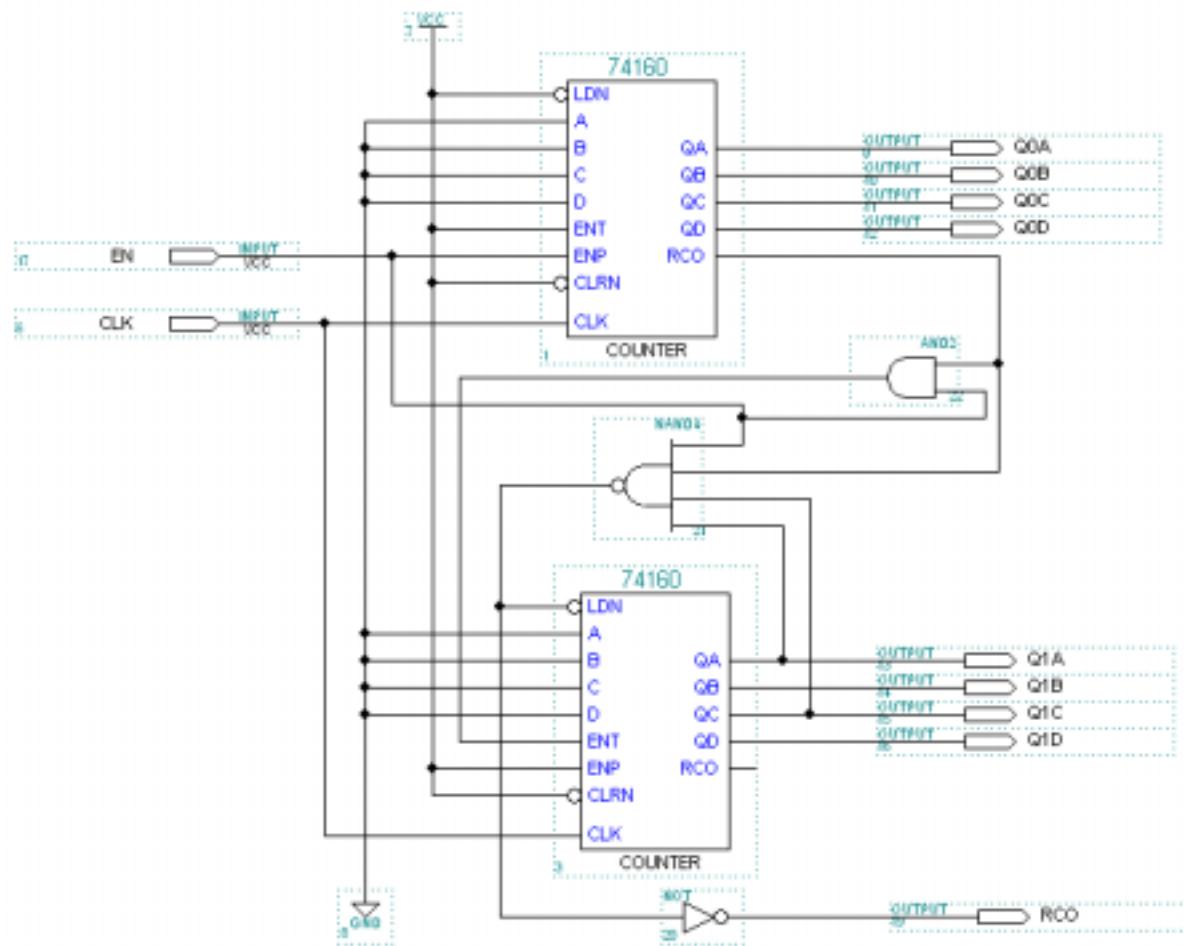

这里我们采用同步置 0 法来实现模 6 计数器，所以需要调入 1 个 3 输入与非门进行反馈。为了使 74160 正常工作，可以调入元件 VCC 来实现强行置高电平、元件 GND 来实现强行置低电平，也可以将相应的管脚悬空，此时管脚采用缺省电平值。对于 74160，LDN、CLRN、ENT、ENP 的缺省值为 ‘1’，A、B、C、D 的缺省值为 ‘0’。为了便于以后实现层次化设计，我们还将低位的 ENT 端子作为输入端，RCO 作为进位输出端。最终的电路图如图 3.2 所示。

图 3.2 模 60 计数器电路图

设计输入完成后，选择“File”菜单下的“Save & Compile”菜单项，打开编译器开始编译。

## 3.2 设计项目校验

在编译完全通过以后，就可以利用 MAX+plus II 软件提供的模拟器进行设计校验了，具体步骤如下：

### 一、建立输入激励波形文件（也称模拟器通道文件 SCF）：

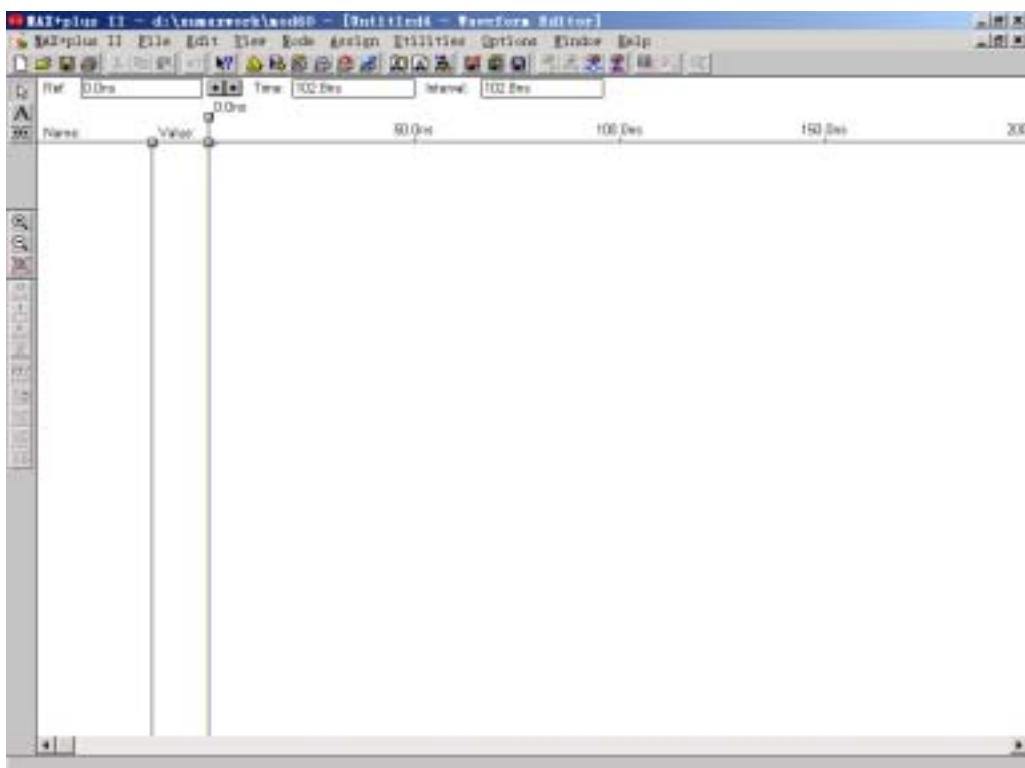

- 1、单“File”中选择“New”打开新建文件类型对话框，如图 2.2 所示。选择“Waveform Editor File(.scf)”项后选择“OK”，则出现如图 3.3 所示的波形编辑器窗口。

图 3.3 波形编辑器窗口

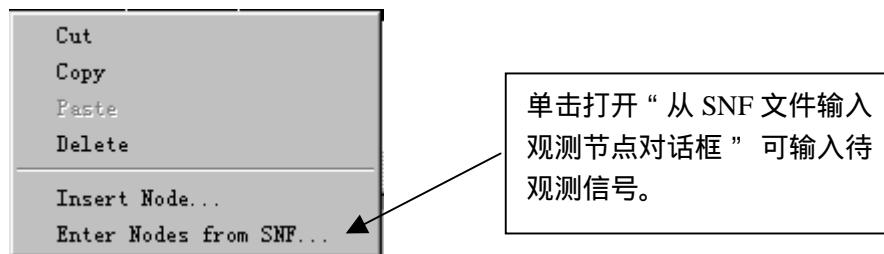

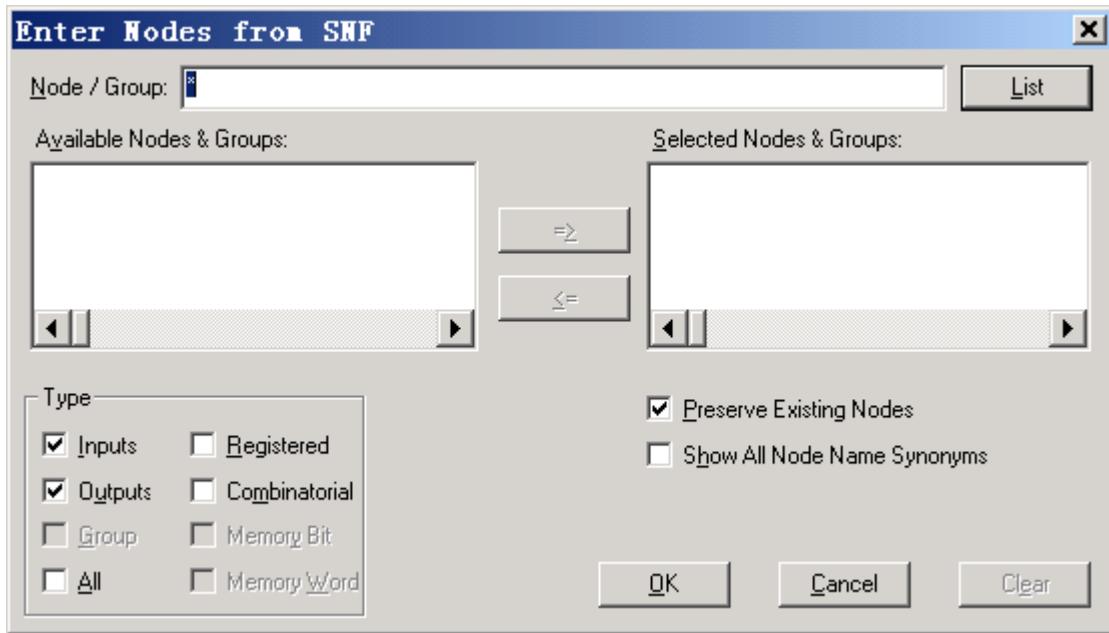

- 2、编辑器窗口的 Name 栏空白处单击鼠标右键，出现如图 3.4 所示菜单。在该菜单中选择“Enter Nodes from SNF...”项，可打开如图 3.5 所示对话框。

图 3.4 右键菜单

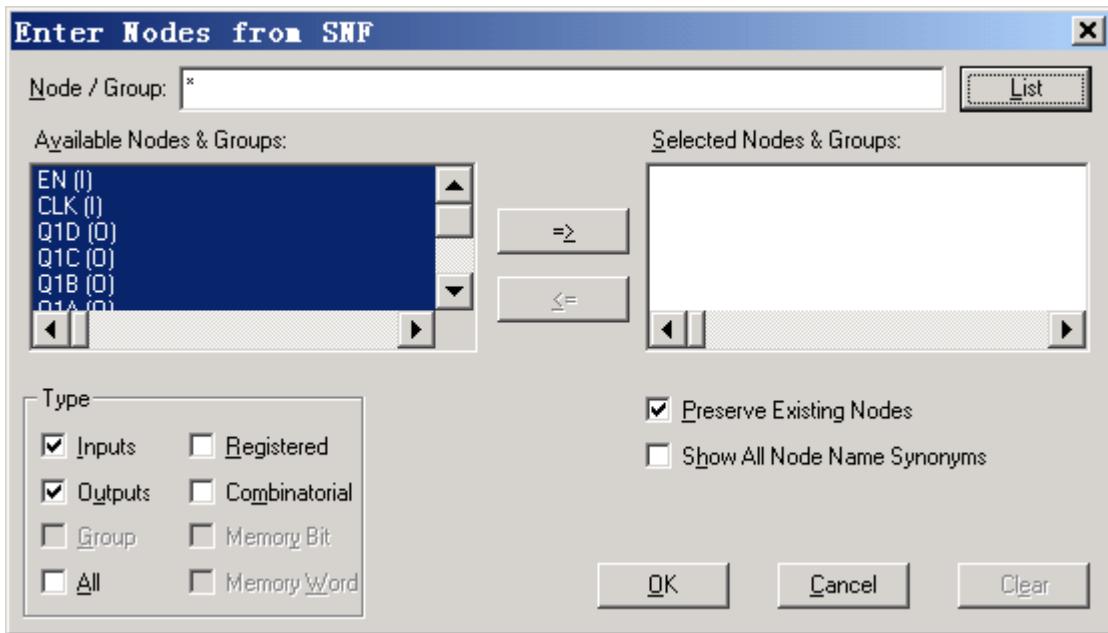

- 3、在图 3.5 中的“Type”区选择“Inputs”和“Outputs”，默认情况下已选中。单击“List”按钮，可在“Available Nodes & Groups”区看到在设计中的输入/输出信号，如图 3.6 所示，这些信号为蓝色高亮，表示被选中。单击“=>”按钮可将这些信号选择到

“ Selected Nodes & Groups ” 区，表示可对这些信号进行观测。

图 3.5 从 SNF 文件输入观测节点对话框

图 3.6 列出输入/输出信号

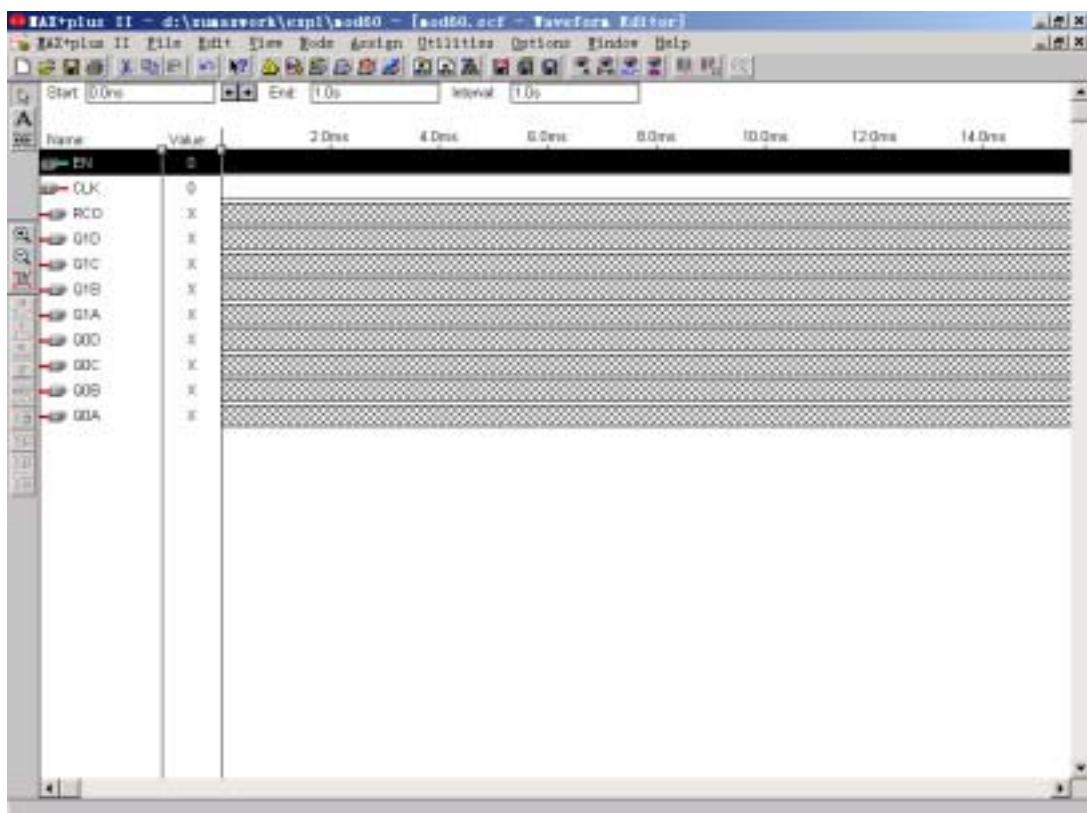

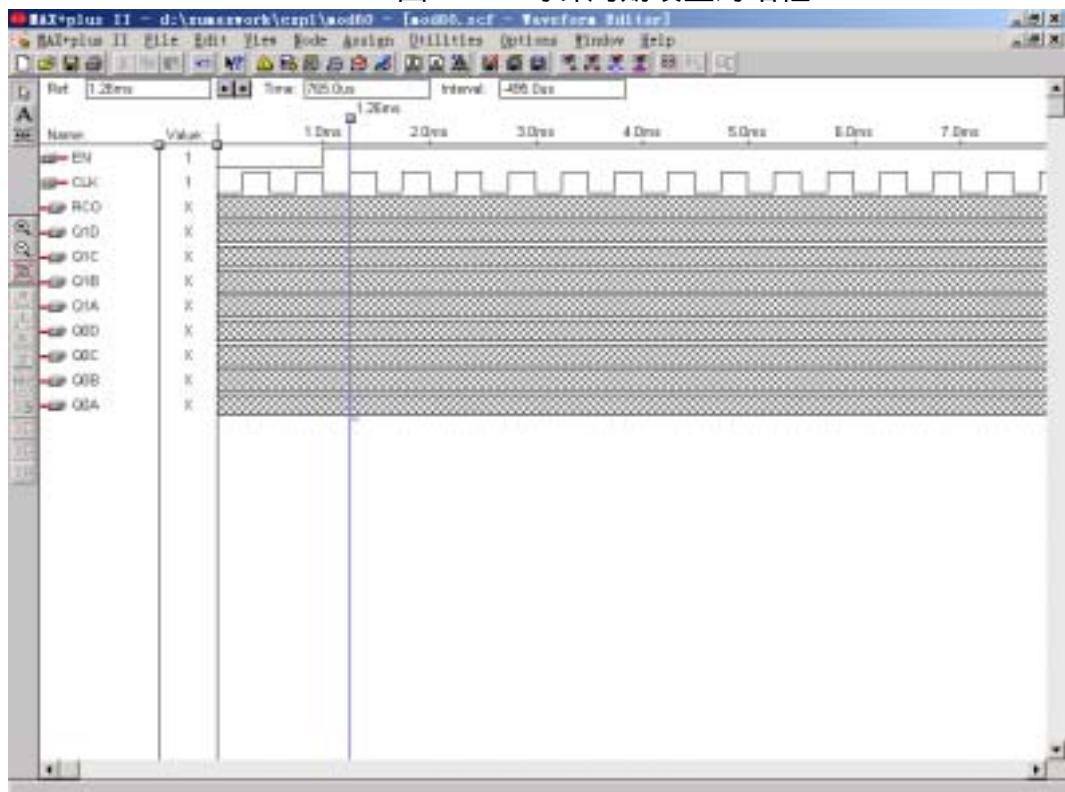

- 4、单击“OK”按钮关闭图 3.6 的对话框。可见到图 3.3 波形编辑器窗口变为图 3.7 所示。

- 5、从菜单“File”中选择“Save”，将此波形文件保存为默认名：“MOD60.scf”，扩展名“.scf”表示模拟通道文件。

图 3.7 波形文件中的输入输出信号

## 二、输入节点波形，即为输入信号建立输入激励波形：

在波形文件中添加好输入/输出信号后，就可开始为输入信号建立输入激励波形。在建立输入波形之前，先浏览一下与此操作相关的菜单选项及工具条。

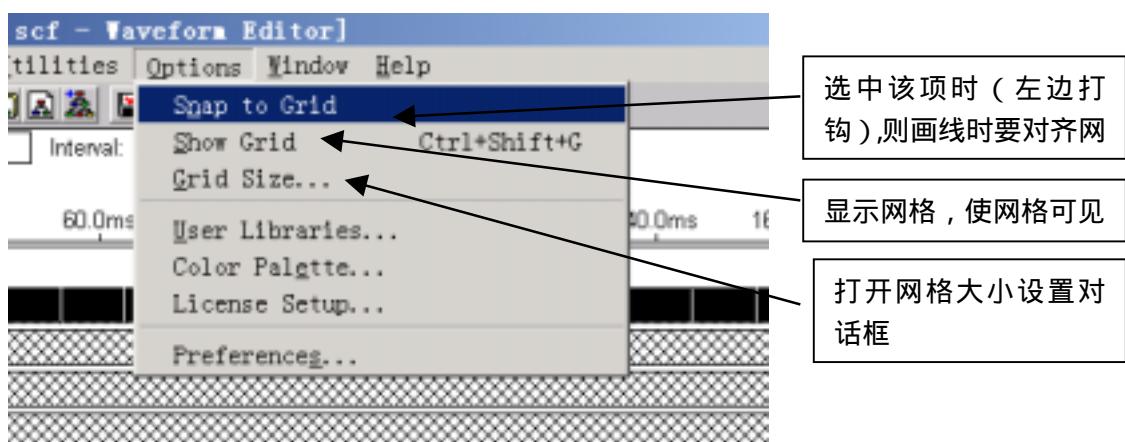

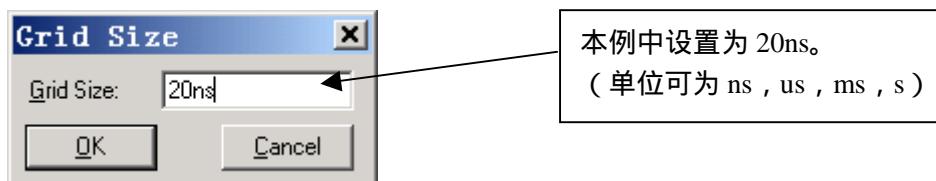

图 3.8 绘图网格设置菜单条

图 3.9 网格大小设置对话框

此外，在默认情况下，模拟时间为 1us。可从菜单“File”下选择“End Time...”来设置模拟时间的长短，在本例中设置为“1s”。

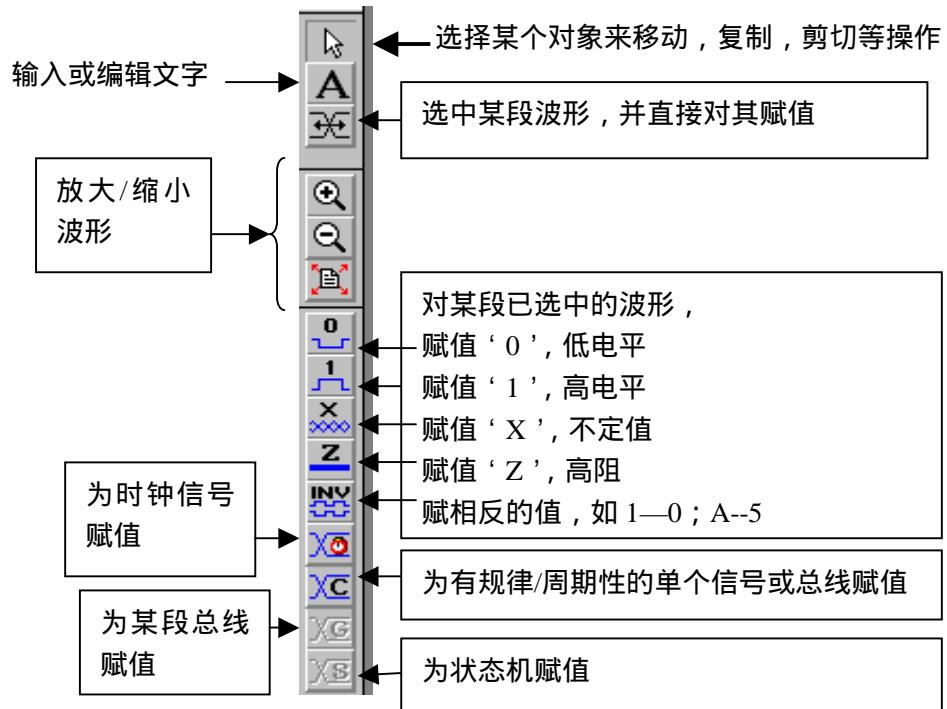

图 3.10 为绘制波形图用的工具条。

图 3.10 波形图绘制用工具条说明

以本设计为例：

1、将信号“EN”从头至尾，即从 0s 到 1s 赋值‘1’：

- 选中信号“EN”，即用鼠标左键单击“Name”区的“EN”，可看到“EN”信号全部变为黑色，表示被选中；

- 用鼠标左键单击 ，即可将“EN”赋‘1’。

- 观察“EN”的作用，采用同样方法可将信号“EN”从 0ns 到 1s 赋值‘1’，在 0ns 至 1ms 之间将其赋‘0’（因为该信号高电平有效）；

- 鼠标移到“EN”信号的 0ns 处按下鼠标左键并向右拖动鼠标至 1ms 处，松开鼠标左键。可看到这段区域呈黑色，被选中；

- 鼠标左键单击工具条 中即可。

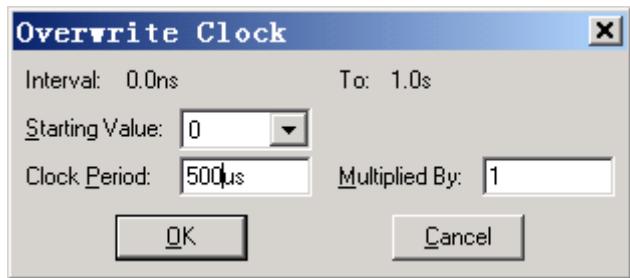

2、为时钟信号“CLK”赋周期为 500us 的时钟信号：

- 打开“Options”菜单，选中“Snap to Grid”菜单项，使其前面不打钩，即画线时不需要对齐网格；

- 选中信号“CLK”；

- 设置信号周期。鼠标左键单击工具 条中就可以打开如图 3.11 所示的对话框，输入所需的时钟周期。（若未在步骤 a 中正确设定“Snap to Grid”菜单项，该对话框中的“Clock Period”栏为灰色，无法输入所需的时钟频率）；

- 单击“OK”关闭此对话框即可生成所需时钟。

- 选择“File”中“Save”存盘。到此完成波形输入，得到图 3.12。

图 3.11 时钟周期设置对话框

图 3.12 建好的输入波形图

### 3、运行模拟器，进行时序模拟

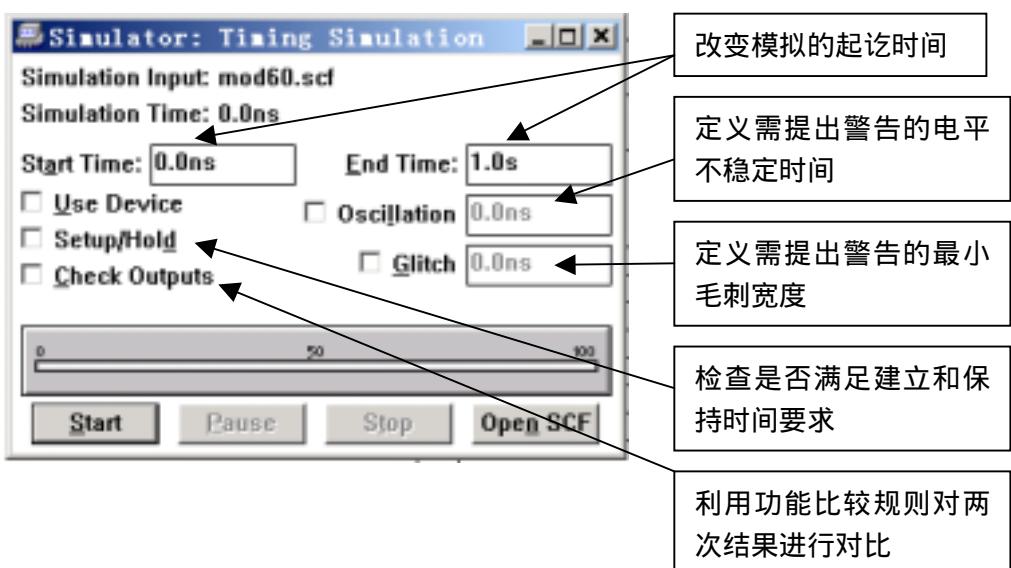

图 3.13 模拟器

东南大学电工电子实验中心 作者：徐莹隽

- a、菜单“MAX+PLUS II”中选择“Simulator”，即可打开如图3.13所示模拟器

- b、单击按钮“Start”即可开始模拟；

- c、模拟完毕后，单击按钮“Open SCF”可打开刚才编辑的波形文件，就可开始对模拟结果进行检查。

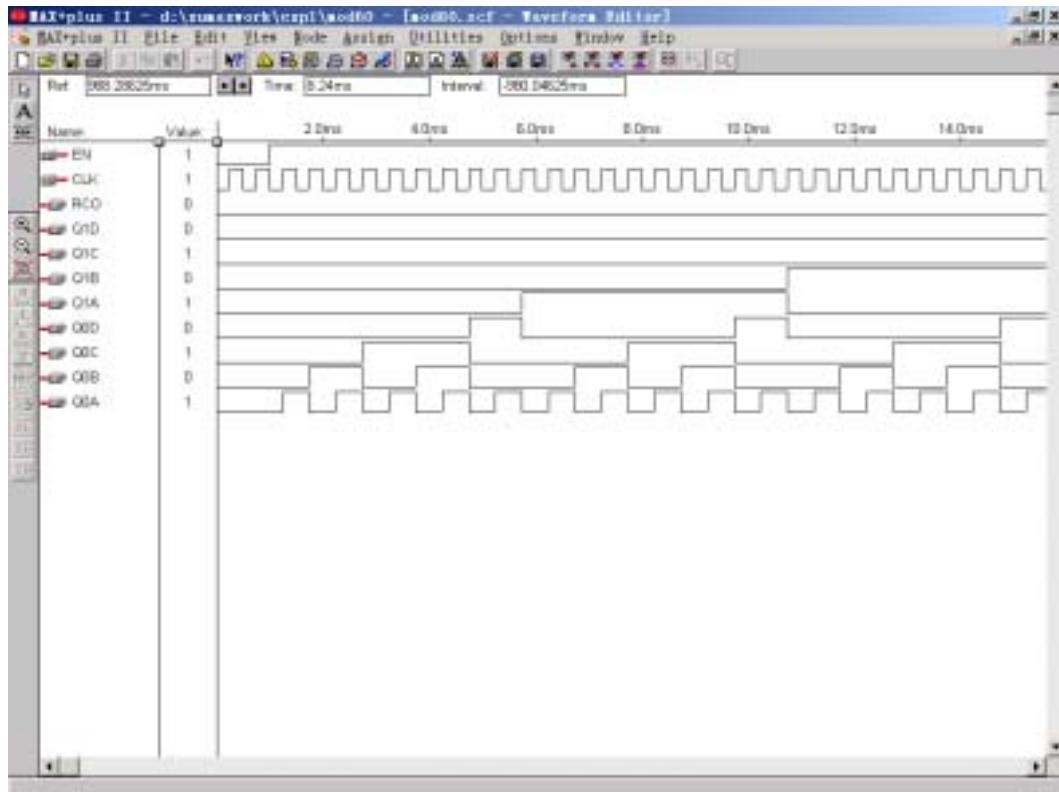

模拟完成后波形模拟文件如图 3.14 所示：

图 3.14 模拟结果

- 4、为观测方便，可将计数输出 Q1D、Q1C、Q1B、Q1A 和 Q0D、Q0C、Q0B、Q0A 分别组成组来观测。步骤如下：

- a. 将鼠标移到“Name”区的 Q1D 上，按下鼠标左键并往下拖动鼠标至 Q1A 处，松开鼠标左键，可选中信号 Q1D、Q1C、Q1B、Q1A；

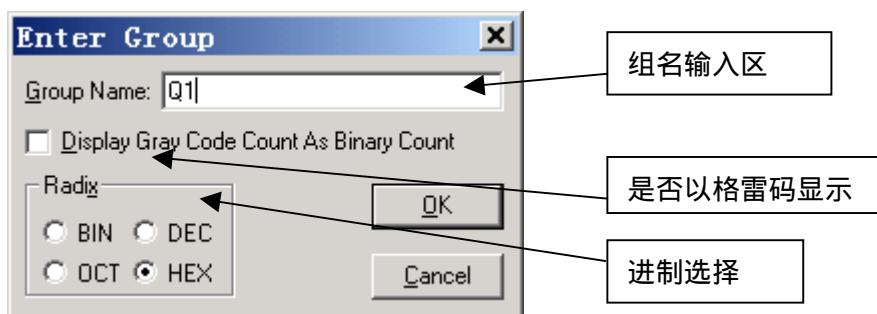

- b. 在选中区（黑色）上单击鼠标右键，打开一个浮动菜单，选择“Enter Group”项，出现图 3.15 所示的对话框；

图 3.15 设置组的对话框

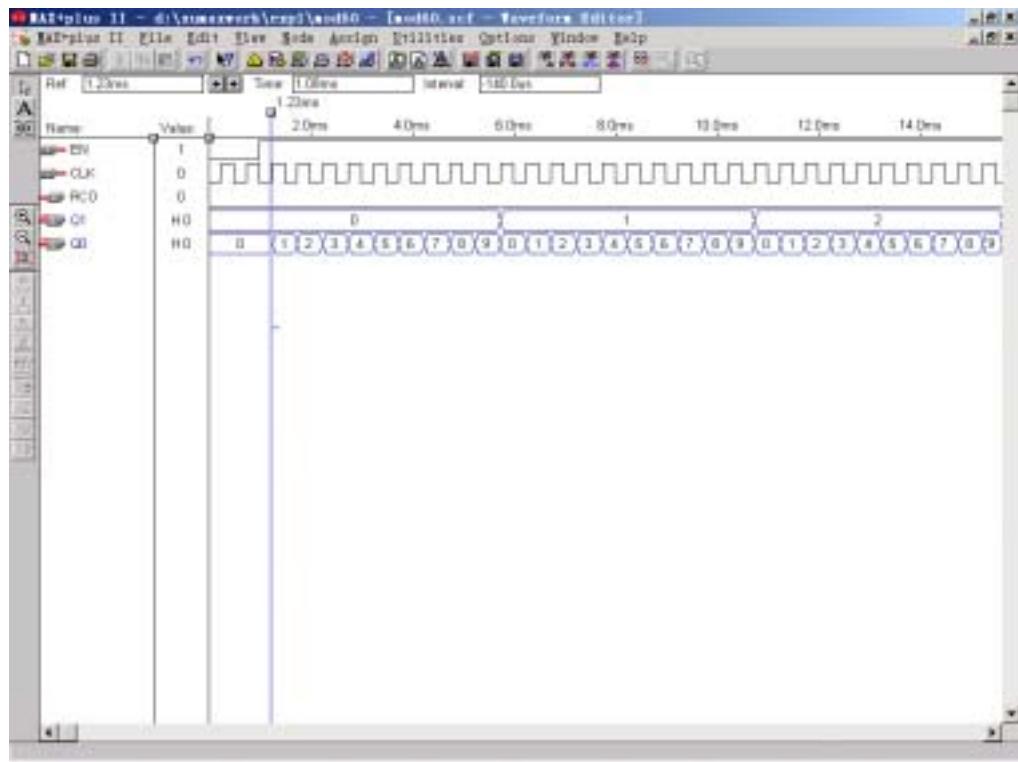

- c. 选择“OK”关闭此对话框，重复以上过程将 Q0D、Q0C、Q0B、Q0A 组成 Q0 组。所的波形图如图 3.16 所示。

图 3.16 模拟结果 (以组方式显示)

### 3.3 层次化设计方法进行项目顶层设计

数字系统设计的一般方法是采用自顶向下的层次化设计。在 Max+plusII 中，可利用层次化设计方法来实现自顶向下的设计。一般在电路的具体实现时先组建低层设计，然后设计顶层。下面以前面设计的模 60 计数器为基本模块建立一个分，秒的时钟，看一下层次设计的过程。

#### 一、底层模块符号的建立和修改

- 1、在 3.2 节的 MOD60 计数器的设计以后，在图形编辑器窗口下，执行菜单“File”下“Create Default Symbol”，可生成符号“MOD60”。这就将我们自己设计的模为 60 的计数器编译成库中的一个元件；

- 2、在图形编辑器窗口下，执行菜单“File”下“Edit Symbol”，打开符号编辑器窗口，可以看到我们新建符号“MOD60”的外观如图 3.17 所示

- 3、和图形编辑器类似，在符号编辑器里，我们可以通过画图工具对符号进行一些必要的修改，以满足我们的需要。

#### 二、建立顶层设计文件

- 1、建立一个新的图形文件，保存为“clock.gdf”；

- 2、将其指定为项目文件（菜单“File”下“Project/Set project to Current File”项）；

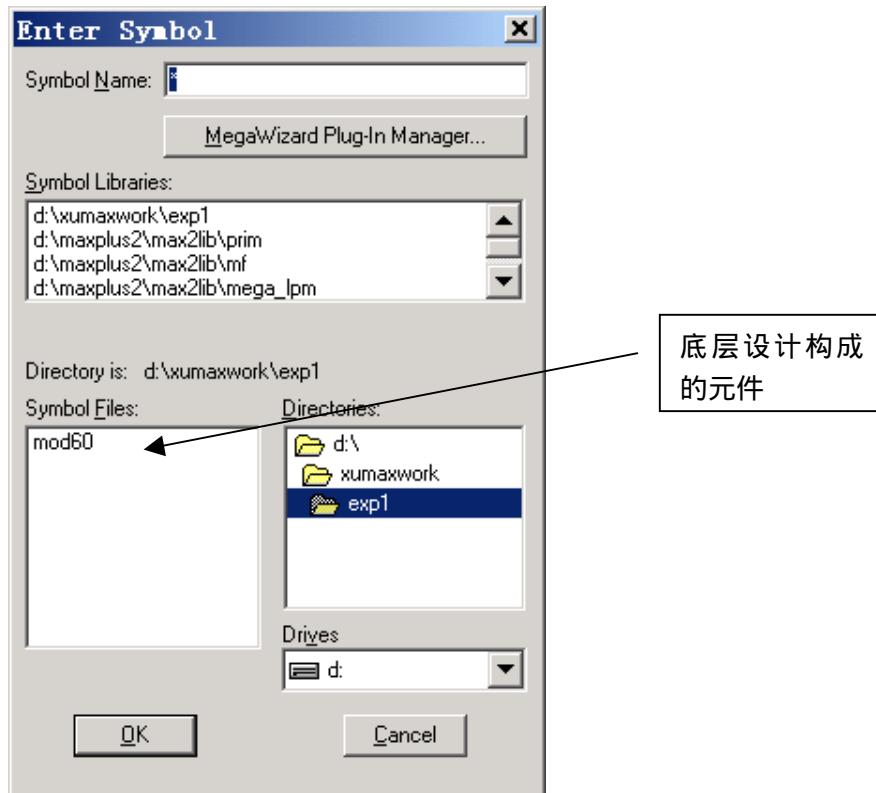

- 3、在“clock.gdf”的图形编辑区空白处，双击鼠标左键可打开“Enter symbol”对话框来选择需要输入的元件，此时看到它与以前我们看到的“Enter symbol”对话框稍有

不同：在元件列表区可看到我们刚才生成的元件 MOD60，如图 3.18 所示：

图 3.17 符号“MOD60”

图 3.18 元件输入对话框

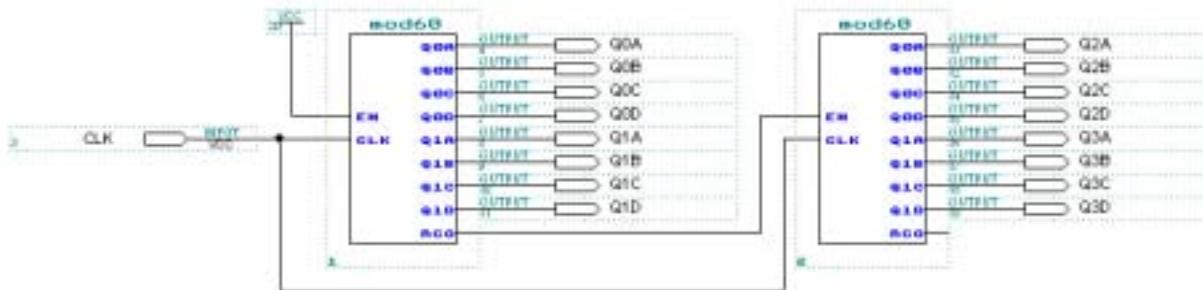

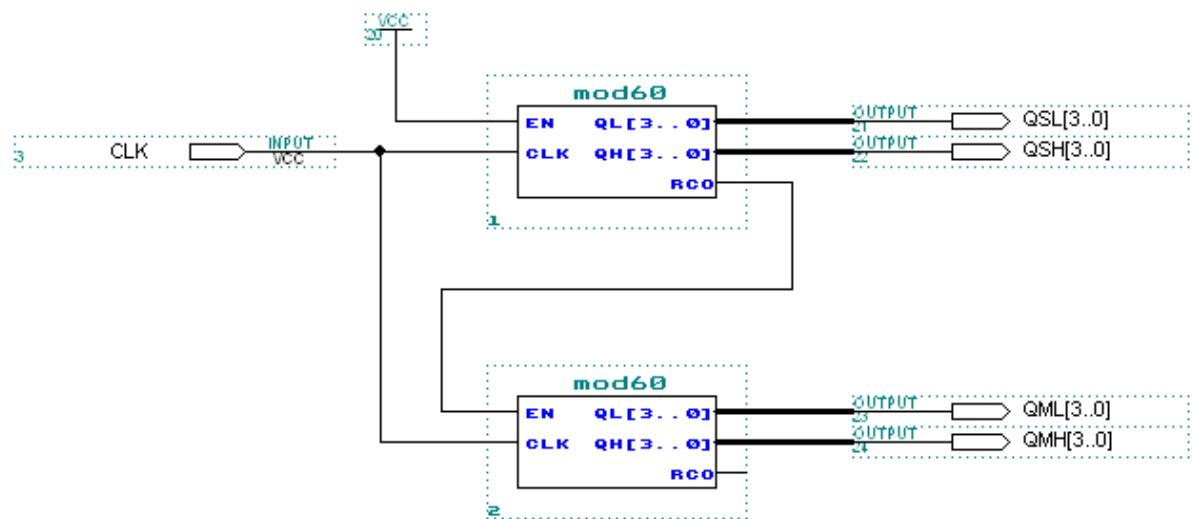

- 4、调入 MOD60 两次，经适当连接构成顶层设计文件，如图 3.19 所示。在图 3.19 中，双击元件 MOD60，可打开低层设计文件“MOD60.gdf”。

- 5、对顶层设计文件“clock.gdf”构成的项目“clock”进行编译、仿真，完成设计。

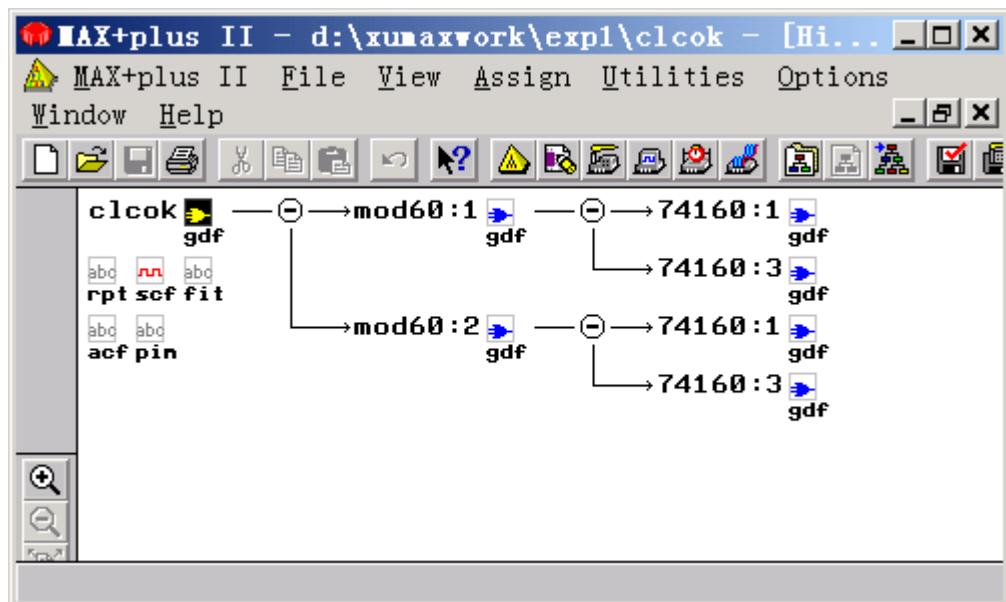

### 三、利用层次显示功能管理设计项目

层次显示方式就是以一个层次树的形式显示整个项目和电路的设计文件。通过工具条中  或菜单“Max+plusII”下“Hierarchy Display”菜单项就可以打开层次显示窗口

如图 3.20 所示。从该窗口中显示了我们刚才设计的数字钟项目的所有层次，其中最顶层的设计文件“clock.gdf”调用了两个 MOD60，而每个 MOD60 又各自调用了两个 74160。在图 3.19 中，双击任何文件名或小图标，可打开相应文件。其中“rpt”文件，即“clock.rpt”文件，从此文件可获得关于设计的管脚的锁定信息、逻辑单元内连情况、资源消耗及设计

方程等其他信息。

图 3.19 clock.gdf 文件

图 3.20 项目 clock 的层次结构

### 3.4 利用 BUS 方式提高设计效率

在图 3.19 的数字钟设计文件中分，秒的输出信号共有 16 个，绘图时很不方便。Max+Plus II 提供了 BUS (总线) 功能来简化设计过程。BUS 是指多个信号线的组合，采用 BUS 可使设计清楚易读，并且可减轻设计中重复连线的负担，此外，利用 BUS 可方便地在波形窗口中观测仿真结果。还是以数字钟为例，看一下 BUS 总线的使用

过程。

首先回到低层设计文件“MOD60.gdf”，对设计文件进行以下修改：

- 1、将图中输出 (output) 元件 Q1D、Q1C、Q1B、Q1A 和 Q0D、Q0C、Q0B、Q0A 全部删除，但保留从元件 74160 的 QA、QC、QB、QA 管脚引出的连线。单击从第一个 74160 的 QA 引出的连线，此时连线变成红色，并有闪烁的黑点，此时输入文字“QL0”。这就将该连线命名为“QL0”，在同一设计文件中，名字相同的连线代表它们在电气上是相通的。用同样的方法将第一个 74160 的 QB、QC、QD 引出的连线分别命名为 QL1、QL2、QL3，将第二个 74160 的 QA、QB、QC、QD 引出的连线分别命名为 QH0、QH1、QH2、QH3。

- 2、添加两个输出 (output) 元件，分别命名为 QL[3..0] 和 QH[3..0]，其中 QL[3..0] 代表 QL3、QL2、QL1、QL0 四线的组合。然后从 Output 元件分别引出一根连线，但连线并不和任何其它元件相连。右键单击该连线，在弹出的右键菜单的 Line Style 中选择粗线，粗线表示该线是总线。和单线一样也可以对总线进行命名，名字相同的总线在电气上是相通的，在本例中如果要对该总线命名，名字必须和所连的 Output 元件名字相同。对另一根连线作同样处理。修改完的设计文件如图 3.21 所示。

图 3.21 修改后的模 60 计数器原理图

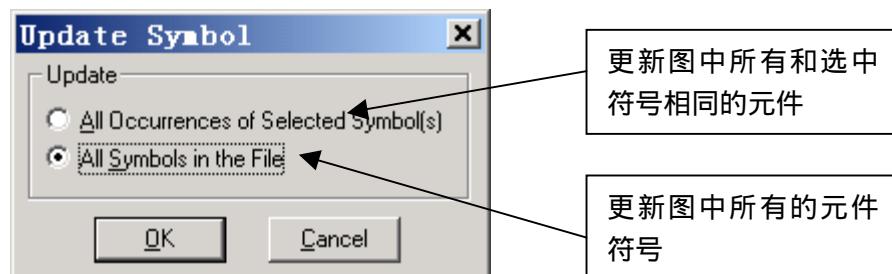

- 3、重新将“MOD60”生成符号，替换掉原来的符号。回到顶层设计文件“clock.gdf”中，执行 Symbol 菜单下的 Update Symbol 菜单项，出现如图 3.22 所示对话框

选择第二项，更新所有符号，删除多余的元件，整理连线并重命名，得到修改完的“Clock.gdf”设计文件如图 3.23 所示。

图 3.22 元件符号更新对话框

图 3.23 修改后的“Clock.gdf”设计文件