# MC9S12NE64 单片机 以太网接口的 FPGA 设计※

■ 沈阳理工大学 张嘉春 李斌 王婧

靖文 宋开鑫 孙新立

摘要 介绍一种以 FPGA 为核心,以 MC9S12NE64 单片机为以太网控制器的以太网接口设计;给出接口的软硬件设计。将 FPGA 与单片机相结合,避免了传统的以单片机为核心的网络接口的诸多缺点,结构简单、开发便捷,具有高速传输、高可靠性等优点。

关键词 FPGA MC9S12NE64 SOPC 以太网接口

## 引言

随着电子工艺的发展,电子器件的发展趋势是:体积越来越小,集成度越来越高,功能越来越强。FPGA 即是一种随之发展而来的新兴的可编程逻辑器件,与其他的 PLD 相比具有更高的集成度、更快的工作速度和更大的编程灵活性。MC9S12NE64 是一种集成了 EMAC 和 EPHY 的 16 位单片机,较以往的以太网控制器(如 RTL8019AS、DM9000A、LAN91C111 等),MC9S12NE64 既具有以太网控制器的功能又兼具单片机的特点——体积小、可靠性高,外围电路少,设计大大简化,占板空间少,系统开发成本低等。

## 1 硬件设计

## 1.1 原理简介

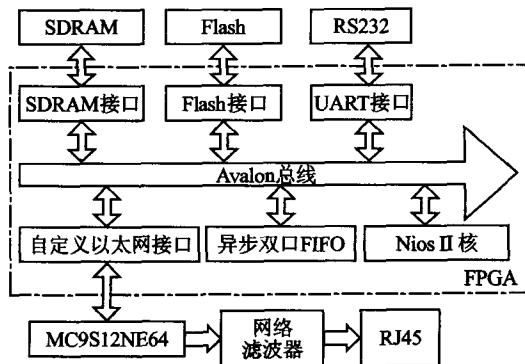

以太网接口的硬件结构框图如图 1 所示。在

图 1 以太网接口的硬件结构框图

IEEE802.3 协议中,MAC 作为一个子层,用于实现数据帧的封装、解封、发送和接收的功能;MII 是连接数据链路层和物理层的接口,同时具有数据管理的功能。在 FPGA 的内核中,自定义一个用于与 MC9S12NE64 相连接的接口,接口采用总线方式,通过异步双口 FIFO,将 PHY 传来的信号 COL、CRS 提供给 MAC 子层,用于载波监听和冲突检测,在 FIFO 内部解决时钟同步的问题以实现数据的正确传输。

## 1.2 主要电路模块

### (1) FPGA

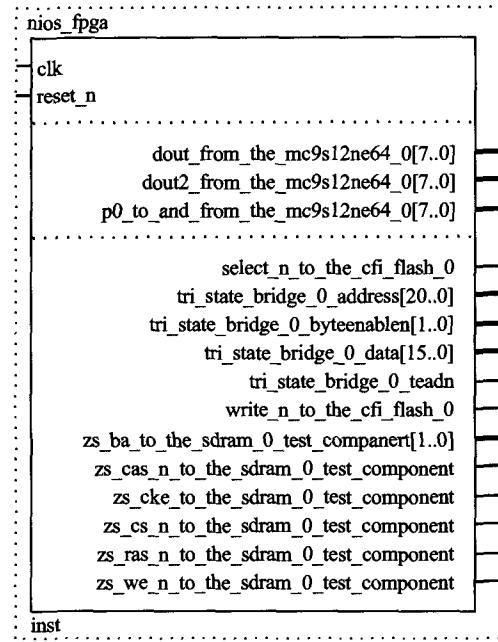

FPGA 选用的是 Altera 公司的 Cyclone II Ep2c8Q208c8，具有 8 256 个逻辑单元(LE)，可方便地实现用户自定义的功能。FPGA 相当于一个空白的芯片，用户可根据实际需要自行定义其内核，方法是在 Quartus II 界面下新建一个工程。打开 SOPC Builder 向系统内部加入 Nios II 核和用户所需外设接口，如 SDRAM、Flash、UART 等。这些接口通过 Avalon 总线实现 Nios II 处理器与外部器件的连接<sup>[1]</sup>。由于 SOPC Builder 中没有提供 MC9S12NE64 的接口模块，所以需要自行开发组件，即在 QuartusII 中用 Verilog 语言编写 MC9S12NE64 的接口程序，通过 SOPC Builder 下的 CREATE NEW COMPONENT 加入接口程序，即可实现 FPGA 内部核心配置<sup>[2]</sup>。FPGA 的内核模块如图 2 所示。

图 2 FPGA 的内核模块

#### (2) MC9S12NE64

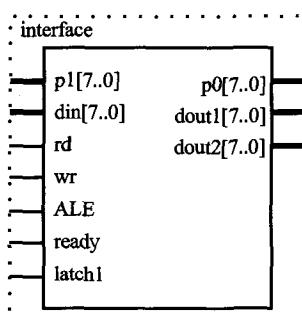

MC9S12NE64 是 16 位的单片机, 内部有 1 个高性能的 25 MHz HCS12 内核, 64 K 内存, 内部集成了以太网的 MAC 和 PHY, 具有 10/100 Mbps 特性, 内置标准的媒介独立接口(MII), 可以实现地址识别及数据管理的功能; 8 KB 的 EMAC 缓冲区, 包括 1 个发送缓冲区和 2 个接收缓冲区, MC9S12NE64 的 RAM 以 2 倍于 CPU 的速度和 CPU 交换数据, 使得 CPU 和 EMAC 缓冲区可以交换存取数据; 遵循 IEEE802.3 协议, 支持半双工和全双工通信。MC9S12NE64 最小系统由 MC9S12NE64 单片机、25 MHz 晶振及复位电路组成。通过外接 RJ45 实现系统与网络的连接。MC9S12NE64 与 FPGA 通信接口的逻辑框图如图 3 所示。

各引脚功能如下:

**wr** 输入信号, 为 FPGA 的写信号, 与 MC9S12NE64 的写端口相连;

**rd** 输入读控制信号;

**ready** 输入信号, 数据就绪标志;

**ALE** 输入信号, 与 MC9S12NE64 的 ALE 信号相连, 用于 FPGA 片内锁存地址, 配合 wr 信号进行 MC9S12NE64 与 FPGA 的通信;

图 3 MC9S12NE64 与 FPGA 通信接口逻辑框图

**p0** 双向信号, 用于地址和数据的传送;

**p1** 输入地址信号;

**dout1, dout2** 锁存输出信号;

**din** 输入信号, 来自 MC9S12NE64 数据总线;

**latch** 读数据锁存信号。

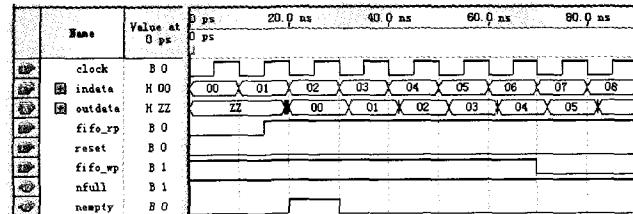

#### (3) 异步双口 FIFO

为了满足时钟不同步的要求, 需要 FIFO 具有异步的读、写时钟。当冲突检测信号 COL 为高时, 要求发送帧执行退回操作, 回至 FIFO 中等待下一个 Transmitting 信号。FIFO 的设计如下: 设置异步 Reset, 高电平触发; 设置 8 位寄存器 fifodata, 保存 FIFO 的数据; 设置 fifo\_rp 和 fifo\_wp 为读、写指针, cr\_rp 和 cr\_wr 为进位标志, fifo\_rp 和 fifo\_wp 为 FIFO\_DEPTH - 1 时取反; 设置 nempty、nfull、near\_empty、near\_full 为数据空、满指示。测试时, 暂定容量 FIFO\_DEPTH 为 32 字节(实际要求至少一个帧的大小, 即 1530 字节), 读、写时钟分别为 50 MHz 和 25 MHz, 时序仿真波形如图 4 所示, FIFO 能够成功读写。

图 4 时序仿真波形

#### (4) 通信电路

为了实现系统与 PC 机的通信, 以便上位机管理, 将 FPGA 内部接口 UART 外接 MAX232 接口电路, 通过 RS232 实现与 PC 机之间的数据通信。

## 2 软件设计

本设计采用自顶向下的设计方法, 将系统分为几个独立的模块, 模块之间相互独立有利于软件的修改和调试, 应用 Nios II IDE 完成程序的编译。网络接口通过本地 DMA 和远端 DMA 来完成数据的收发。所谓“本地 DMA”可以理解为 MC9S12NE64 内部数据传输, 而“远端 DMA”是指 MC9S12NE64 与 FPGA 之间的数据传输。

#### (1) 初始化

初始化程序主要包括设置寄存器和操作数据端口, 设置数据总线宽度、中断服务类型以及设置接收和发送数据缓存区的大小等。

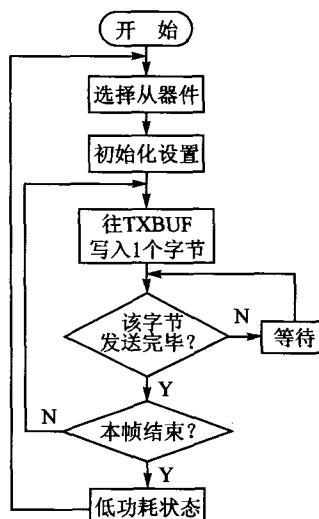

#### (2) 发送数据

MC9S12NE64 作为一个集成以太网接口的单片机, 数据的发送校验、碰撞检测由芯片自己完成。这里

MSP430F449 的 SPI 通信主要软件流程如图 3 所示。

在实验中发现, SPI 通信作为芯片级的通信, 在较好的电磁环境中一般不会发生数据的传输错误, 误码率极低; 但是为了使命令和数据的发送更为准确, 在某些场合 UCLK 引脚可拉高, 以保证通信自始至终 UCLK 引脚无意外的脉冲引入, 可有效避免因异常时钟信号引起误码。在软件中设置合理的波特率和数据帧格式, 也可极大提高数据传输的准确性。

RS-485 通信的帧格式如下:

| 帧标志  | 源地址  | 目标地址 | 控制命令 | 数据长度 | 数据      | CRC 校验码 |

|------|------|------|------|------|---------|---------|

| 1 字节 | 1 字节 | 1 字节 | 2 字节 | 1 字节 | 由长度字节决定 | 2 字节    |

**源地址:** 发送该帧数据的单片机地址。

**目标地址:** 接收该帧数据的单片机地址。

**数据长度:** 数据帧中, 该数据帧携带的数据个数, 不包括控制字段和校验码。

只需要配置发送数据的物理地址、源地址、目的地址、数据类型及发送数据即可。数据的发送由两步完成: 首先, 把内存中的数据传入 MC9S12NE64 的发送缓冲区; 然后设置寄存器启动本地 DMA 将数据送入 FIFO 发送出去。

### (3) 接收数据

在初始化程序中已经分配好了接收缓冲区的位置, 并且配置好了中断的模式。当有一个正确的数据包到来时, 控制器发出中断请求, 中断申请响应后, 进入中断服务程序并开始接收数据。在查询方式下, 通过查询 CURR 和 BNRY 两个寄存器的值来判断是否收到 1 帧数据。当 BNRY +1 与 CURR 不等时, 说明接收缓冲区接收到新的数据帧。若收到新数据帧, 则先读取前 2 个字的数据, 这 2 个字的数据代表此次传输的数据帧的基本状态: 第 1 个字的低字节表示接收状态, 第 1 个字的高字节为下一个包的开始地址指针, 第 2 个字节为本数据包的长度(以字节为单位计算)。本课题采用中断和查询组合的方式接收数据包。

## 结语

将 MC9S12NE64 以总线方式与 FPGA 进行通信具有

图 3 MSP430F449 的 SPI 通信流程

**校验码:** 采用的是 CCITT 的 CRC 校验方法, 对整个帧(除校验码本身)进行校验, 生成多项式为  $G(X) = x^{16} + x^{15} + x^2 + 1$ 。

## 3 实际应用与小结

在基于 MSP430 系列单片机的采集系统中, MSP430F449 作为主机, 负责数据的存储、键盘控制、液晶显示和远程通信等功能; MSP430F149 作为从机, 进行数据的采集与分析。二者通过三线主从式的 SPI 通信进行命令发布与数据交流, 硬件电路简单, 通信快速、准确, 效果良好, 可满足工程需要。■

## 参考文献

- [1] 魏小龙. MSP430 系列单片机接口技术及系统设计实例 [M]. 北京: 北京航空航天大学出版社, 2002.

- [2] 李桐宇, 杨家玮. 用 SPI 总线实现 DSP 和 MCU 之间的高速通信 [J]. 电子元器件应用, 2006, 8(11): 28~30.

- [3] 胡大可. MSP430 系列单片机 C 语言程序设计与开发 [M]. 北京: 北京航空航天大学出版社, 2003.

李福俊(硕士), 主要研究方向为单片机控制与信号处理; 姜学东(副教授), 主要研究方向为高频高压电源和工业控制。

(收稿日期: 2007-05-08)

以下优点: 速度快, 其通信工作时序是纯硬件行为; 节省 FPGA 的 I/O 口线; 相对于非总线方式, 编程简单控制可靠; 在 FPGA 中通过逻辑切换 MC9S12NE64 易于与 SDRAM 或 ROM 接口。该设计增强了系统的灵活性, 实现了高速的以太网数据传输, 具有广阔的应用前景。

编者注: 自定义接口源代码见本刊网站 [www.mesnet.com.cn](http://www.mesnet.com.cn)。■

## 参考文献

- [1] 徐光辉, 黄如. 基于 FPGA 的嵌入式开发与应用 [M]. 北京: 电子工业出版社, 2006.

- [2] 任爱峰. 基于 FPGA 的嵌入式系统设计 [M]. 西安: 西安电子科技大学出版社, 2004.

- [3] 彭澄廉. 挑战 SOC——基于 NIOS 的 SOPC 设计与实践 [M]. 北京: 清华大学出版社, 2004.

- [4] 江国强. SOPC 技术与应用 [M]. 北京: 机械工业出版社, 2006.

张嘉春, 主要研究方向为宽带综合数据光同步网节点计算机接口设计。

(收修改稿日期: 2007-05-17)