# 基于微机的边界扫描测试主控系统的设计

张 华 陈朝阳 沈绪榜

( 华中科技大学图像识别与人工智能研究所

图像信息处理与智能控制教育部重点开放实验室 )

**摘要:**分析了边界扫描测试技术的工作机制对测试主控系统的功能需求,提出了一种基于微机 PCI 总线的低成本边界扫描测试主控系统的硬件设计方案。该系统以 PC 机为平台,以用 CPLD 器件实现的 JTAG 主控器生成满足 IEEE1149.1 协议的边界扫描测试信号,并用普通的 SRAM 实现存储器共享。仿真表明,该系统产生的测试信号完全满足 IEEE1149.1 协议的时序要求,可用于 IC 或 PCB 的边界扫描测试,以及进行边界扫描测试的研究和实验。

**关 键 词:**边界扫描测试; JTAG 主控器; 集成电路测试; PCI; CPLD

中图分类号: TN407 文献标识码: A 文章编号: 1671-451X(2002)05-0022-03

边界扫描测试(BST-Boundary Scan Test)技术是一种可测性设计技术,其基本思想是在集成电路的边界(引脚)上增加附加的串行扫描单元,从而实现器件引脚状态的完全可控和完全可观测。与之相应的工业标准为 IEEE1149.1 系列标准。该技术为芯片的集成度提高带来的芯片和电路板的测试难题提供了一种有效且低成本的解决方法<sup>[1]</sup>。从 JTAC(Joint Test Action Group)提出该技术至今的十几年中,边界扫描测试技术在国外已得到了一些应用,并将有广阔的应用前景<sup>[2]</sup>。国内目前对边界扫描测试技术中的受控器设计和互连测试的研究已取得了一些成果。但目前国内尚没有使用方便且价格较低的边界扫描测试仪器,这直接影响了国内对该技术的研究和应用。本研究在分析边界扫描测试受控系统工作机制的基础上提出一种基于 PC 机的边界扫描测试主控系统的设计方案和实现电路。设计仿真结果和用逻辑分析仪观察结果表明,该系统所产生的测试信号完全符合 IEEE1149.1 协议的要求。由于本系统是以微机为平台的,因此可以充分利用微机的资源优势。通过相应的软件设计,本系统可以用于集成芯片的功能测试和印制电路板的互连测试及电路故障诊断,也适用于进行边界扫描测试的研究和实验。

## 1 功能需求

IEEE1149.1 标准规定的边界扫描测试受控系统的体系结构包括四个测试访问端口(又称 JTAG 接口)<sup>[3]</sup>: 测试数据输入端口 TDI, 测试数据输出端口 TDO, 测试时钟 TCK, 测试方式选择 TMS。主要硬件单元为 TAP 控制器, 指令寄存器, 边界扫描寄存器及旁路寄存器。可选的有测试复位输入 TRST 及其他可选的测试数据寄存器。指令寄存器和所有测试数据寄存器的工作由 TAP 控制器产生的信号来控制。TAP 控制器是一个时序电路, 由 TMS 和 TCK 信号驱动。TAP 控制器共有 16 种状态, 其状态转换满足 IEEE1149.1 标准定义的状态要求。TAP 控制器的这些状态提供了边界扫描测试所需的全部过程, 其中包括:

a. 提供信号将指令移入指令寄存器中;

b. 提供信号将测试数据移入测试数据寄存器中(经 TDI), 并把测试响应数据从这些寄存器移出(经 TDO);

c. 提供信号完成测试操作, 如捕获、移位、更新测试数据等。

根据受控系统的 TAP 控制器状态图<sup>[3]</sup>, 边界扫描测试的基本过程为: 测试主控系统产生满足 IEEE1149.1 协议的测试信号, 将测试数据以串行方式由受控系统的 TDI 输入边界扫描寄存器, 通过 TMS 发送测试控制命令, 经 TAP 控制器控制边

收稿日期: 2001-10-16。

作者简介: 张 华(1972-)男,硕士研究生,武汉,华中科技大学图像识别与人工智能研究所(430074)。

基金项目: 航天创新基金资助项目。

界扫描单元完成测试数据的加载和测试响应数据的采集。最后,测试响应数据以串行扫描方式由TDO送到测试主控系统进行分析处理。

所以,边界扫描测试主控系统的主要功能就是生成测试数据,将测试数据转变为满足IEEE1149.1协议的JTAG接口信号并送入测试目标的JTAG接口(TCK,TMS,TDI),同时接收从接口(TDO)扫出的数据。在测试过程中,可以将测试输出数据与预期输出数据进行比较,若有故障即停止测试。测试输出数据可以存于存储器中,供测试结束后进行诊断。

## 2 硬件设计

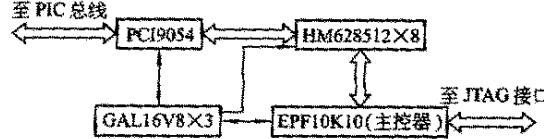

为了便于测试数据的生成和测试后的诊断工作,本系统以PC机为工作平台,设计成基于PCI总线的接口卡形式。系统电路框图如图1所示,

图1 测试主控系统电路框图

整个系统分为四个模块:PCI接口电路,存储器组,译码电路和主控器。其工作流程为:PC机软件根据被测对象和测试图形生成主控器可以执行的测试代码并通过PCI总线传送到系统的存储器组中,接收到开始测试信号后,主控器开始执行存储器组中的代码,生成满足IEEE1149.1协议的测试信号并送到JTAG接口,同时接收从JTAG接口送入的测试响应信号与预期信号进行比较,或将其存于存储器组中。若比较结果与预期响应不相符,即停止提供测试信号并向PC机申请中断。存于存储器组中的数据可以通过PCI总线读回PC机进行诊断,以查找出故障的位置及原因。

### 2.1 PCI接口电路与译码电路

PCI总线可以实现PC机与外部元件的高速数据传输。PLX公司开发的PCI9054是一种PCI接口控制芯片,符合PCI局部总线规范V2.2,其峰值传输速率为132Mbit/(32位PCI数据线)。在本系统中,PCI9054的工作频率在PCI侧为33MHz,在Local侧为10MHz。

译码电路提供测试控制信号和存储器组的访问控制及地址译码信号。测试控制信号主要包括:测试开始/停止信号、测试结束信号和测试故障信号。存储器组的访问控制信号包括PCI9054对存储器组的访问和主控器对存储器组的访问控制信

号。由于二者对存储器组的访问是分时的,因此可以将二者的访问控制信号相与(低电平有效),地址线和数据线则直接相连。

### 2.2 存储器组

存储器组用于存放测试代码和测试响应数据,由PCI9054和主控器共享访问,即对存储器组的访问包括PCI9054向存储器组写入测试代码和从存储器组读取测试响应数据,以及主控器从存储器组中读取测试代码和向存储器组写入测试响应数据。

PCI9054的本身特点和对主控器的特别设计,使普通的SRAM可以实现安全的共享,从而避免使用价格相对昂贵的双口RAM:当PCI9054不访问存储器组时,PCI9054的数据线和地址线都为悬空状态,不影响主控器对存储器组的访问;而当PCI9054要访问存储器组时,使其引脚LHOLD变为高电平,当其引脚LHOLDA相应变为高电平时,PCI9054的地址线和数据线才有效。在本主控器的设计中增加了一个HOLD输入引脚,当HOLD为高电平时,使主控器的数据线和地址线变为高阻态。这样,根据系统的运行流程,当PCI9054向存储器组写入测试代码或从其读入测试响应数据时,由于这些过程只发生在测试进行前或测试结束后,可以使主控器的HOLD引脚为高电平,主控器的数据线与地址线为高阻态,不影响PCI9054对存储器组的访问。也就是说,PCI9054和主控器对存储器组的访问采用了分时的原则,同时由于主控器的运行是由PC机通过PCI9054来控制的,所以PCI9054对存储器组的访问相对优先。

本系统中采用 $2 \times 10^6 \times 16$ bit SRAM,其中低端存储器地址用于存放测试代码,高端地址存放测试响应数据。地址分配由测试软件在编译测试代码时确定,并随测试代码的执行而得以实现。

### 2.3 主控器

主控器是本系统的核心部分,其主要功能包括:访问存储器,将测试代码转换为满足IEEE1149.1标准的边界扫描测试信号,进行数据比较等。所以,主控器实际上是一个简单的RISC微处理器。

主控器的体系结构由三部分组成:命令解释器,存储器接口和提供边界扫描测试接口信号的JTAG接口<sup>[4]</sup>。其存储器接口由16位数据线DATA[15:0]和24位地址线ADR[23:0],写信号WR,读信号RD,复位信号RESET及时钟信号CLOCK组成。命令集合包括8条命令:扫描指令SCAN,比较指令COMP,测试方式选择指令TMS,条件转移指

令 CBRANCH ,无条件转移指令 BRANCH ,存储指令 STORE ,计数指令 COUNT 及控制指令 CONTROL . JTAG 接口由 IEEE1149.1 协议中的 5 个信号 TDI ,TDO ,TMS ,TCK 与 TRST 组成 .

主控器的基本逻辑结构可由一个节拍产生器 ,一个指令译码器和八个寄存器组成 . 节拍产生器产生两个节拍 取指节拍和执行节拍 其实质就是一个有两种状态的状态机 . 指令译码器利用一个 3~8 译码器来实现 8 条指令 . 寄存器包括 : 程序计数器( 24 位 ) ,循环次数计数器( 12 位 ) ,测试

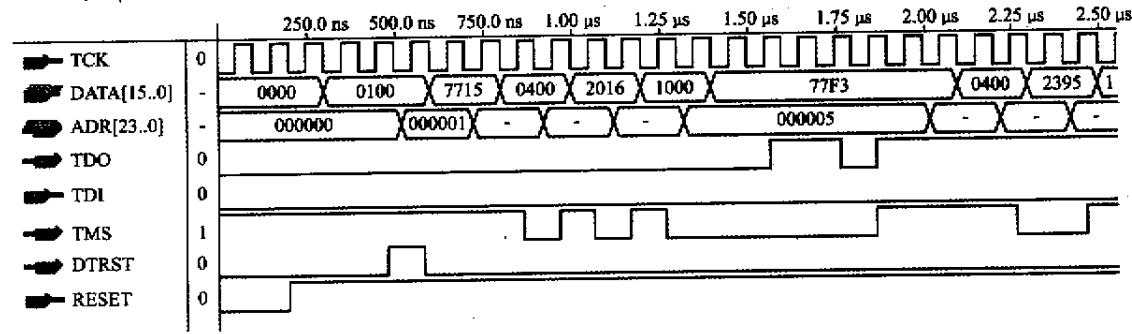

方式选择寄存器( 13 位 ),扫描输入寄存器( 12 位 ) ,结果比较寄存器( 12 位 ),扫描输出寄存器( 13 位 ),数据缓冲器( 16 位 )和地址寄存器( 24 位 ). 使用的 EDA 工具为 MAX + PLUS II ,设计输入采用原理图输入方式 ,具体的逻辑设计方法请参看参考文献 [5] . 本系统中设计的主控器所用逻辑门数不超过 5 000 门 ,占用引脚 56 个 ,利用 ALTERA 公司生产的具有 10 000 可用门、 84 引脚的 CPLD 器件 EPF10K10LC84 来实现其逻辑设计 . 编译后仿真的部分波形如图 2 所示 .

图 2 主控器仿真波形

本系统目前已完成调试 ,通过逻辑分析仪观察 ,所产生的 JTAG 接口信号波形与仿真波形吻合 ,完全满足 IEEE1149.1 协议的时序要求 .

#### 参 考 文 献

- [1] 陈光禹 ,潘中良 . 可测性设计技术 . 北京 :电子工业出版社 ,1997.

- [2] Dellecker R. Boundary-scan bursts into the modern product.

tion facility. IEEE Aerospace and Electronics Magazine , 2001 ,16(6):21~24

- [3] Test technology technical committee of the IEEE computer society. IEEE Standard Test Access Port and Boundary Scan Architecture. IEEE Std 1149. 1-1990 ,1990.

- [4] 沈绪榜 .RISC 及后编译技术 . 北京 清华大学出版社 ,1994.

- [5] 宋万杰 .CPLD 技术及其应用 . 西安 西安电子科技大学出版社 ,1999.

## A PC-based boundary-scan testing system

Zhang Hua Chen Chaoyang Shen Xubang

**Abstract :** The mechanism of boundary-scan test and the functional requirement of boundary-scan tester are analyzed , and a PCI-based boundary-scan testing system is presented. In the system , PC works as a platform , the JTAG controller used to generate the boundary-scan testing signals is realized by using CPLD chip , and normal SRAM chips is used as the shared memory. So the system is characterized by the whole function , convenience in using and low price. It can be used in the boundary-scan testing of IC and PCB , as well as in the research and experiment of the technology .

**Key words :** boundary-scan test ; JTAG controller ; IC test ; PCI ; CPLD

**Zhang Hua** Postgraduate ; Institute for Pattern Recognition & AI , Huazhong Univ. of Sci. and Tech. , Wuhan 430074 , China .